HTCC system-level package structure and package method of flip chip

A system-level packaging and packaging structure technology, which is applied in the manufacturing of electrical components, electrical solid-state devices, semiconductor/solid-state devices, etc., can solve the problems of inability to meet complex system circuit integration, damage to the atmosphere inside the sealed cavity, and affect chip reliability. , to achieve broad market application prospects, improve system integration, and protect reliability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0027] A method for preparing a flip chip HTCC system-in-package structure. The steps of the method include:

[0028] (1) To prepare the HTCC substrate 1, the length and width of the HTCC substrate 1 shall be 35-60mm, the thickness shall be 2-4mm, and the flatness of the flip chip mounting area shall not be greater than 30μm;

[0029] (2) To prepare the upper cavity enclosure frame 2 and the lower cavity enclosure frame 4, the height of the upper cavity enclosure frame 2 is 1.5-3mm, the height of the lower cavity enclosure frame 4 is 1.5-2mm; the upper cavity enclosure frame 2 and the lower cavity enclosure frame 4 have a wall thickness of 1-2mm, and the upper cavity enclosure frame 2 and the lower cavity enclosure frame 4 are made of Kovar alloy;

[0030] (3) Prepare the upper cavity cover 3 and the lower cavity cover 5, the upper cavity cover 3 and the lower cavity cover 5 are made of Kovar alloy, the upper cavity cover 3 and the lower cavity cover The thickness of the plate 5 is ...

Embodiment

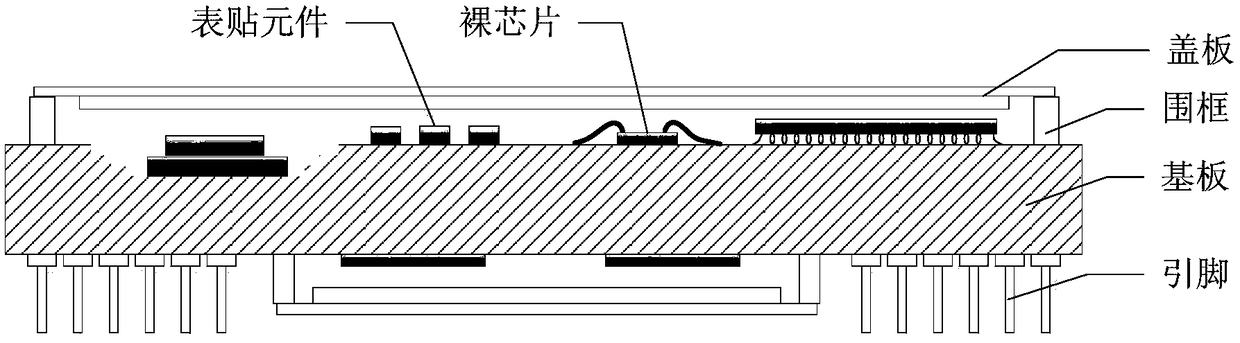

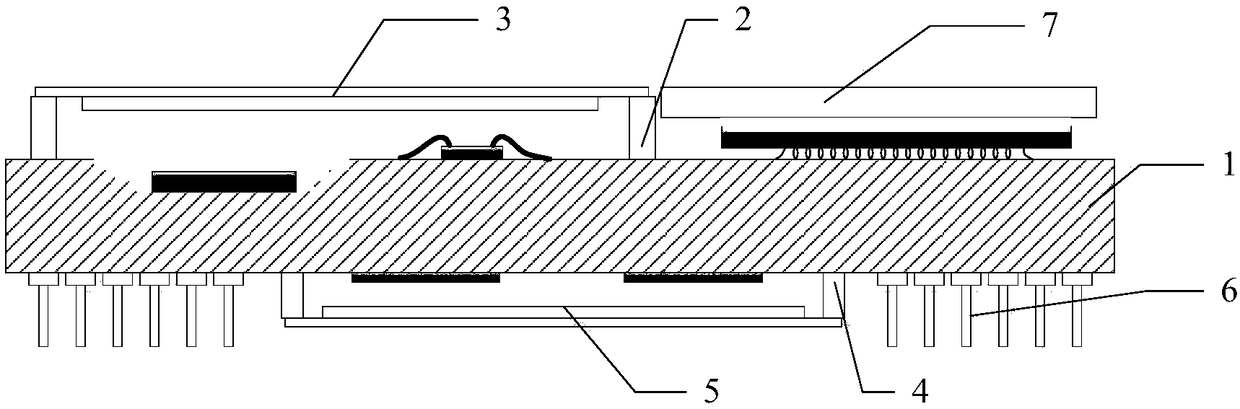

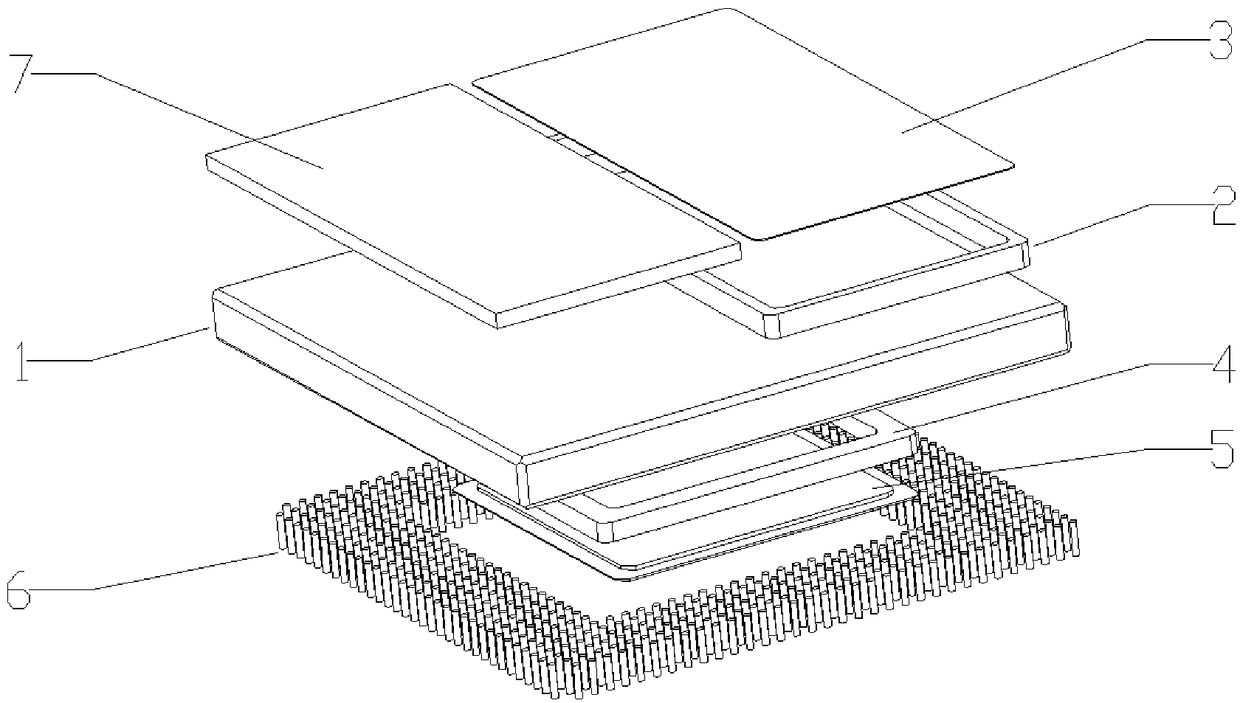

[0037] Such as figure 2 with image 3 As shown, a flip chip HTCC system-in-package structure includes an HTCC substrate 1, an upper cavity enclosure frame 2, an upper cavity cover plate 3, a lower cavity enclosure frame 4, and a lower cavity cover plate 5. CGA pin array 6 and heat sink 7;

[0038] The heat sink 7 and the upper cavity cover plate 3 are placed side by side on the upper surface of the HTCC substrate 1. Between the HTCC substrate 1 and the heat sink 7 is the mounting area for the flip-chip chip. Between the HTCC substrate 1 and the upper cavity cover plate 3 The upper cavity enclosure frame 2 is installed between the HTCC substrate 1, the upper cavity cover plate 3 and the upper cavity enclosure frame 2 to form a closed cavity; the CGA pin array 6 has a cavity in the center, and the lower cavity The cover plate 5 is installed in the central cavity of the CGA pin array 6. The CGA pin array 6 and the lower cavity cover plate 5 are located on the lower surface of the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More