CMOS transistor and manufacturing method thereof

A manufacturing method and transistor technology, applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the problems of increasing flicker noise, enhancing scattering, flicker noise interference, etc., and achieve the effect of reducing interface states and reducing dangling bonds

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

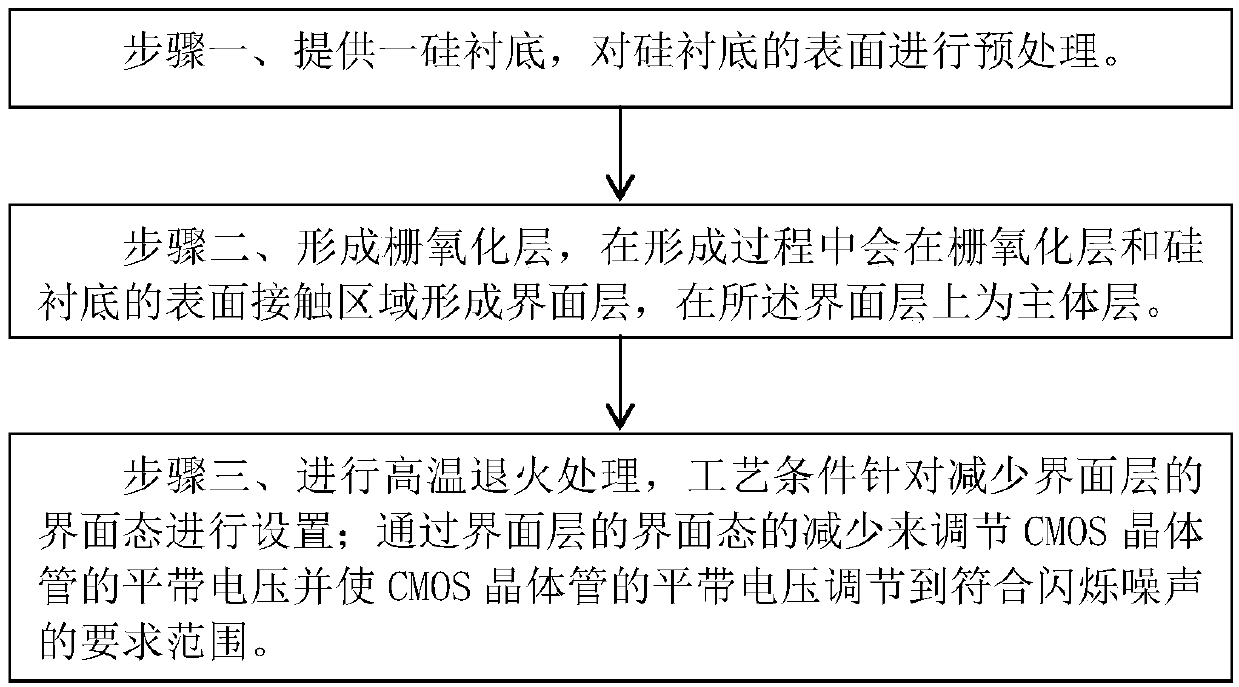

Method used

Image

Examples

Embodiment Construction

[0042] The device of the embodiment of the present invention is obtained on the basis of an in-depth analysis of the technical problems existing in the existing CMOS transistor, so before introducing the device of the embodiment of the present invention in detail, first introduce the technical problems of the existing CMOS transistor:

[0043]In the 28HP process, HKMG is usually used, but in the 28LP process, the complex HKMG is not used, and the structure of gate oxide layer plus polysilicon gate is still used. The gate oxide layer is mainly composed of SiO2, and usually includes nitrogen element, namely SiON. In the gate oxide layer of CMOS transistors, SiO 2 The interface with the silicon substrate, that is, Si, is the boundary of silicon single crystal, that is, there is an interface layer of Si-SiO2. Studies have shown that Si-SiO 2 The interface layer is not a geometric plane, but there is about thickness of. The structure of the interface layer is SiO x , where x is...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More