Manufacturing method of magnetic radom access memory unit array and peripheral circuit connecting wires

A random access memory and cell array technology, applied in the manufacture/processing of electromagnetic devices, circuits, electrical components, etc., can solve problems such as small size openings, MRAM device pollution, damage diffusion barriers, etc., to achieve complexity and production costs Effects of reduction, device electrical performance and yield improvement, and magnetic/electrical performance improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment example 1

[0063] Implementation case 1: two single damascene (SD, Single Damascene) processes, the steps are as follows:

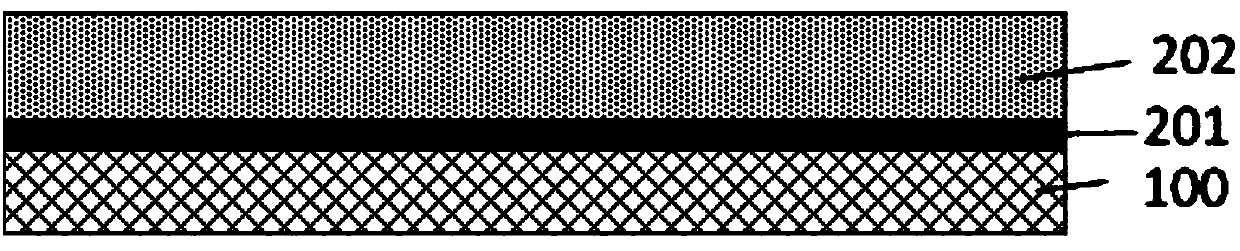

[0064] Step 3.1.1: On the magnetic tunnel junction dielectric capping layer (II) 401, deposit the top electrode via dielectric 402, and finally, use a planarization process to grind the top electrode via (TEV) dielectric 402, as shown in Figure 3(a) shown; the top electrode via (TEV) dielectric 402 is SiO 2 , SiON or low-k and other materials, the thickness of which is 120nm ~ 400nm.

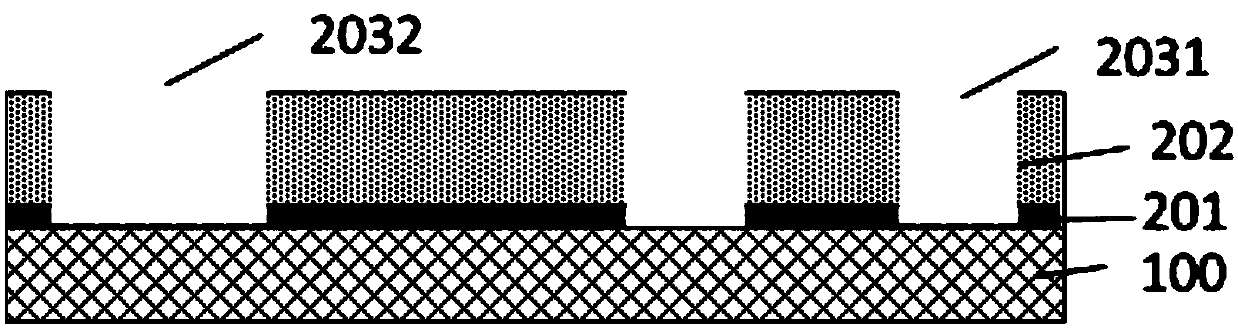

[0065] Step 3.1.2: Graphically define and use an etching process to form top electrode through holes (TEV) 4031 and top electrode through holes 4032; in the logic area, connect them to the bottom electrode contact metal layer 301; in the storage area, connect them to To the top hard mask layer 303, typically, a cleaning process is used to remove the polymer after etching, as shown in FIG. 3(b).

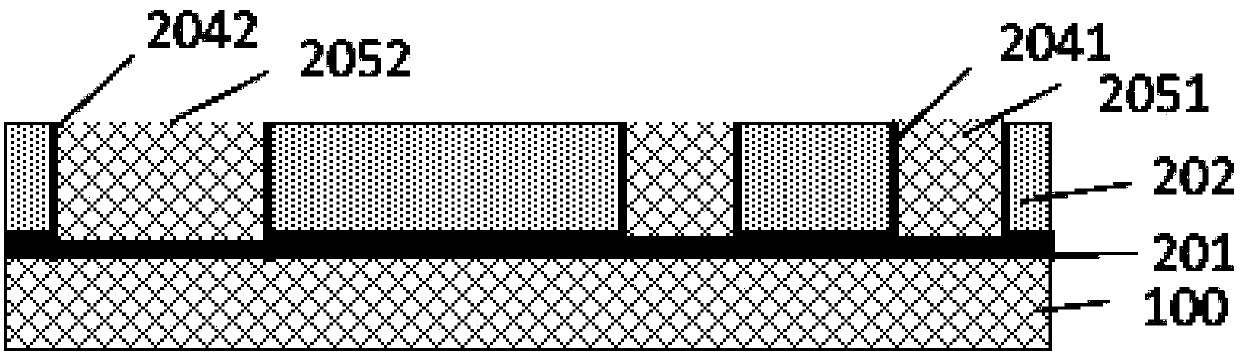

[0066] Step 3.1.3: filling metal to form top electrode via hole filling 4051 and top el...

Embodiment example 2

[0068] Implementation case 2: a dual damascene (DD, Dual Damascene) process, such as Figure 4 shown; the steps are as follows:

[0069] Step 3.2.1: On the magnetic tunnel junction dielectric capping layer (II) 401, deposit the top electrode via hole dielectric 402, and then use a planarization process to grind the top electrode via (TEV) dielectric 402 flat; the top electrode via (TEV) ) Dielectric 402 is SiO 2 , SiON or low-k and other materials, the thickness of which is 120nm ~ 400nm; finally, deposit metal wiring (M x+1 ) The thickness of dielectric 502 is 50nm~300nm, and its material is SiO 2 , SiON or low-k, etc., usually before deposition, an etch stop layer 501 with a thickness of tens of nanometers is deposited, and its material is SiN, SiC or SiCN.

[0070] Step 3.2.2: Graphically define and use an etching process to form the top electrode through hole (TEV) and the metal wiring groove connecting the logic area and the storage area. In the logic area, connect the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More