A device and method for generating SVPWM based on a PC/104 bus and an FPGA

A bus and generation module technology, applied in the direction of instrumentation, electrical digital data processing, etc., can solve the problems of weak sequential logic processing ability of CPLD, increase the complexity of hardware circuit design, high requirements for system sequential logic processing, etc., achieve rich functions, shorten R&D cycle, the effect of shortening the development cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The present invention will be further described below in conjunction with the examples and accompanying drawings, but it is not used as a limitation to the protection scope of the claims of the present application.

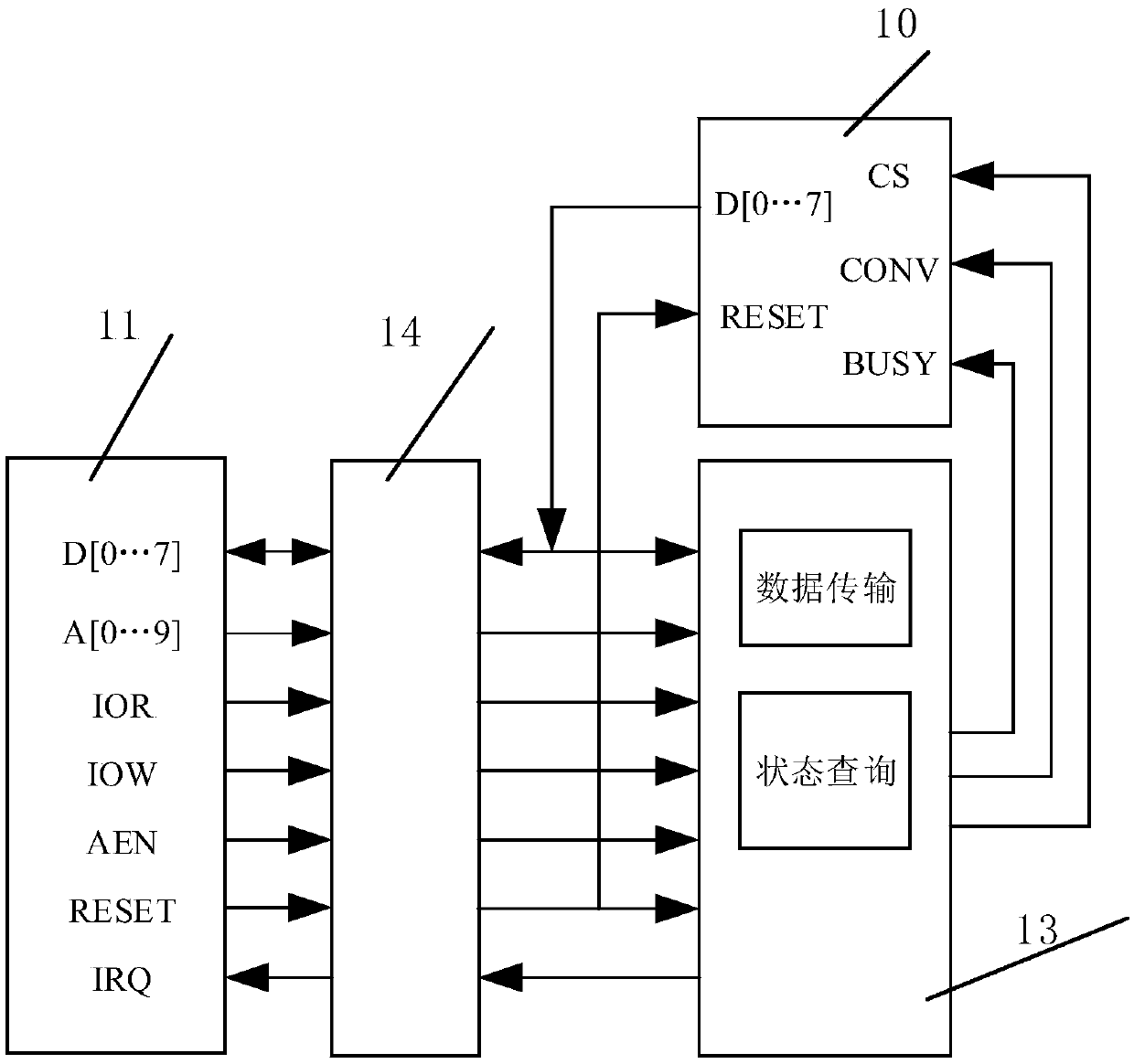

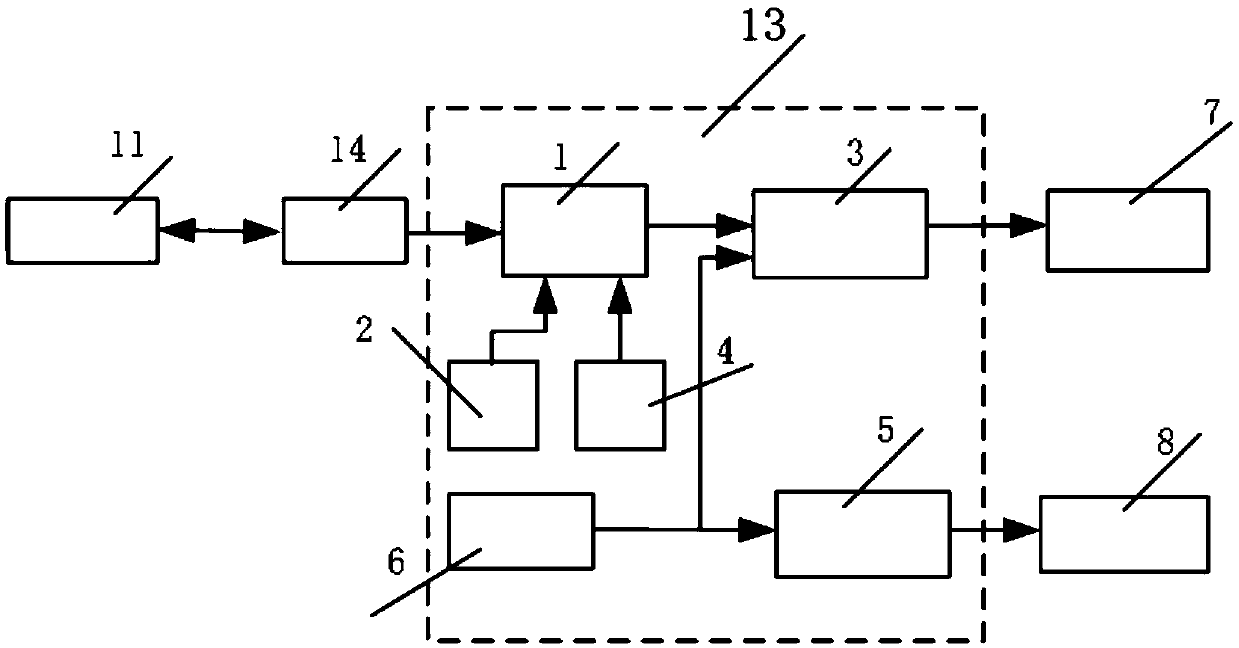

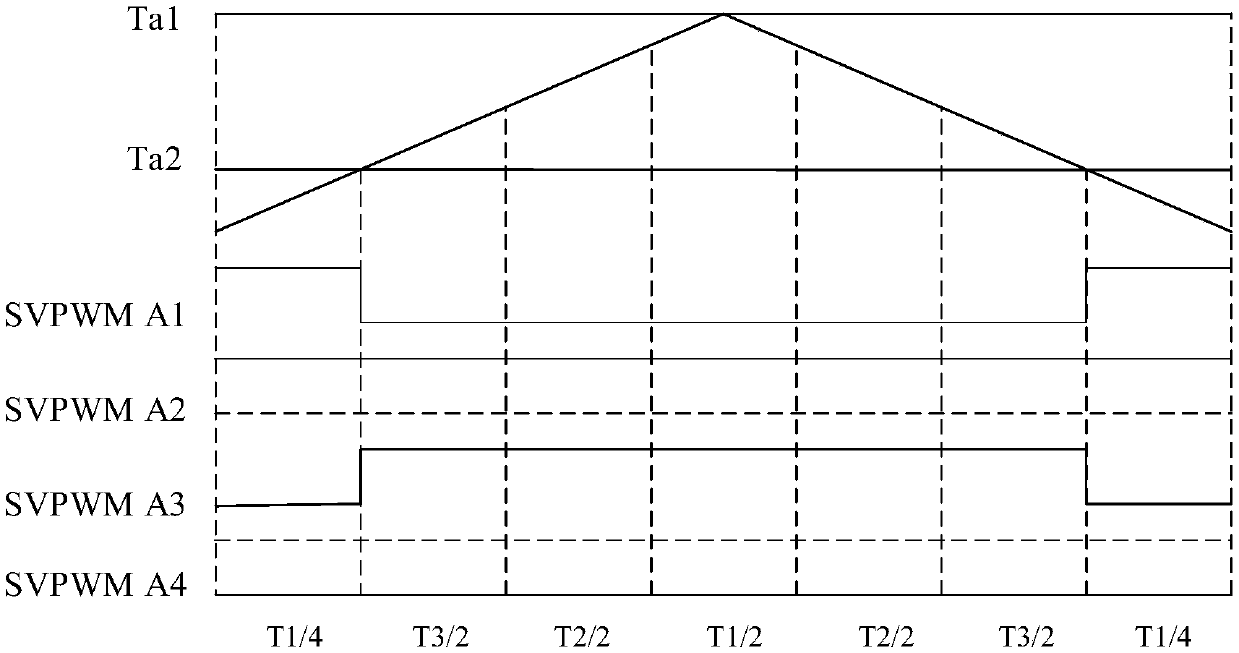

[0030] The present invention is based on PC / 104 bus and FPGA produces the device of SVPWM (abbreviation device, see Figure 5 with figure 2 ) comprises PC / 104 bus 11, data acquisition module 9, CPU module 12, A / D conversion module 10 and FPGA (complex programmable logic device) 13, level conversion module 14; The input terminal of described data acquisition module 9 is connected with The external three-phase line voltage is connected, the output end of the data acquisition module 9 is connected with the input end of the A / D conversion module 10, and the 8 data lines of the A / D conversion module pass through the DataBite0 of the level conversion module 14 and the PC / 104 bus ~DataBite7 altogether 8 data wires are connected, and CPU module 12 carries out two...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com