A large-scale manufacturing method for cmos-mems integrated chips

A technology of integrated chips and manufacturing methods, applied in the direction of manufacturing microstructure devices, gaseous chemical plating, and techniques for producing decorative surface effects, etc., can solve problems such as high cost and reduced signal transmission quality, and achieve volume reduction, Reduced footprint and reduced signal noise

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

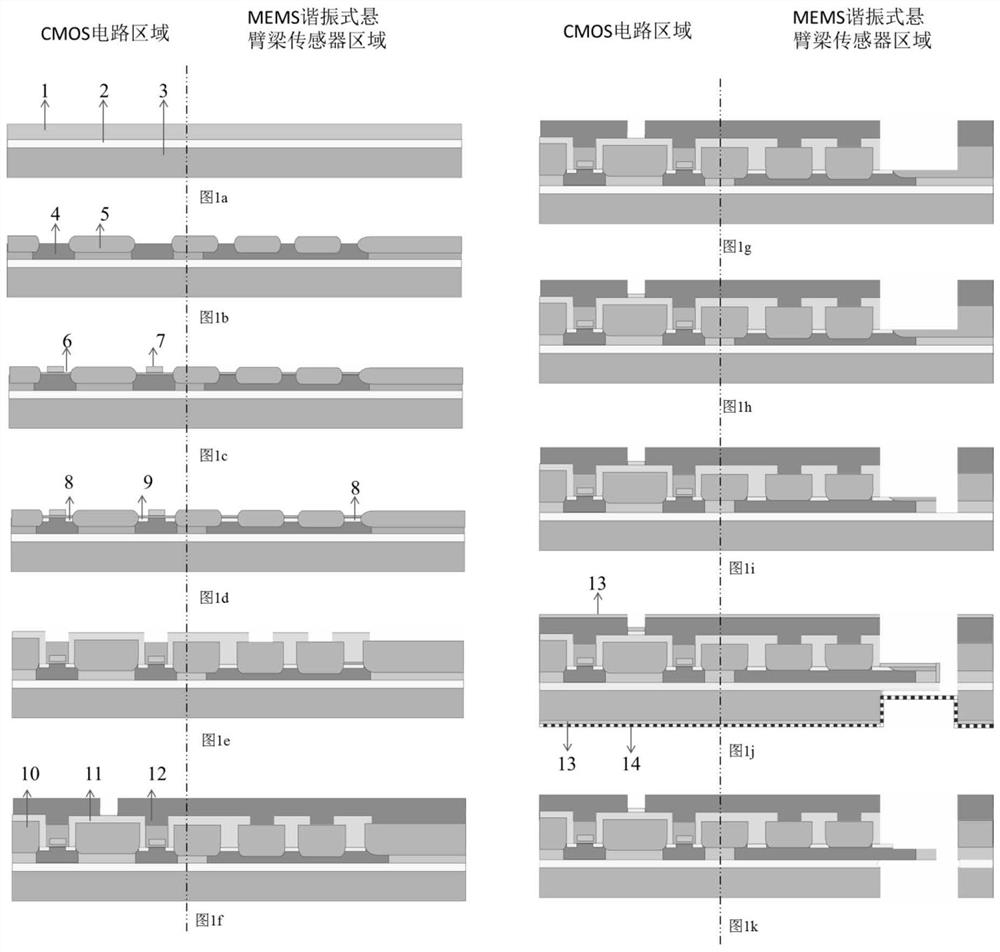

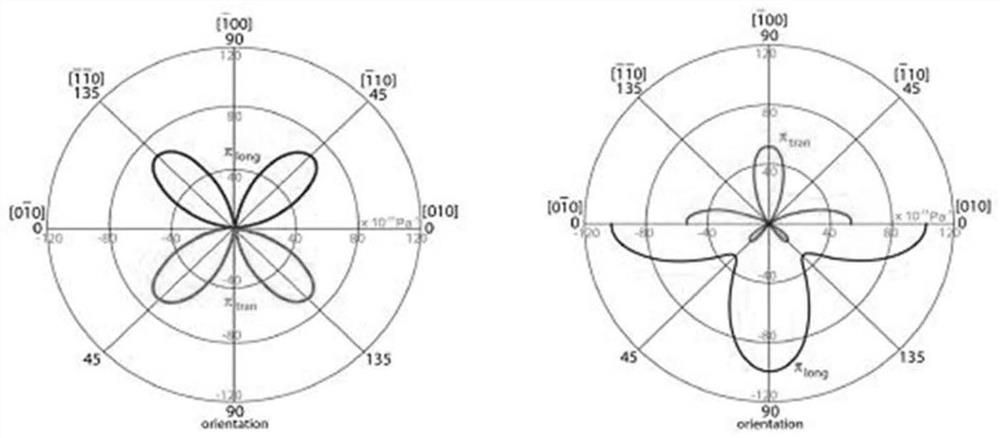

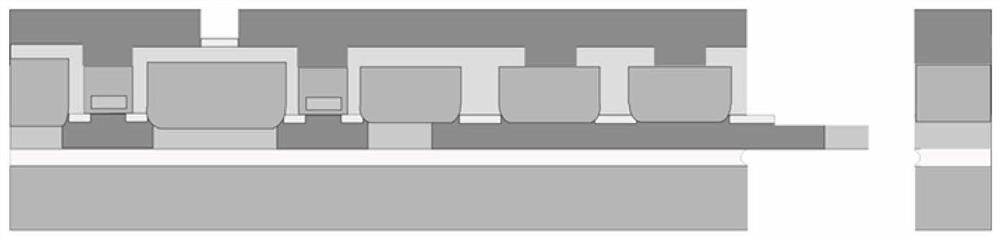

[0036] The present disclosure provides a large-scale manufacturing method of a CMOS-MEMS integrated chip. The N well / P well is manufactured in the MEMS region by using the CMOS process of injecting N well / P well, and injecting P+ / N+ into the N well / P well. Manufacturing the piezoresistive part of the MEMS region solves the contradiction that the CMOS process tends to use a P-type substrate while the MEMS resonant cantilever beam manufacturing process tends to use an N-type substrate. This disclosure adopts Inter-CMOS and Post-CMOS technology, organically integrates CMOS technology and MEMS bulk silicon manufacturing technology, completes the fabrication of MEMS electrical structure in the CMOS process, and protects the silicon chip with a passivation layer after the CMOS process is completed, through The MEMS bulk silicon process completes the fabrication of the MEMS resonant cantilever beam, which avoids the influence of the high-temperature process in the conventional MEMS el...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More