Impurity diffusion process in semiconductor device preparation process

A preparation process and impurity diffusion technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as affecting chip parameters and performance, large process deviation, and deterioration of junction characteristics, and improve product quality consistency. , saving power and water consumption, and improving the effect of device contamination

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

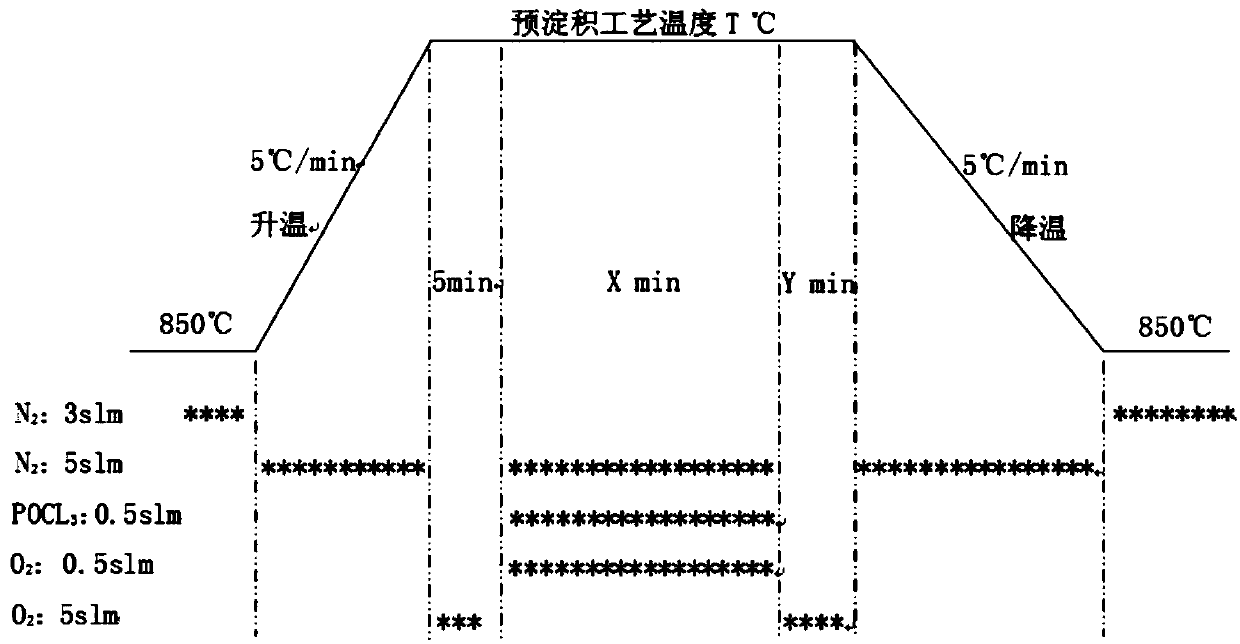

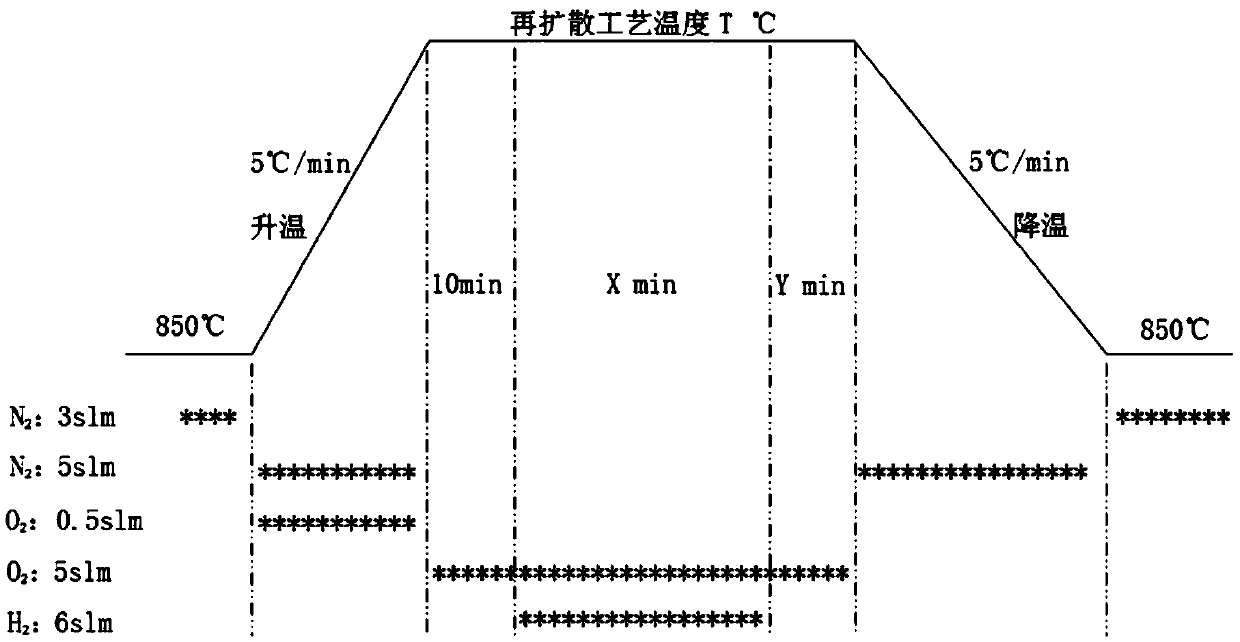

Method used

Image

Examples

Embodiment 1

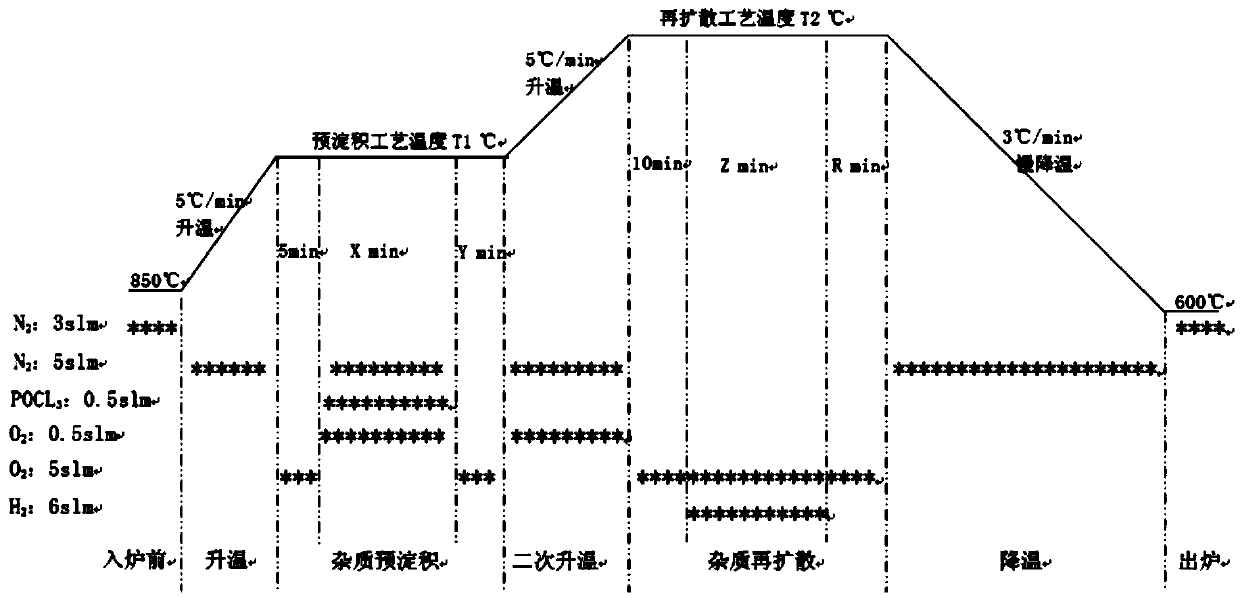

[0045] Present embodiment is the POCl of a certain product that adopts technology of the present invention to carry out 3 Diffusion of impurity phosphorus as a dopant source, the process is as follows:

[0046] 1. Clean the silicon wafer for 1.5 hours;

[0047] 2. According to the process curve ( image 3 ), wherein T1=1050°C, X=40 minutes, Y=0, T2=1140°C, Z=10 minutes, R=40 minutes, the whole process is about 5 hours, and the whole optimized process is about 6.5 hours.

[0048]Parameter comparison, the main parameters include RS (surface resistance), XJ junction depth, TOX oxide layer thickness. In the process of the process, place the front, middle and back three position measurement pieces in the constant temperature area, respectively mark 1#, 2# and 3#, to determine the parameter distribution, and test the silicon chip when performing the RS surface resistance and TOX parameter test The parameter values of the upper, middle, lower, left, and right positions are shown...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More