Wafer-level packaging structure and packaging method of floodlighting module

A technology of wafer-level packaging and flood lighting, which is applied in semiconductor/solid-state device components, semiconductor devices, electrical components, etc., can solve the problem of not meeting the needs of miniaturization and miniaturization of products in the electronics industry, and the requirement for device volume is not high , large device size and other issues, to achieve the effect of good consistency, excellent optical performance, and high alignment accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

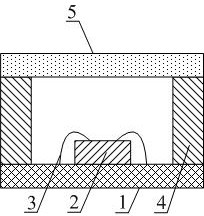

[0033] Such as figure 1 As shown, a wafer-level packaging structure of a floodlighting module in this embodiment includes a substrate 1, a functional chip 2, spacers 4, and optical components 5; wherein, the substrate 1 is a ceramic substrate, and the substrate 1 is It has at least one pair of positioning marks (not shown); the functional chip 2 is arranged on the surface of the substrate, the functional chip 2 is a vertical cavity surface emitting laser, and the surface of the functional chip 2 is electrically connected to the surface of the substrate 1 through a metal wire 3; the functional chip 2 The peripheral substrate is provided with a spacer 4, the upper end of the spacer 4 is higher than the functional chip 2; the optical component 5 is arranged above the functional chip 2, and the two ends of the optical component 5 are respectively connected to the spacer 4 on the periphery of the functional chip 2. The top end of the optical component 5 and the spacer 4 jointly for...

Embodiment 2

[0038] A wafer-level packaging method for a floodlighting module, comprising the following steps:

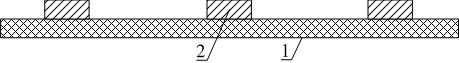

[0039] 1. See figure 2 , providing a clean substrate 1 having at least one pair of alignment marks (not shown).

[0040] Two, see image 3 , integrating multiple functional chips 2 onto the substrate through a die bond process.

[0041] 3. See Figure 4 , using a wire bonding (wire bond) process to realize the electrical connection between the functional chip 2 and the surface of the substrate 1 through the metal wire 3 .

[0042] 4. Apply glue dispensing process to coat glue layer A (not shown) on the surface of the substrate between multiple functional chips 2;

[0043] 5. Use a lithography machine to complete the alignment of the spacer 4 and the substrate 1 through the semiconductor back side alignment (Back Side Alignment) method. After the alignment is completed, the lower end of the spacer 4 is in contact with the adhesive layer A; lock the substrate 1 and The space...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More