Superjunction device structure and preparation method thereof

A technology of super junction device and column structure, applied in the field of super junction device structure and its preparation, can solve the problem of uneven defect in super junction drift region, achieve optimized reverse recovery characteristics, reduce carrier life, and low cost Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

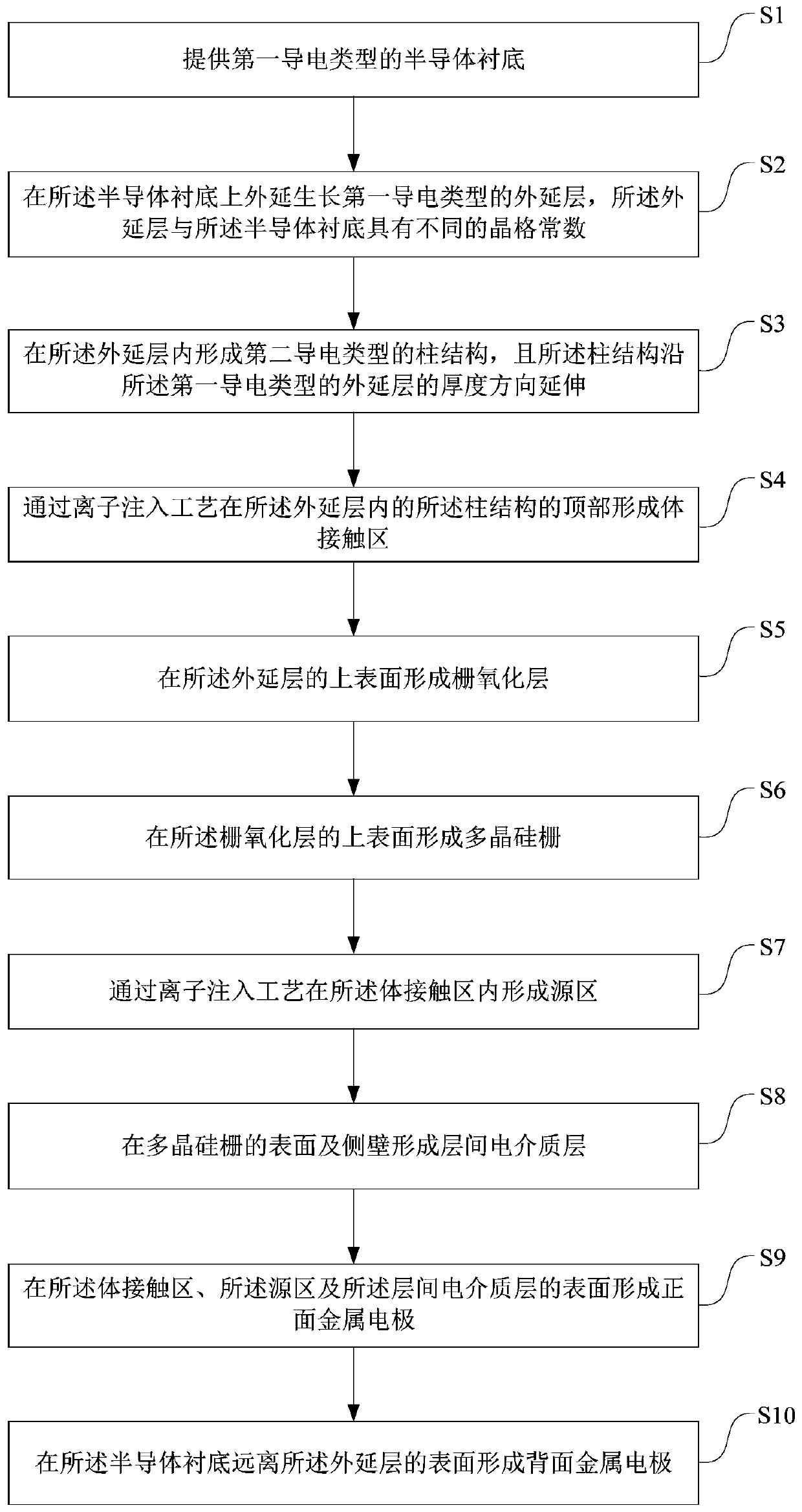

[0078] see Figure 1 to Figure 12 , the invention provides a method for preparing a superjunction device structure, comprising the following steps:

[0079] 1) providing a semiconductor substrate 101 of the first conductivity type;

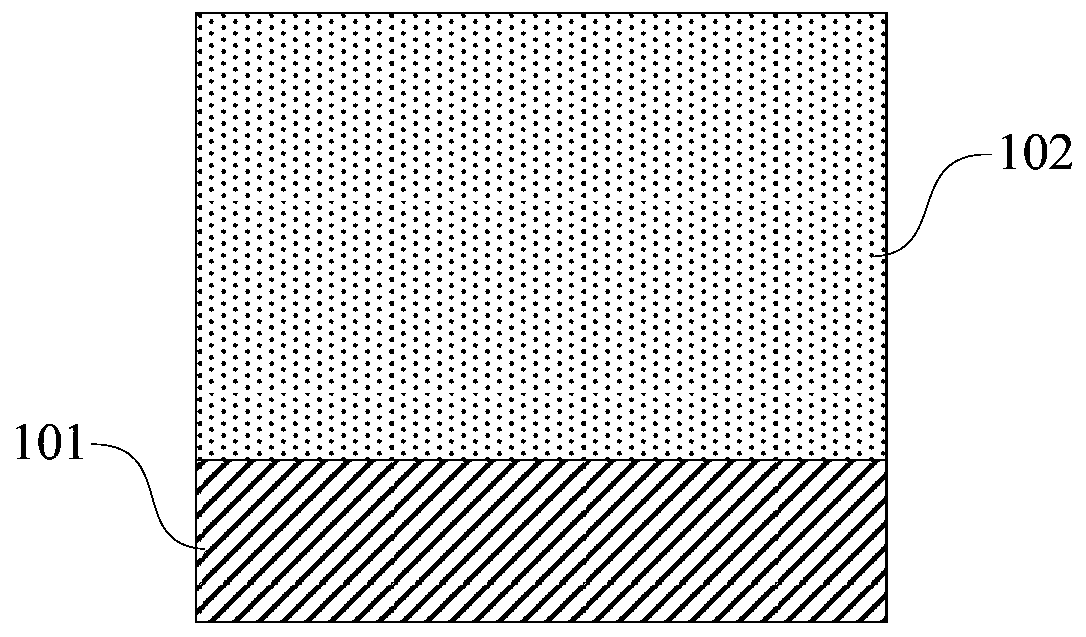

[0080] 2) epitaxially growing an epitaxial layer 102 of the first conductivity type on the semiconductor substrate 101, the epitaxial layer 102 having a different lattice constant from the semiconductor substrate 101;

[0081] 3) Forming a column structure 103 of the second conductivity type in the epitaxial layer 102 , and the column structure 103 extends along the thickness direction of the epitaxial layer 102 .

[0082] In step 1), see figure 1 The S1 step and figure 2 , providing a semiconductor substrate 101 of the first conductivity type. figure 2 is a schematic cross-sectional view of the semiconductor substrate 101. Optionally, in this embodiment, the first conductivity type is n-type, and the semiconductor substrate 101 is an n-typ...

Embodiment 2

[0121] see Figure 13 , this embodiment provides a super junction device structure and its preparation method. Compared with Embodiment 1, the difference of this embodiment is that the constituent material of the column structure 203 is germanium silicon material, and through the 103 a is epitaxially filled with silicon germanium material to form the column structure 203 .

[0122] As an example, in Figure 13 Among them, the super junction device structure includes a semiconductor substrate 201 of the first conductivity type, an epitaxial layer 202 of the first conductivity type and a column structure 203 of the second conductivity type, wherein the material of the column structure 203 is silicon germanium Material. Such as Figure 13 As shown, the super junction device structure further includes: a body contact region 204 , a gate oxide layer 205 , a polysilicon gate 206 , a source region 207 , an interlayer dielectric layer 208 , a front metal electrode 209 and a back me...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More