GaN-based field effect transistor and preparation method thereof

A GaN-based field and transistor technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of two-dimensional electron gas depletion, the influence of two-dimensional electron gas concentration, and the reduction of device characteristics.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, but not to limit the present invention. In addition, it should be noted that, for the convenience of description, only some structures related to the present invention are shown in the drawings but not all structures.

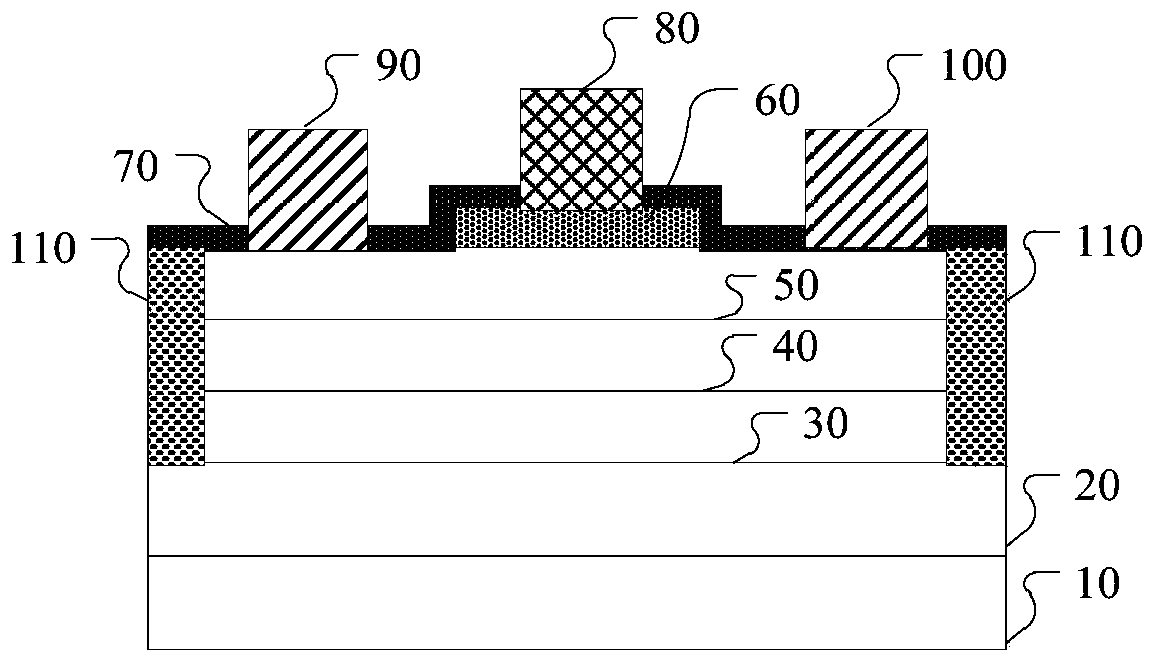

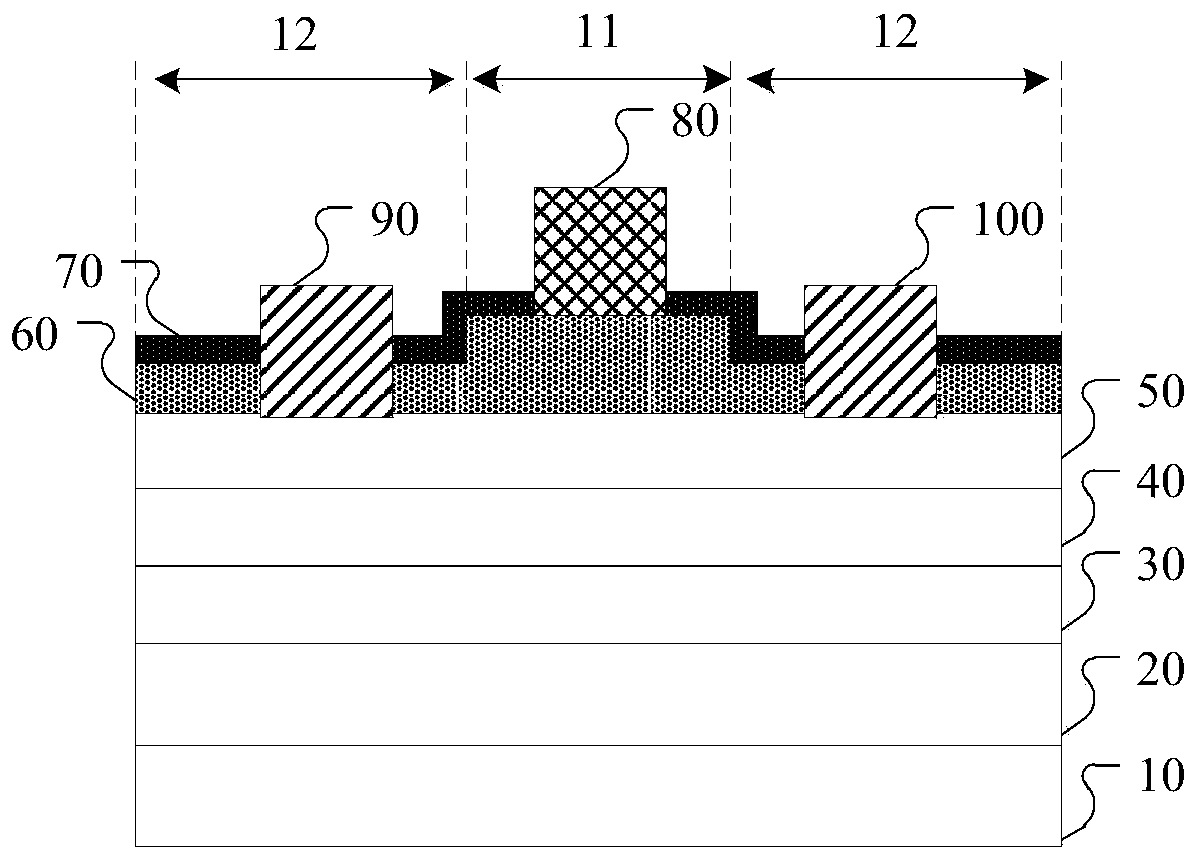

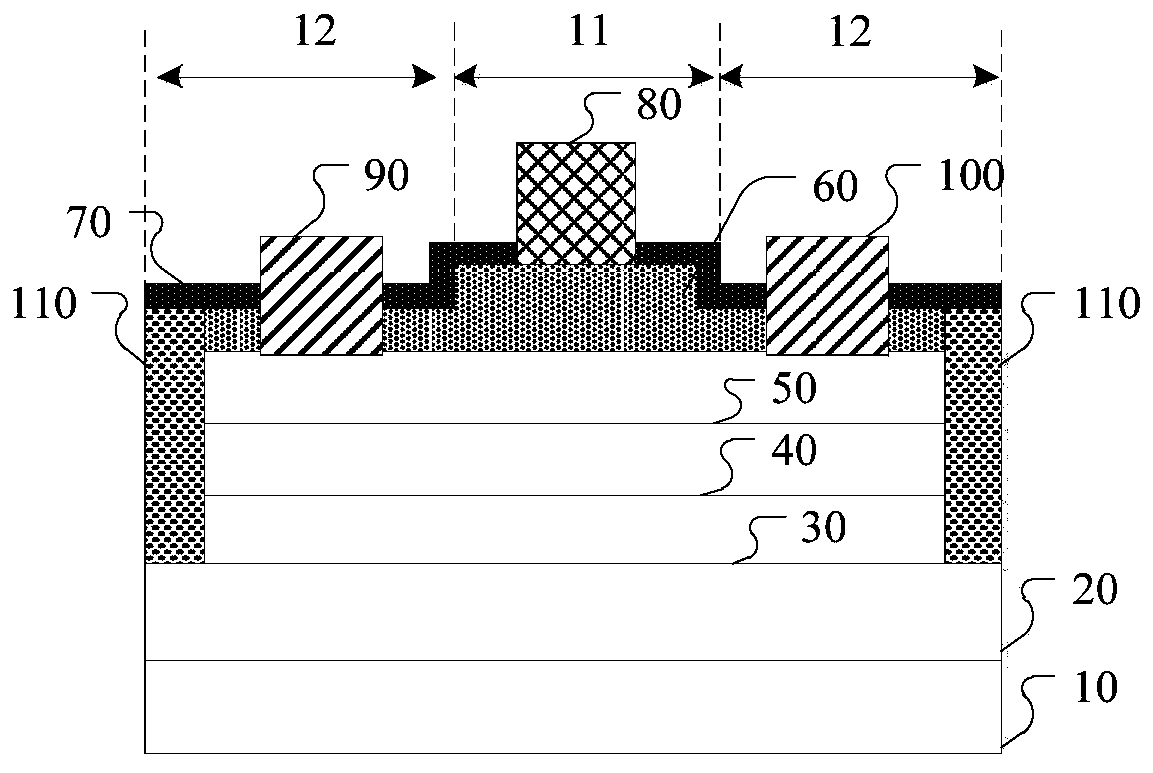

[0051] An embodiment of the present invention provides a GaN-based field effect transistor, referring to figure 1 , figure 1 It is a schematic structural diagram of a GaN-based field effect transistor provided in Embodiment 1 of the present invention, including:

[0052] Stacked substrate 10, buffer layer 20, back barrier layer 30, channel layer 40, barrier layer 50, p-type gate layer 60 and passivation layer 70;

[0053] Gate 80 in contact with p-type gate layer 60, and source 90 and drain 100 penetrating throu...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More