FPGA graph processing acceleration method and system based on OpenCL

A technology of graph computing and basic instructions, applied in the field of big data processing, can solve the problems of system performance degradation, limited FPGA chip cache, waste of the advantages of high parallelism of FPGA, etc., to reduce memory access delay, reduce memory access times, The effect of improving system efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

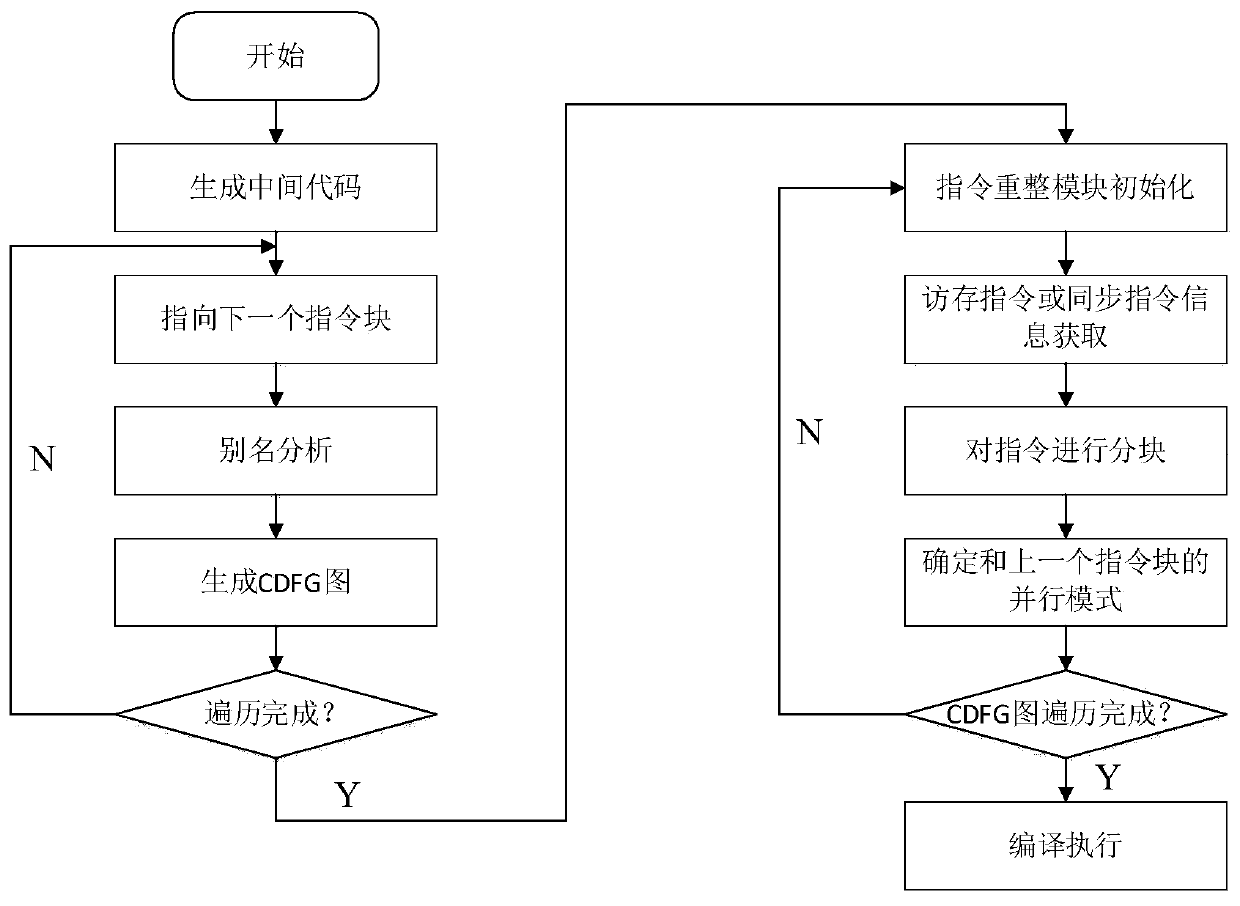

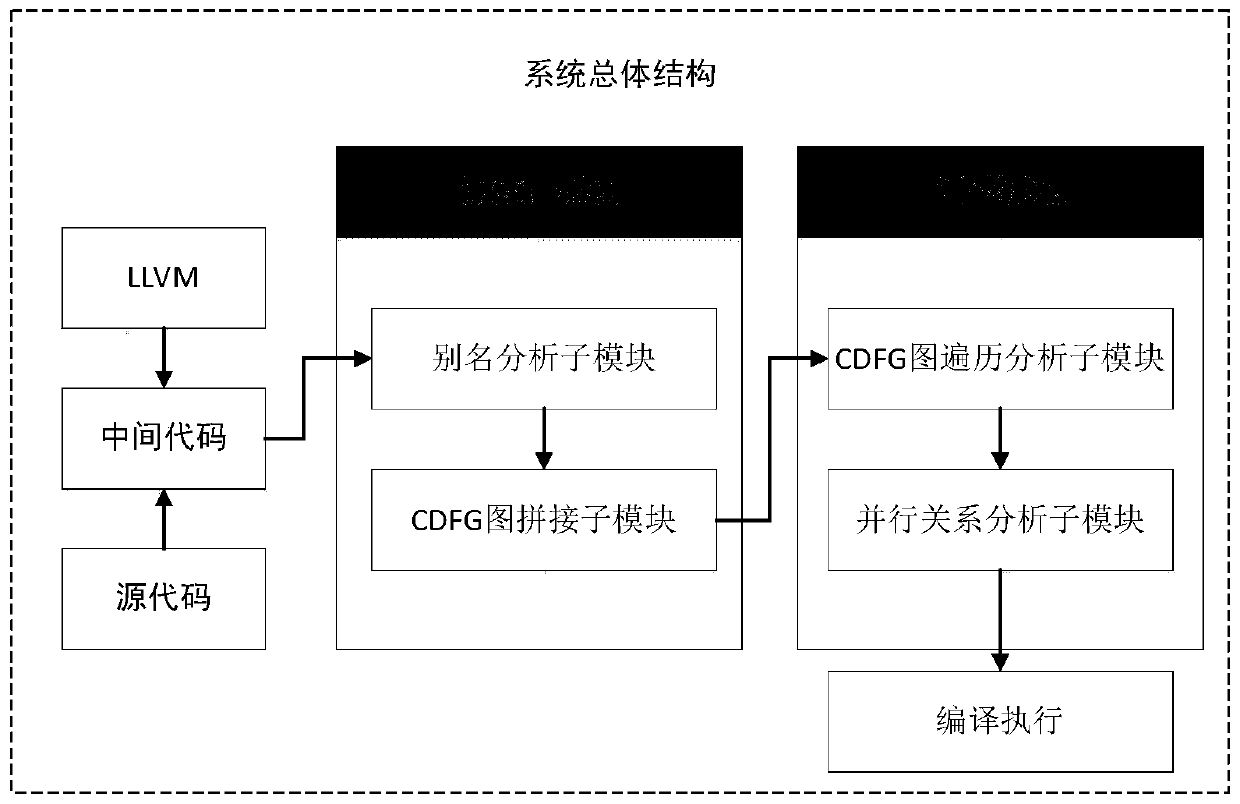

Method used

Image

Examples

Embodiment 1

[0100] The energy management system EMS mainly provides grid dispatchers with various real-time information of the grid, including: frequency, generator power, line power, bus voltage, etc., and conducts scheduling decision-making management of the grid to realize centralized monitoring and control of power production and transmission , to ensure the safe, high-quality and economical operation of the power grid. The power system needs to realize real-time / ultra-real-time EMS, and all calculations need to be completed within the sampling time, which generally includes two types: transient calculation and steady-state calculation. The core of steady-state calculation is power flow calculation. At present, power system applications are mainly implemented on the CPU, but power flow calculations have very fine-grained parallelism, which is not supported by general-purpose CPUs and cannot meet real-time requirements.

[0101] An annotated power flow distribution graph is a directed ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More