Quick mapping method for normally open defect of nano CMOS circuit represented by matrix

A technology of matrix representation and mapping method, which is applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., and can solve problems such as reducing the mapping area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0051] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

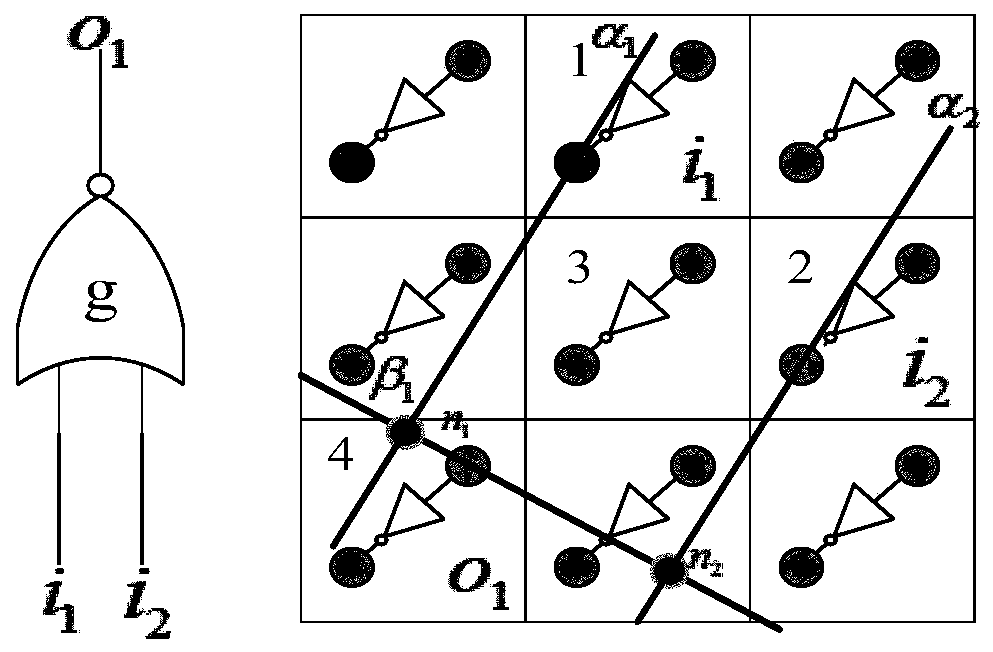

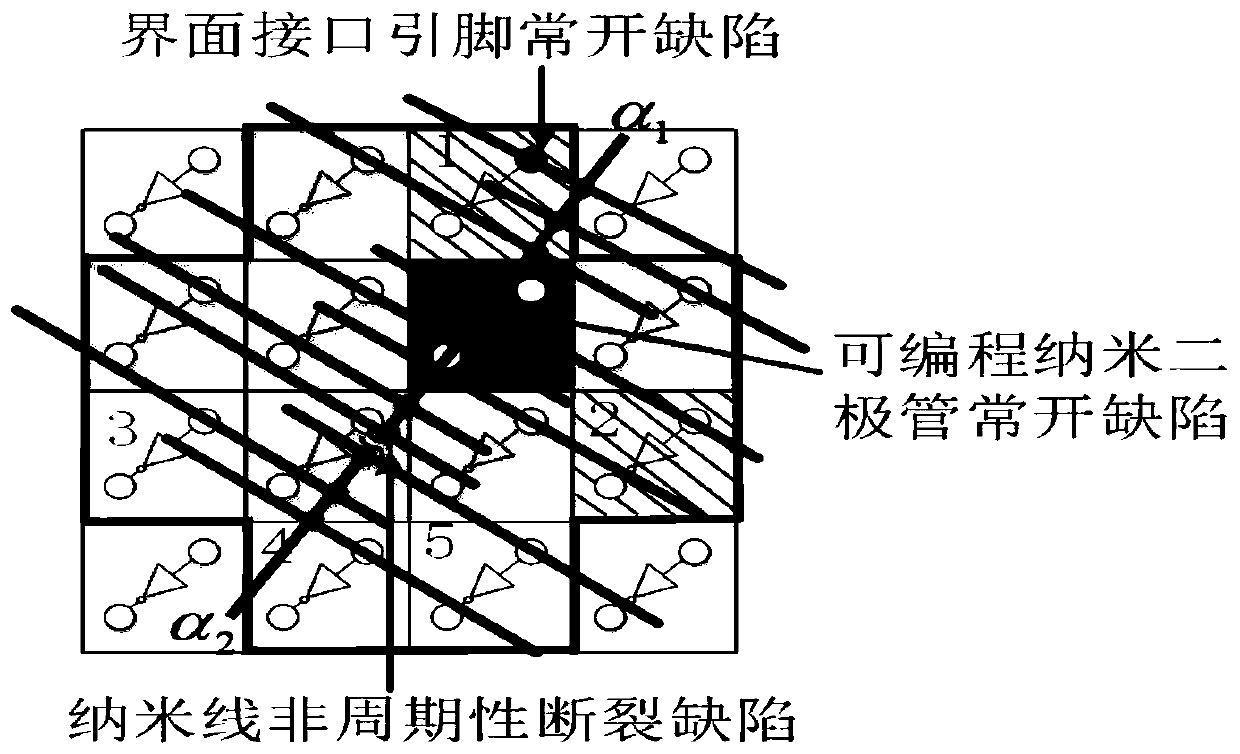

[0052] by Figure 4 (a) shows a NOR gate logic circuit containing 11 nodes as an example, and it is mapped to a 4×4 size in the form of a matrix Figure 5 The defective nano-CMOS circuit shown in (a) adopts the method of the present invention to carry out fast fault-tolerant mapping, specifically comprises the following steps:

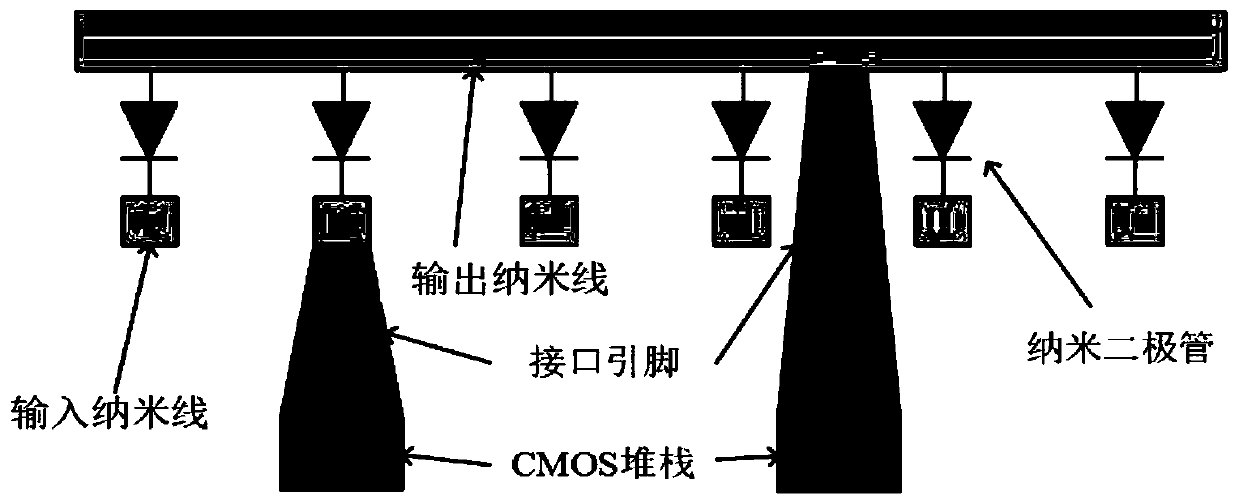

[0053] Step ①: For any nano-CMOS circuit including output nanowire layer, input nanowire layer, several programmable nano-diodes and bottom CMOS inverter array, if any programmable nano-diode is always in the off state, causing its The signal path between the connected two nanometer CMOS units is always disconnected, and the defect is defined as a programmable nanodiode normally-on defect; if any output nanowire or input nanowire breaks irregularly at the non-periodic breakpoint , causing the connected domain of the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More