Substrate wafer structure for improving resistivity of substrate and preparation method

A substrate wafer and resistivity technology, which is applied in the manufacture of circuits, electrical components, semiconductors/solid-state devices, etc., can solve the problem that the power consumption of low-power devices cannot be effectively reduced significantly, and the thickness of the substrate cannot be effectively thinned , Improve resistivity and other issues, achieve the effect of improving resistivity, solving technical requirements for ultra-thin sheet processing, and increasing the range of resistivity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

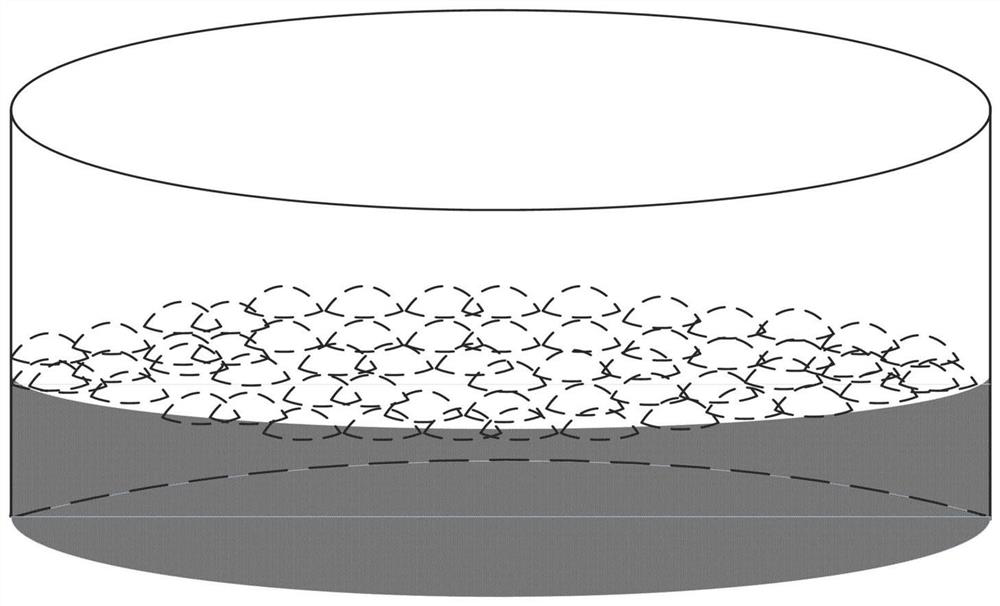

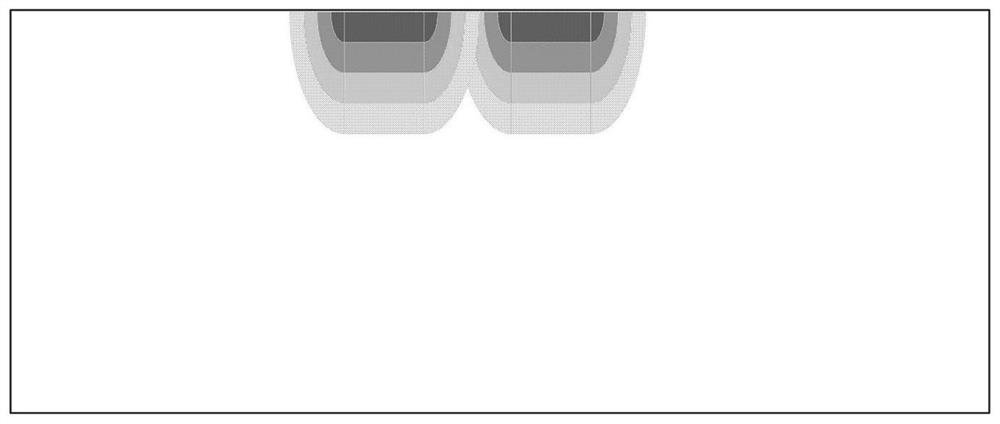

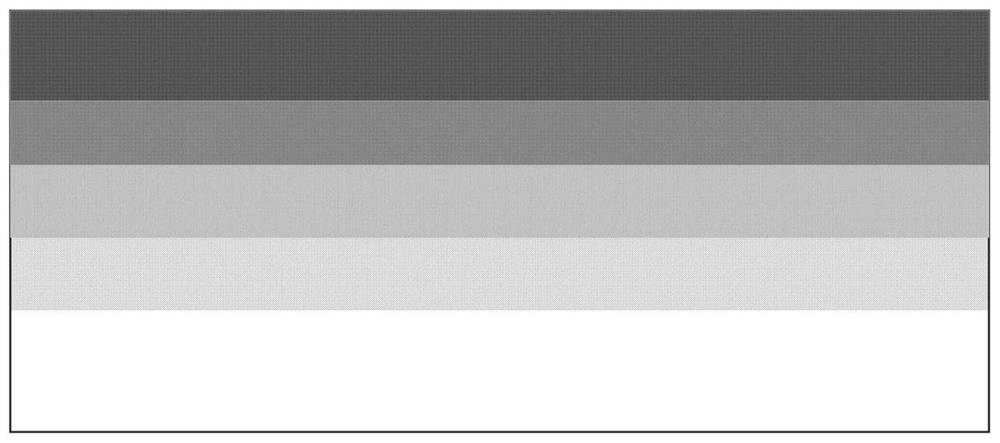

[0042] combined with figure 2 And attached image 3 The schematic diagram of the substrate structure of the single-sided ion implantation or doping method under different implantation windows and depths, the distribution of the ion structure inside the wafer after high temperature diffusion is shown in the attached figure 1 shown;

[0043] Step 1: Select a certain amount of substrate wafers and divide them into different intervals according to different res...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More