Trench gate semiconductor device and manufacturing method thereof

A manufacturing method and trench gate technology are applied in the manufacture of trench gate semiconductor devices and in the field of trench gate semiconductor devices, which can solve problems such as restricting process development and manufacturing difficulties, and achieve step reduction and elimination of step limitations. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

[0079] The trench gate semiconductor device of the first embodiment of the present invention:

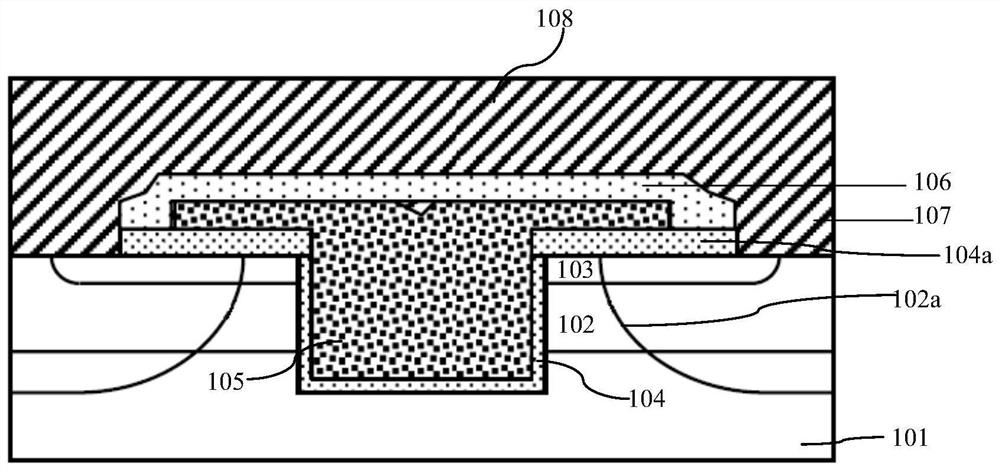

[0080] Such as Figure 4 As shown, it is a schematic structural diagram of a trench gate semiconductor device in the first embodiment of the present invention; the trench gate semiconductor device in the embodiment of the present invention includes:

[0081] A body region 2 doped with a second conductivity type is formed in the first epitaxial layer 1 doped with the first conductivity type, the body region 2 extending downward from the top surface of the first epitaxial layer 1 .

[0082] The trench gate includes a gate trench 4 , a gate dielectric layer 5 and a gate conductive material layer 6 . In the first embodiment of the present invention, the gate dielectric layer 5 includes a gate oxide layer; the gate conductive material layer 6 includes a polysilicon gate.

[0083] The gate trench 4 passes through the body region 2 , and the top surface of the gate trench 4 is even with ...

no. 2 example

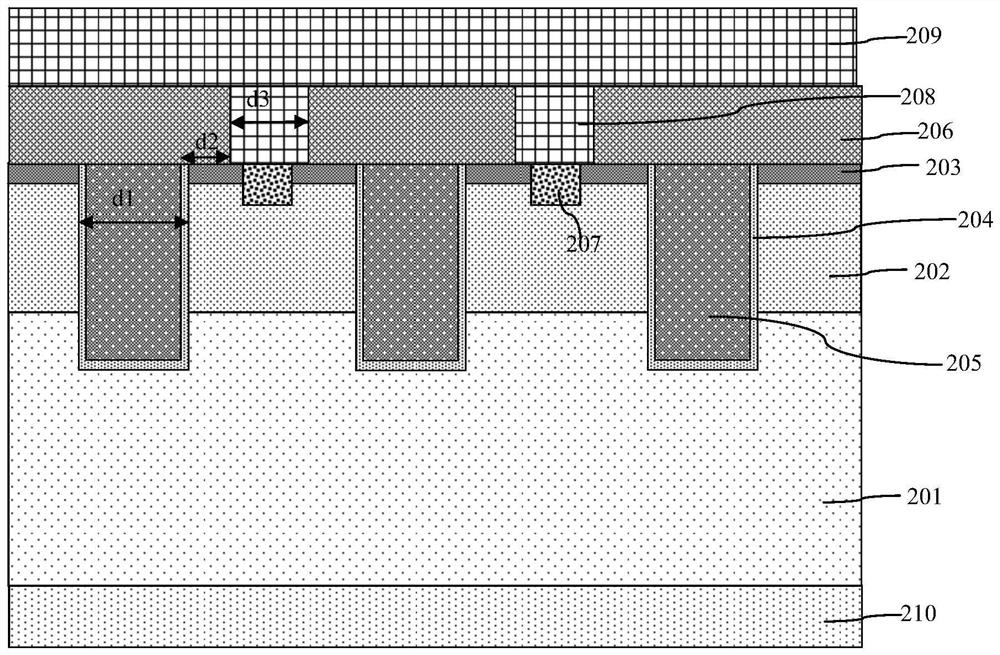

[0096] The trench gate semiconductor device of the second embodiment of the present invention:

[0097] Such as Figure 5 As shown, it is a schematic structural diagram of the trench gate semiconductor device of the second embodiment of the present invention; the difference between the trench gate semiconductor device of the second embodiment of the present invention and the trench gate semiconductor device of the first embodiment of the present invention is:

[0098] A super junction structure is formed in the first epitaxial layer 1 , and the super junction structure is formed by alternating columns 12 of the first conductivity type and the second conductivity type.

[0099] The first conductivity type columns are composed of the first epitaxial layer 1 between the second conductivity type columns 12; the second conductivity type columns 12 are composed of second conductivity type ion implantation regions or filled with The superjunction trench is composed of a second epita...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More