Superconducting integrated circuit layout optimization method and device, storage medium, and terminal

A layout optimization, integrated circuit technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problem of spending a lot of time, affecting the chip iteration cycle, and unable to meet the requirements of large-scale automatic design of superconducting integrated circuits and other problems to achieve the effect of improving the calculation effect and optimizing the layout results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0066] In order to solve the technical problems existing in the prior art, an embodiment of the present invention provides a method for optimizing the layout of a superconducting integrated circuit.

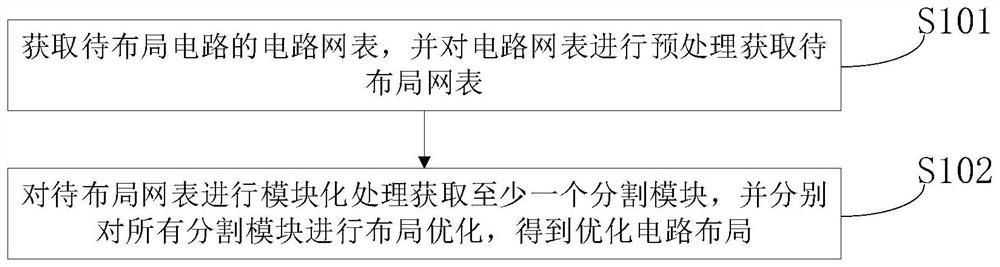

[0067] figure 1 It shows a schematic flow chart of a superconducting integrated circuit layout optimization method according to an embodiment of the present invention; refer to figure 1 As shown, the method for optimizing the layout of a superconducting integrated circuit in the embodiment of the present invention includes the following steps.

[0068] Step S101, obtaining a circuit netlist of a circuit to be placed, and performing preprocessing on the circuit netlist to obtain a netlist to be placed.

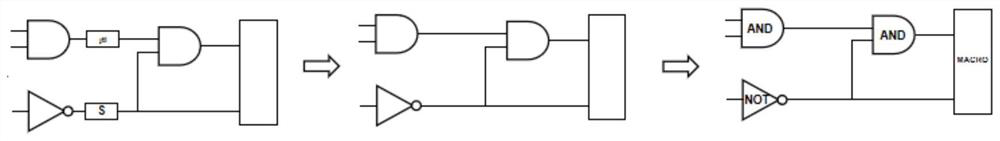

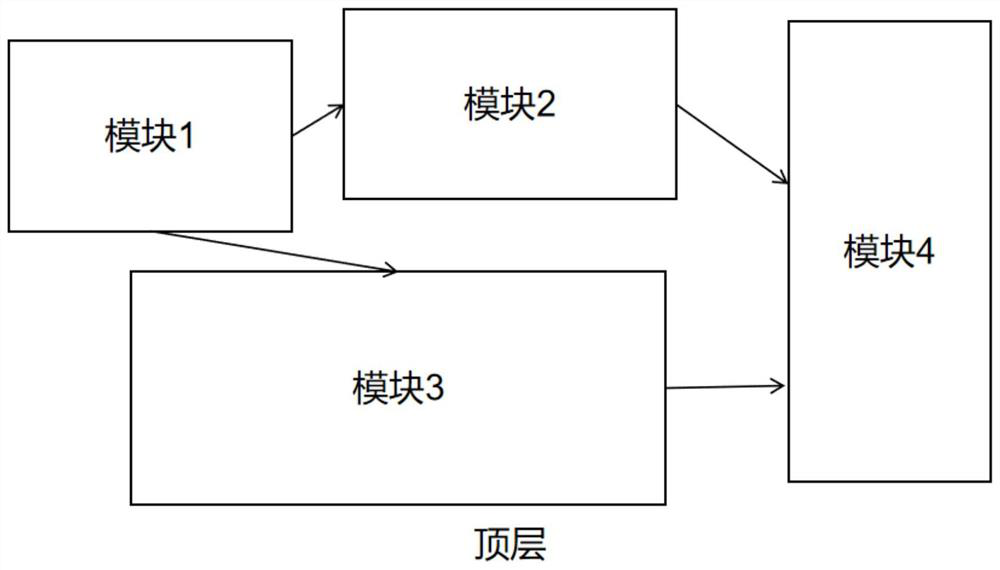

[0069] Specifically, the circuit netlist after logic synthesis of the circuit to be placed is obtained, and then the circuit netlist is preprocessed to obtain the netlist to be placed. figure 2 It shows a schematic diagram of the effect of preprocessing the circuit netlist in E...

Embodiment 2

[0091] In order to solve the technical problems existing in the prior art, an embodiment of the present invention provides a superconducting integrated circuit layout optimization device.

[0092] Figure 9 It shows a schematic structural diagram of a superconducting integrated circuit layout optimization device according to Embodiment 2 of the present invention; refer to Figure 9 As shown, the device for optimizing the layout of a superconducting integrated circuit according to the embodiment of the present invention includes a preprocessing mechanism and an optimization mechanism.

[0093] The preprocessing mechanism is used to obtain the circuit netlist of the circuit to be identified, and preprocess the circuit netlist to obtain the netlist to be laid out;

[0094] The optimization mechanism performs modular processing on the layout netlist to obtain at least one segmentation module, and performs global layout optimization on all segmentation modules respectively to obta...

Embodiment 3

[0103] In order to solve the above-mentioned technical problems existing in the prior art, an embodiment of the present invention also provides a storage medium, which stores a computer program, and when the computer program is executed by a processor, it can realize Embodiment 1 Superconducting Integrated Circuit Layout Optimization Method All steps in .

[0104] The specific steps of the superconducting integrated circuit layout optimization method and the beneficial effects obtained by applying the readable storage medium provided by the embodiment of the present invention are the same as those of the first embodiment, and will not be repeated here.

[0105] It should be noted that the storage medium includes various media capable of storing program codes such as ROM, RAM, magnetic disk or optical disk.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More