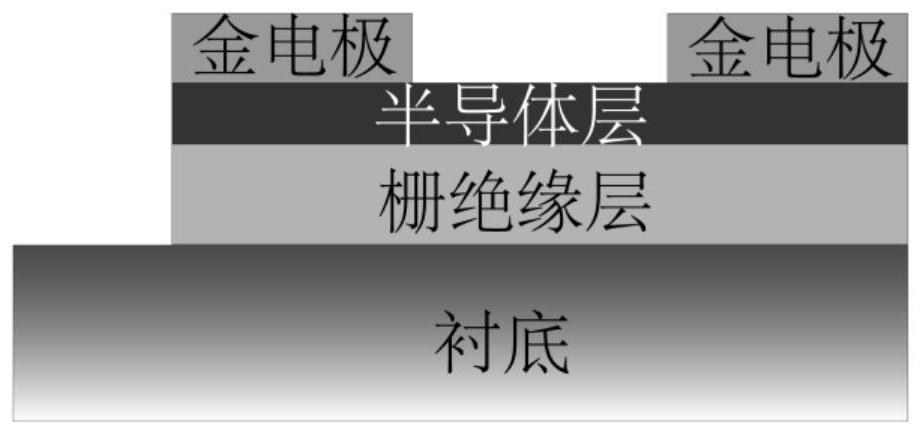

Synaptic transistor device based on novel polyimide gate insulating layer and preparation method thereof

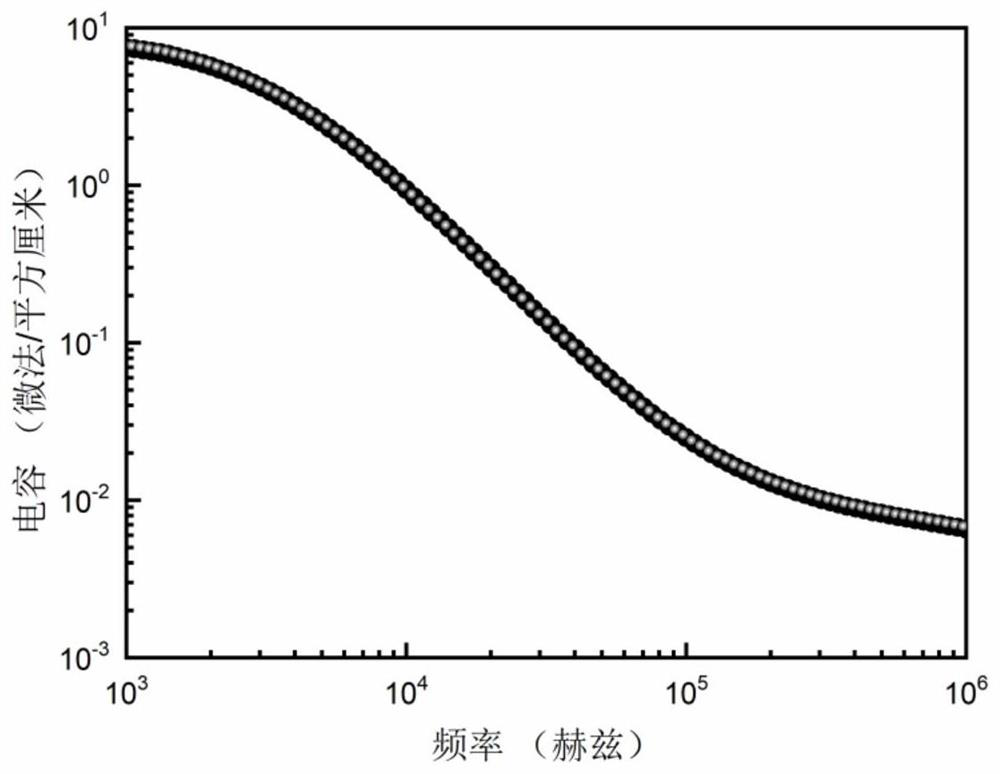

A technology of gate insulating layer and polyimide, which is applied in the field of synaptic transistor electronic devices, can solve the problems of large power consumption and small working voltage range, and achieve the effects of low power consumption, large working voltage range and large specific capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0039] A method for preparing a synaptic transistor device based on a novel polyimide gate insulating layer is as follows:

[0040] (1) Clean the conductive glass substrate with a size of 2 × 2 cm and a thickness of 2 mm by ultrasonic cleaning with deionized water, acetone and isopropanol in sequence, then blow dry the surface of the substrate with nitrogen gas, and put it into a UV cleaning machine for 15 minute;

[0041] (2) PMDA-ODA amic acid solution (the solvent of this solution is made of N-methylpyrrolidone (NMP) and xylene (xylene) according to volume ratio 4 ratio with the PMDA-ODA amic acid solution of ionic liquid [EMIM] [TFSI] and 12% mass fraction 1.) According to the mass ratio of 1 to 20, mix and stir evenly to obtain a light yellow and clear mixed solution of PMDA-ODA polyimide and ionic liquid [EMIM][TFSI].

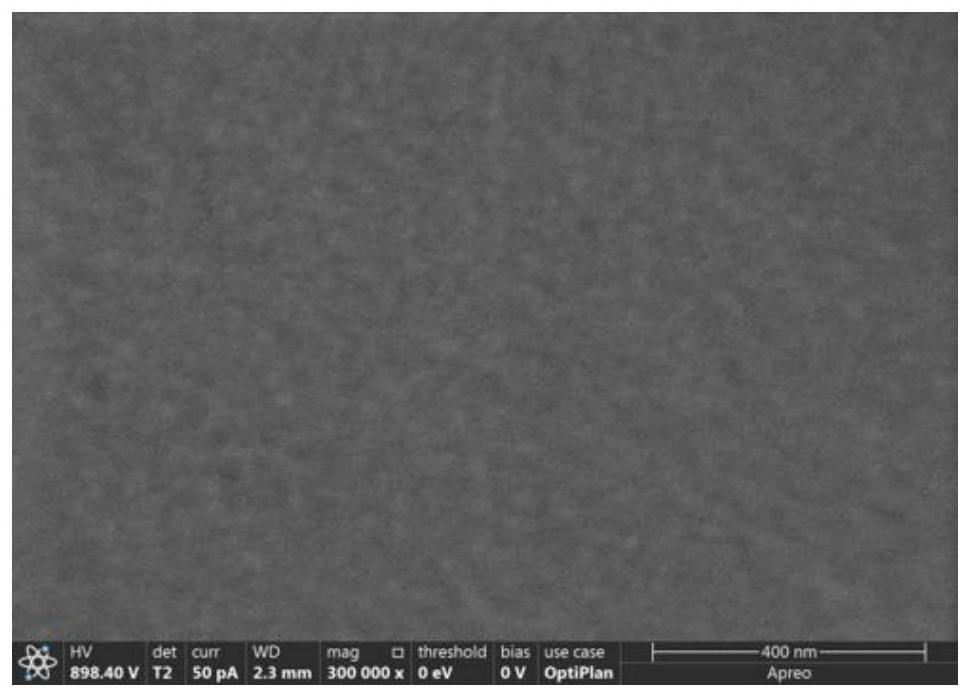

[0042] (3) in the glove box, drip the mixed solution of PMDA-ODA type polyimide and ionic liquid [EMIM][TFSI] in the substrate of 4 square centimeters ste...

Embodiment 2

[0050] A method for preparing a synaptic transistor device based on a novel polyimide gate insulating layer is as follows:

[0051] (1) Clean the conductive glass substrate with a size of 2 × 2 cm and a thickness of 2 mm by ultrasonic cleaning with deionized water, acetone and isopropanol in sequence, then blow dry the surface of the substrate with nitrogen gas, and put it into a UV cleaning machine for 15 minute;

[0052] (2) PMDA-ODA amic acid solution (the solvent of this solution is made of N-methylpyrrolidone (NMP) and xylene (xylene) according to volume ratio 4 ratio with the PMDA-ODA amic acid solution of ionic liquid [EMIM] [TFSI] and 12% mass fraction 1.) According to the mass ratio of 1 to 10, mix and stir evenly to obtain a light yellow and clear mixed solution of PMDA-ODA polyimide and ionic liquid [EMIM][TFSI].

[0053] (3) in the glove box, drip the mixed solution of PMDA-ODA type polyimide and ionic liquid [EMIM][TFSI] in the substrate of 4 square centimeters s...

Embodiment 3

[0058] Other steps are with embodiment 1, and difference is that the polyamic acid solution in the step (2) is replaced by PMDA-ODA amic acid solution by PMDA-ODA amic acid solution, wherein, the solvent in the BPDA-ODA amic acid solution is N - Methylpyrrolidone (NMP).

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More