Semiconductor structure preparation method and semiconductor structure

A semiconductor and mask layer technology, applied in semiconductor/solid-state device manufacturing, transistors, electrical components, etc., can solve problems affecting pattern transfer, required pattern deviation, bit line contact structure deviation, etc., to avoid alignment deviation effect of shifting, improving alignment accuracy, and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The method for preparing the semiconductor structure provided by the present invention and the specific implementation of the semiconductor structure will be described in detail below in conjunction with the accompanying drawings.

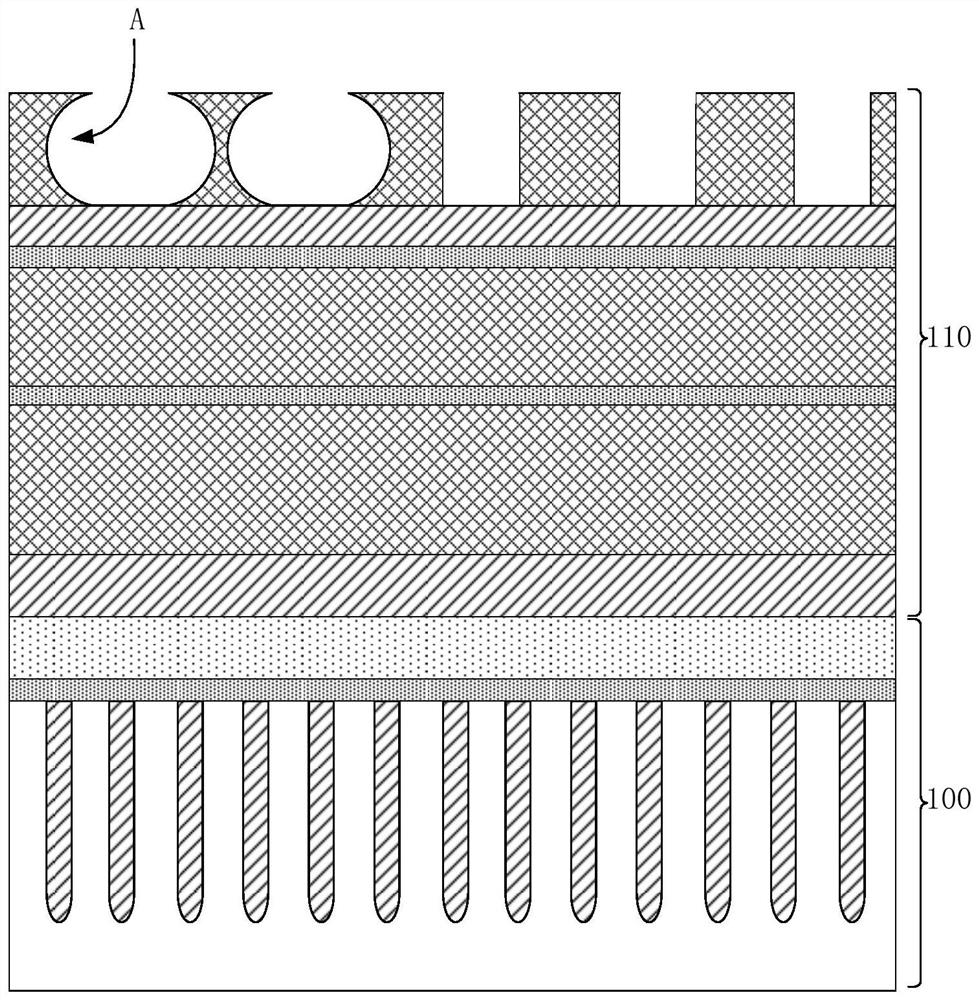

[0030] Figure 1A is a schematic top view of the semiconductor structure provided by the first embodiment of the present invention, please refer to Figure 1A , the semiconductor structure includes a substrate 100 and a mask layer 110 disposed on the substrate 100. When patterning the top mask layer, since the material hardness of the top mask layer is small, the side of the top mask layer The wall will form an arcuate bend (eg Figure 1A The area indicated by the middle arrow A). Then when pattern transfer is performed based on the pattern of the top mask layer, such as Figure 1B and Figure 1C As shown, among them, Figure 1B is a schematic top view of the mask layer 110 of the semiconductor structure, Figure 1C for along Figure ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Angle | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com