Integrated circuit optical proximity correction parallel processing method and system

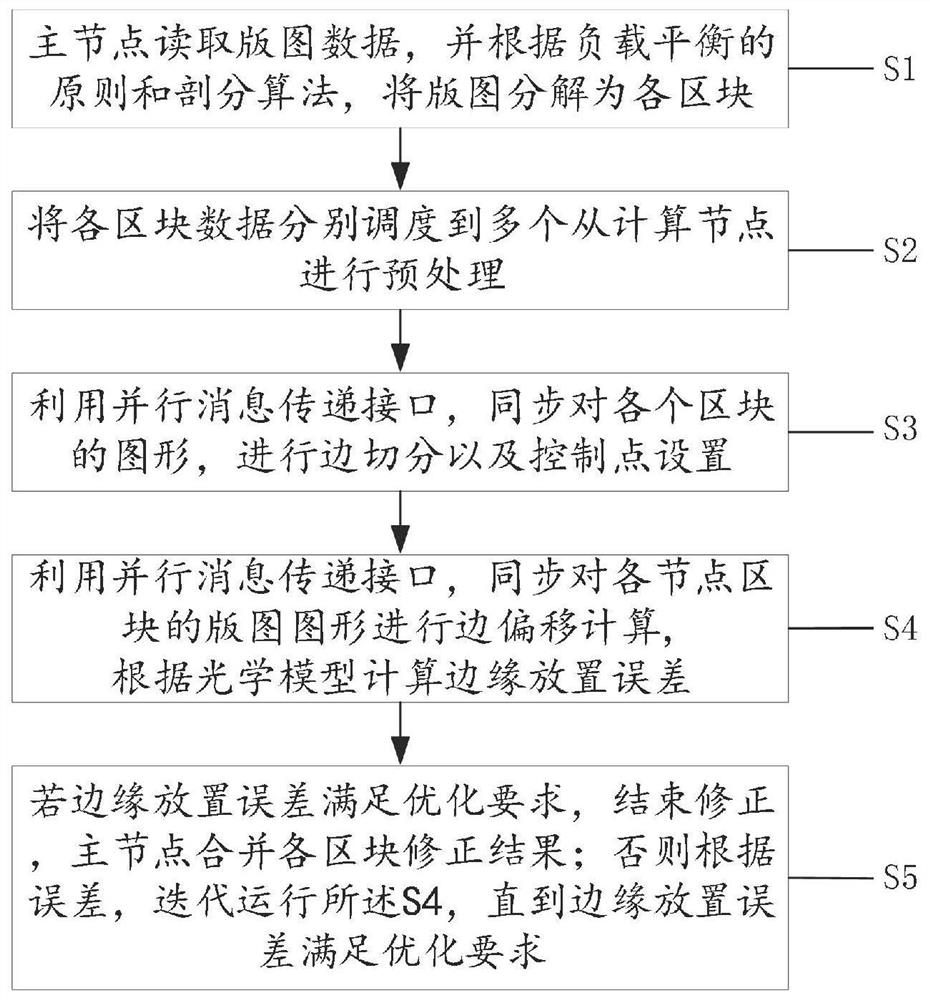

A technology of optical proximity correction and parallel processing, which is applied in the direction of originals, optics, and optomechanical equipment for optomechanical processing. It can solve the problem of large correction errors at the boundaries of overlapping regions, reduced correction speed, and data that do not meet the mask requirements. Problems such as manufacturing rules can save computing resources and time, improve speed, and avoid correction of boundary problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

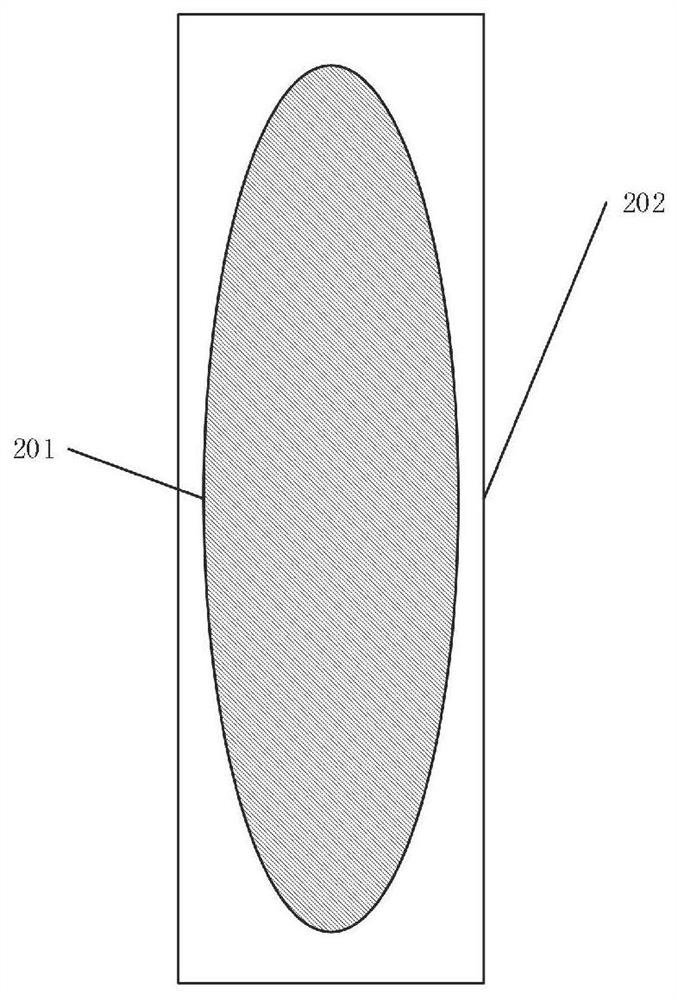

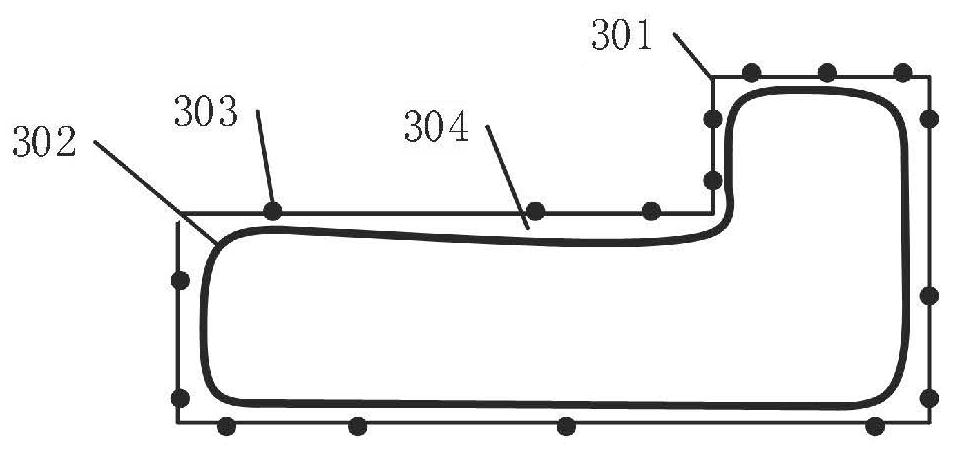

[0036] It should be noted that in semiconductor manufacturing, an important step in the chip process is the use of photolithography. The pattern "negative" used in these steps is called a mask. An opaque graphic mask is masked, so underlying erosion or diffusion will only affect areas outside the selected area. In the field of integrated circuits, feature size refers to the smallest dimension in a semiconductor device. The smaller the feature size, the higher the integration level of the chip. However, in practice, the wavelength of the light source of the existing lithography system is usually much larger than the feature size of the integrated circuit, that is, the resolution of the lithography system is not enough, resulting in serious distortion of the manufactured graphics due to light interference and diffraction effects, and finally processed on the silicon wafer. Lithographic patterns are different from design patterns. Compared with the original layout, the imaging ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com