Shield gate groove type field effect transistor and preparation method thereof

A field effect transistor and shielded gate technology are applied in the field of shielded gate trench type field effect transistors and their preparation, and can solve the problems of increased breakdown voltage and the like

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0045] In traditional trench-type shielded gate transistors, because the doping concentration of the shielded gate structure is heavily doped, when the device is in forward blocking, the electric flux of ionized donor charges in the withstand voltage region tends to concentrate on the corner of the shielded gate. , so the larger peak electric field limits the increase in breakdown voltage.

[0046] In view of the above problems, an embodiment of the present application provides a shielded gate trench type field effect transistor, which can effectively improve the peak electric field introduced by the electric field concentration effect caused by the small curvature radius at the corner of the shielded gate.

[0047] The technical solutions of the embodiments of the present application are described in detail below with reference to the accompanying drawings.

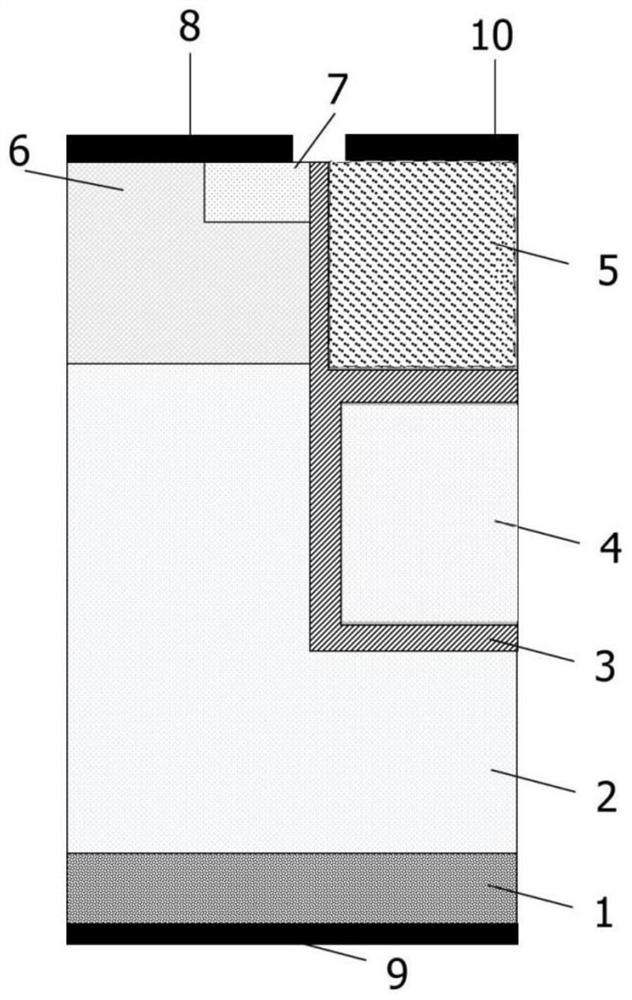

[0048] figure 1 It is a schematic diagram of the first structure of the shielded gate trench type field effect transi...

Embodiment 2

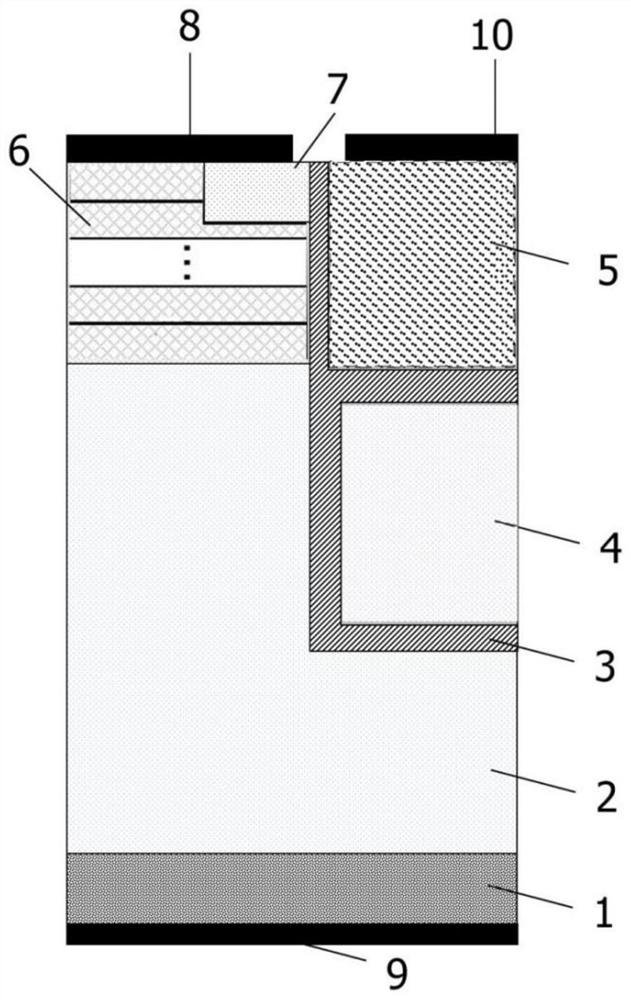

[0062] The first embodiment above provides a shielded gate trench field effect transistor. By adjusting the original heavily doped polysilicon type shielded gate structure, the peak electric field at the corner of the shielded gate is eliminated, and the polysilicon with reduced doping concentration is used It can withstand the built-in potential between the P-type polysilicon and the N-type drift region, which can reduce the lateral depletion formed between the two, thereby reducing the specific on-resistance of the device drift region, but when the breakdown voltage is less than 300V, Especially when the breakdown voltage is less than 100V, even less than 40V, the channel region and the drift region have comparable specific on-resistance. Therefore, for low-voltage shielded gate trench field effect transistors, the channel The improvement of the specific on-resistance of the channel region is as important as the design of the drift region. Therefore, the embodiment of the pr...

Embodiment 3

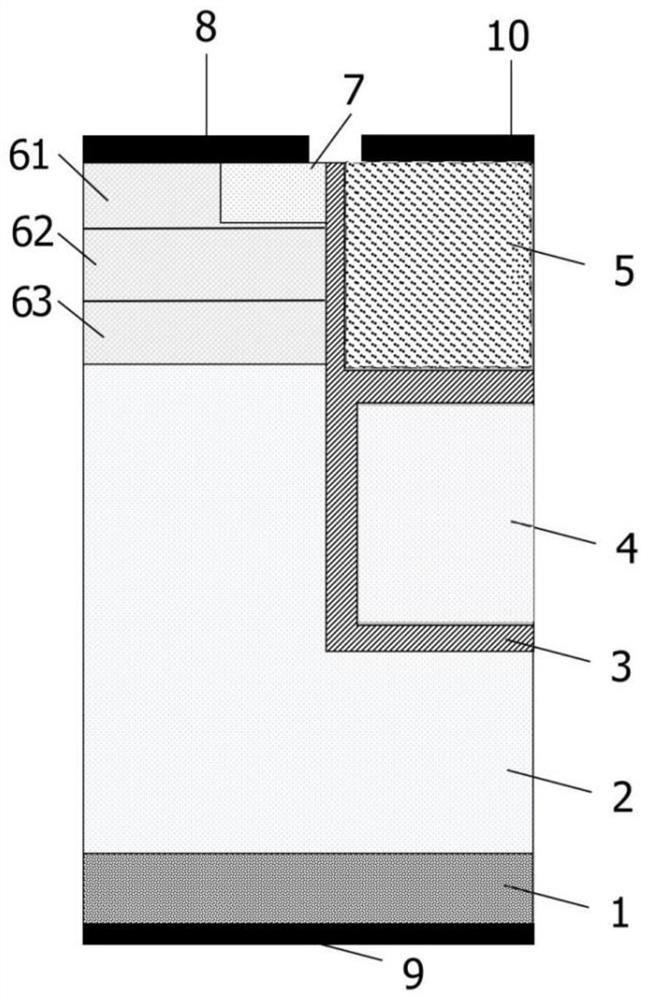

[0073] Based on the shielded gate trench field effect transistor shown in the second embodiment above, the embodiment of the present application provides a shielded gate trench field effect transistor having three doping distribution layers distributed at equal intervals.

[0074] see image 3 , the shielded gate trench field effect transistor, comprising: a substrate region 1, a drift region 2, a shielded gate 4, a control gate 5, a base region 6, a source region 7, an insulating layer 3, a source electrode 8, and a drain electrode 9 and a metal grid 10;

[0075] Wherein, the drift region 2 , the base region 6 , the source region 7 and the source 8 are sequentially disposed above the substrate region 1 , and the drain 9 is disposed below the substrate region 1 , the control gate 5 and the shielding gate 4 are arranged on the same side of the drift region 2 from top to bottom, and the control gate 5 is respectively connected to the base region 6 and the source through the ins...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Doping concentration | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More