A silicon carbide mosfet cell layout structure with integrated gated diode

A gate-controlled diode and layout structure technology, applied in transistors, electrical components, semiconductor devices, etc., can solve the problems of high conduction voltage drop of SiC body diodes, high JFET area density, and increased dynamic loss of devices, so as to improve long-term reliability performance, low on-resistance, increased current capability and robustness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The following combined with the attached figures, the principle and characteristics of the present invention are described. The examples are used to explain the present invention, not to limit the scope of the present invention.

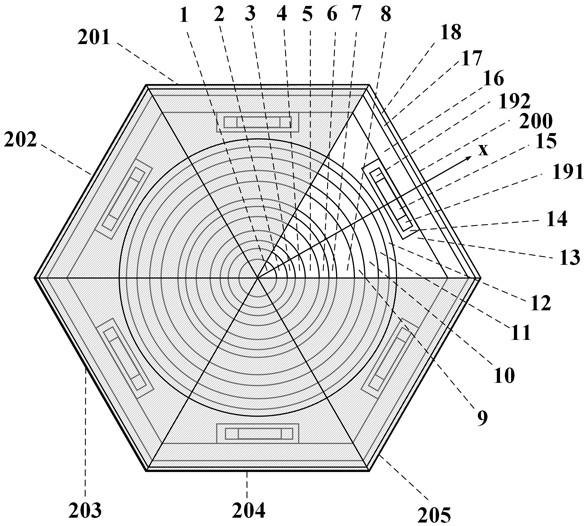

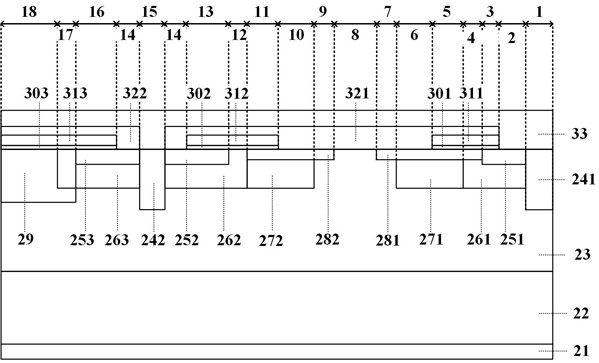

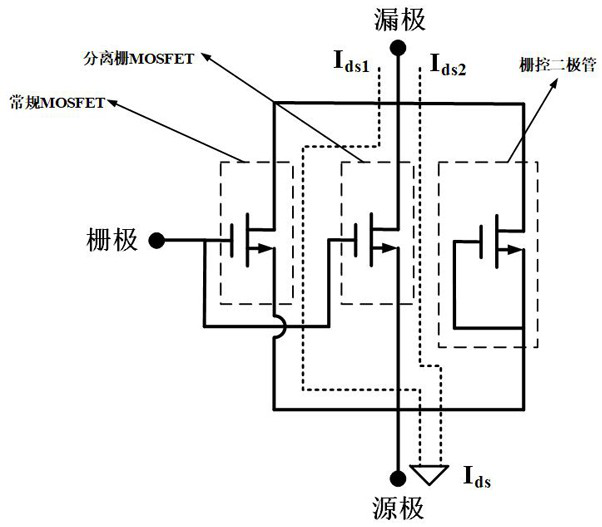

[0039] like figure 1 所示,本实施例提供一种集成栅控二极管的碳化硅MOSFET元胞版图结构,包括第一区域1,第二区域2,第三区域3,第四区域4,第五区域5,第六Area 6, Seventh Region 7, Eighth Region 8, Ninth Region 9, Tenth Region 10, Eleventh Region 11, Twelfth Region 12, 13th Region 13, 14th Area 14, Fifteenth, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th, 15th Area 15, 16 areas 16, 17 areas 17, eighteenth area 18, 191 area 191, 192 area 192, 201 area 201, 202 area 202, No. 1, No. 1 203, 203, 204, 204, 205 areas 205.

[0040] The first area 1 is a fan of 60 degrees in the inner angle; the second region 2, the third region 3, the fourth region 4, the fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More