Patents

Literature

72results about How to "Increase channel density" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

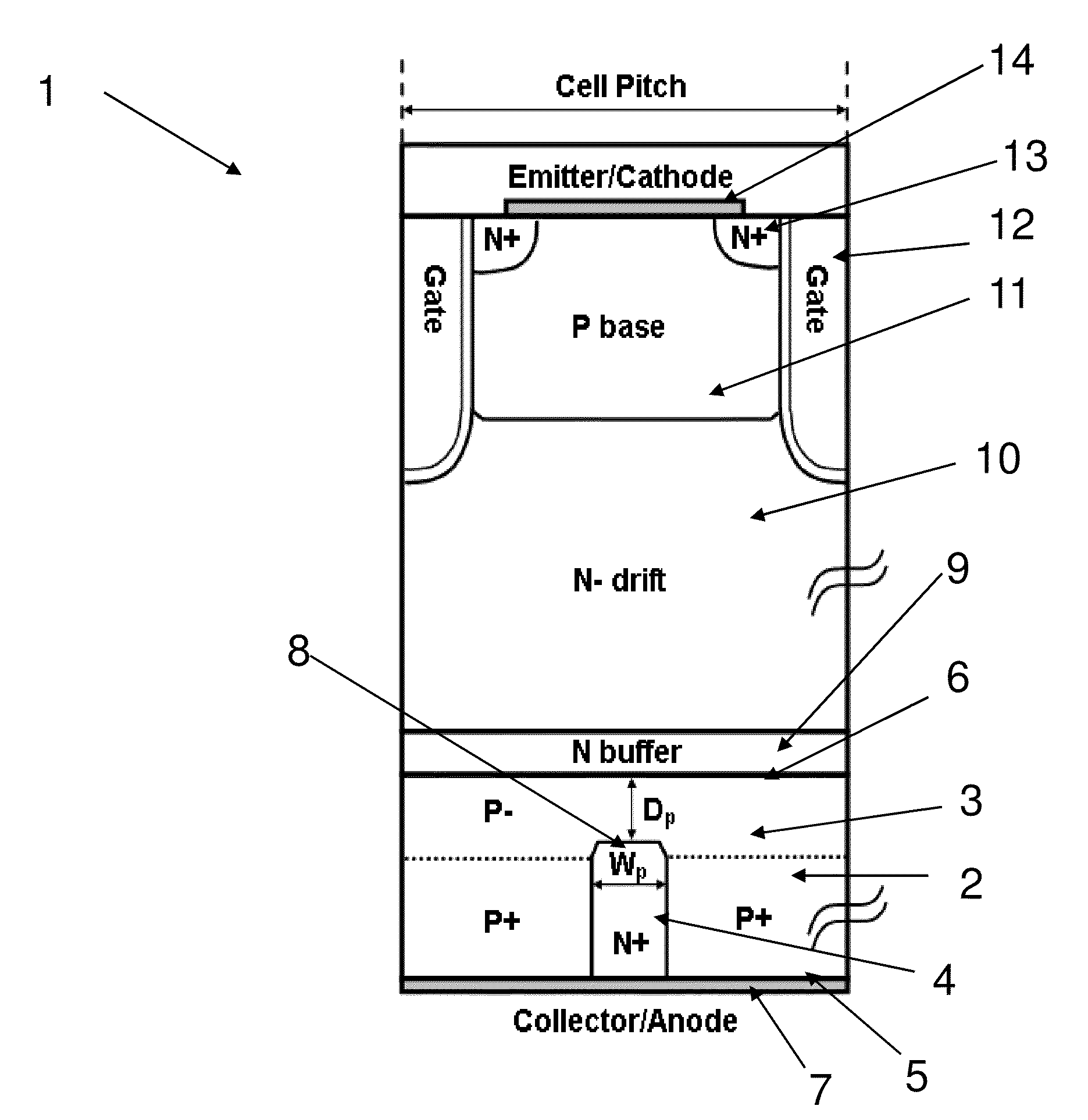

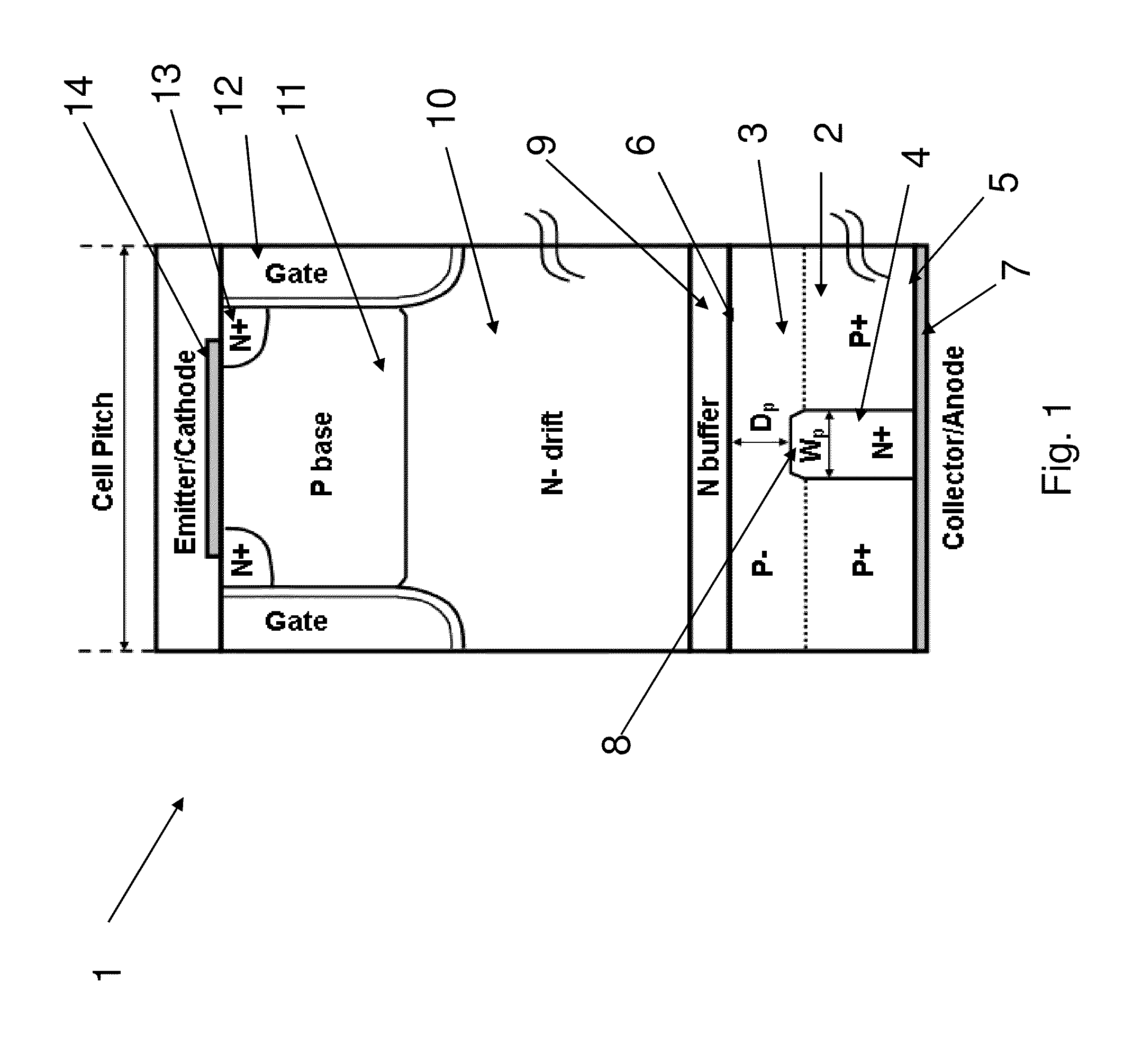

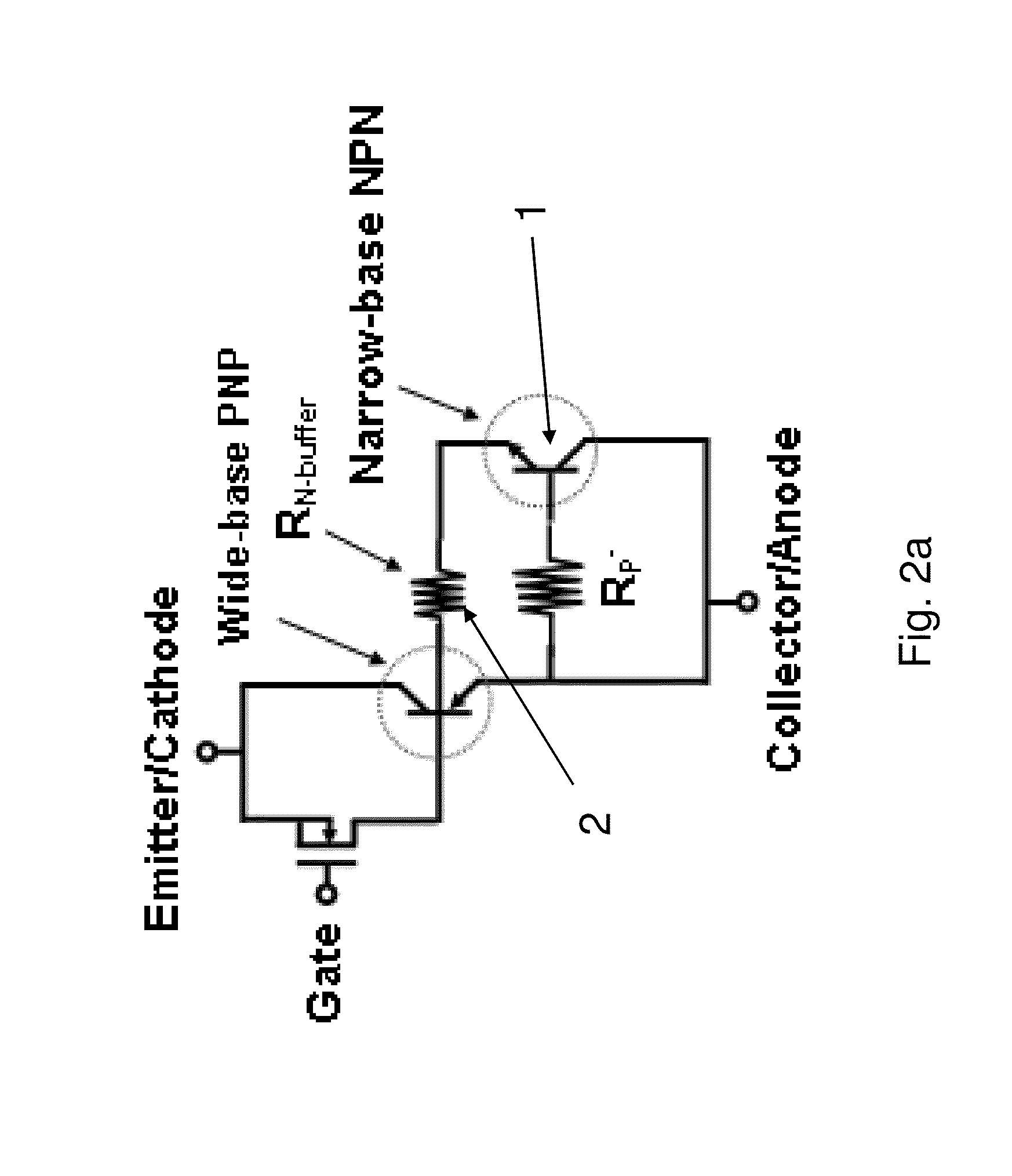

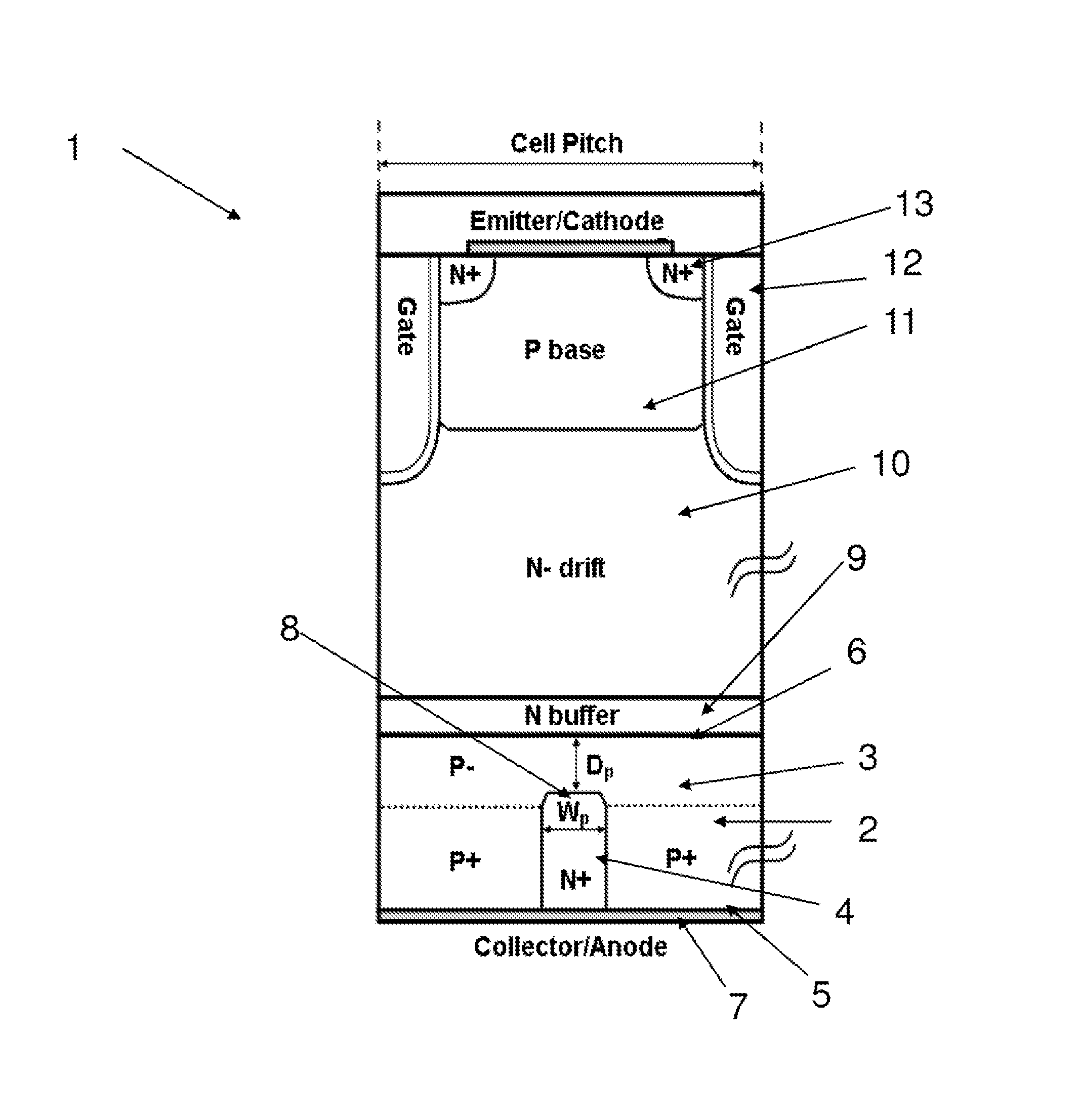

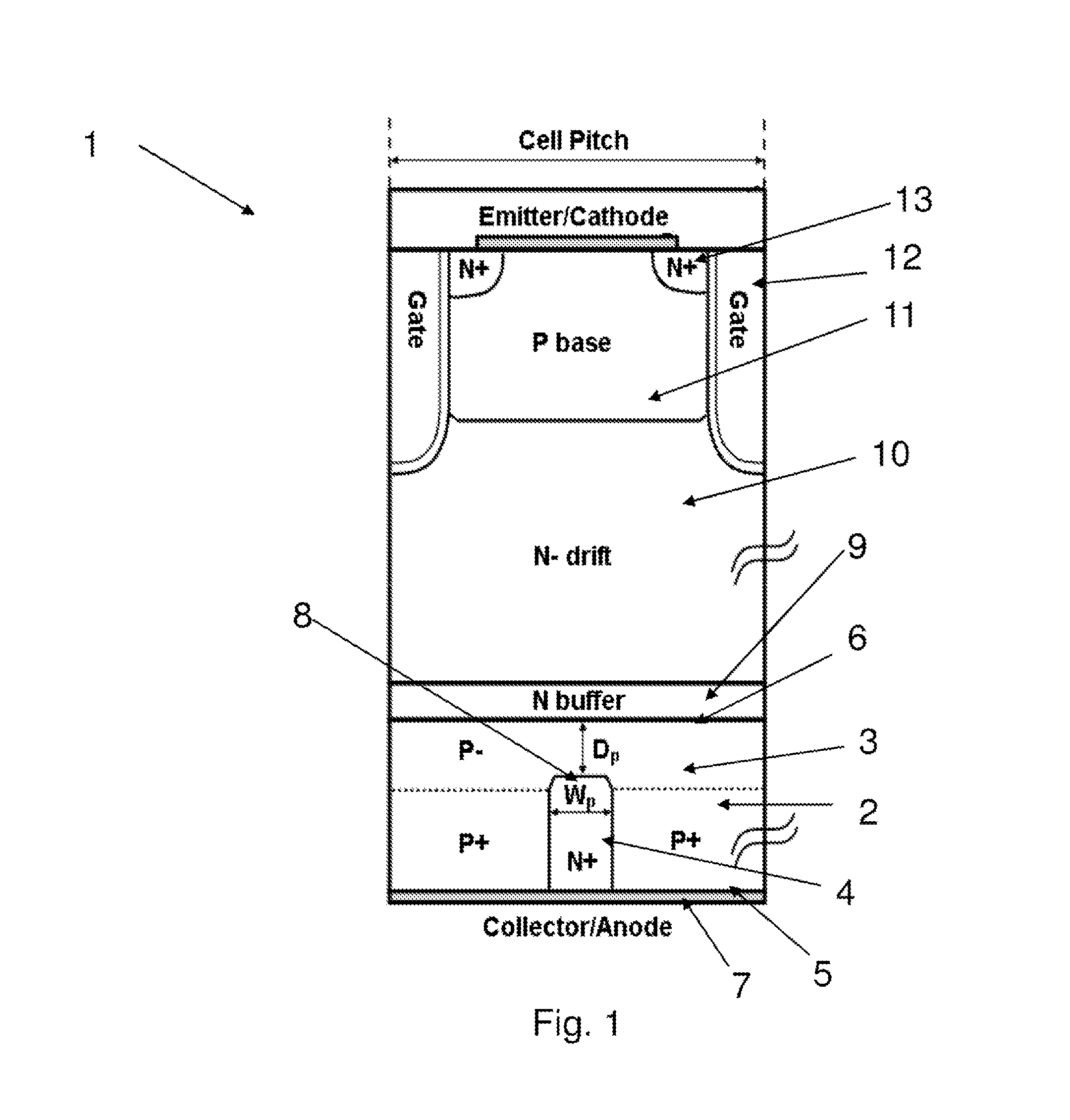

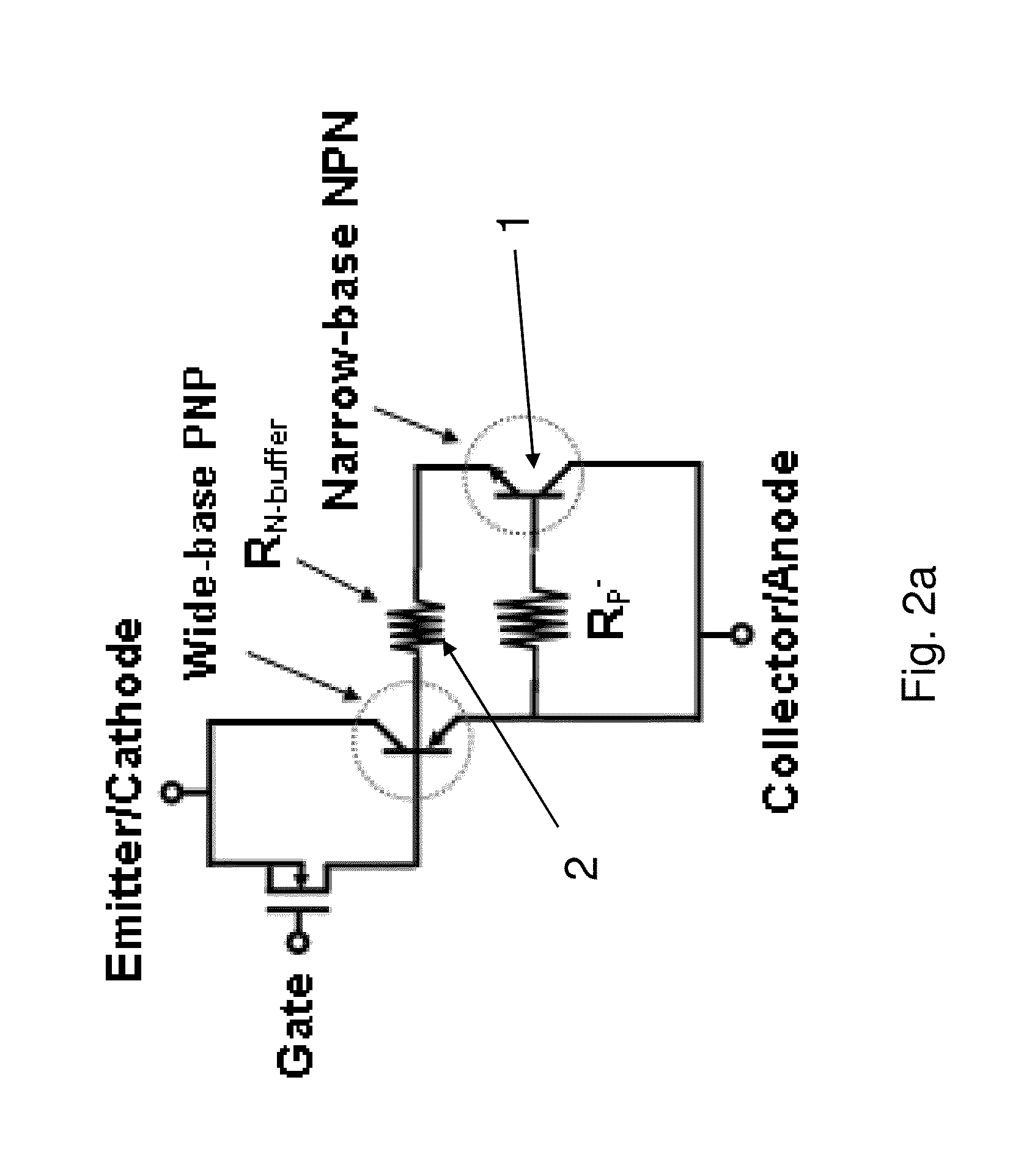

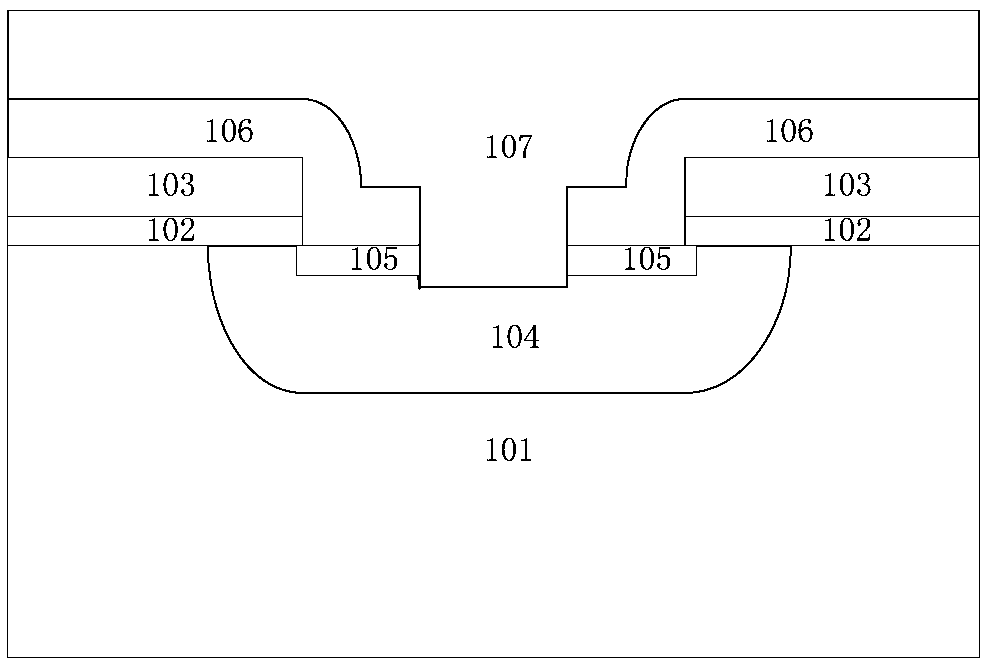

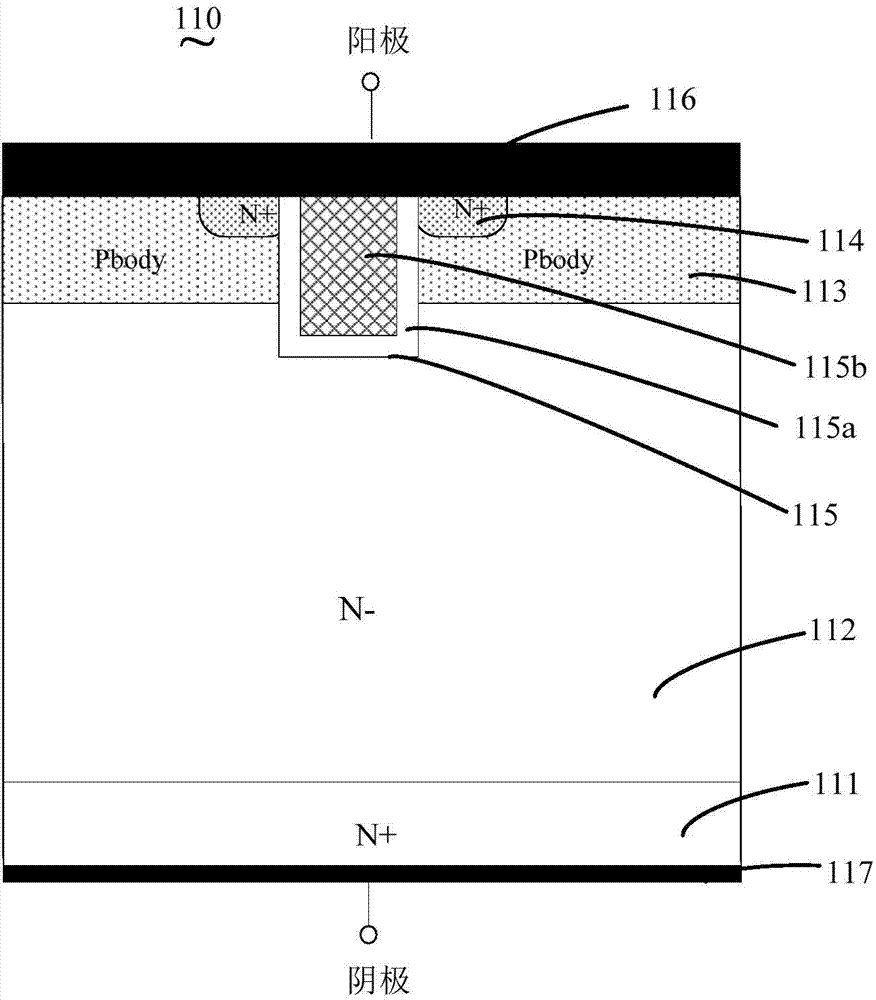

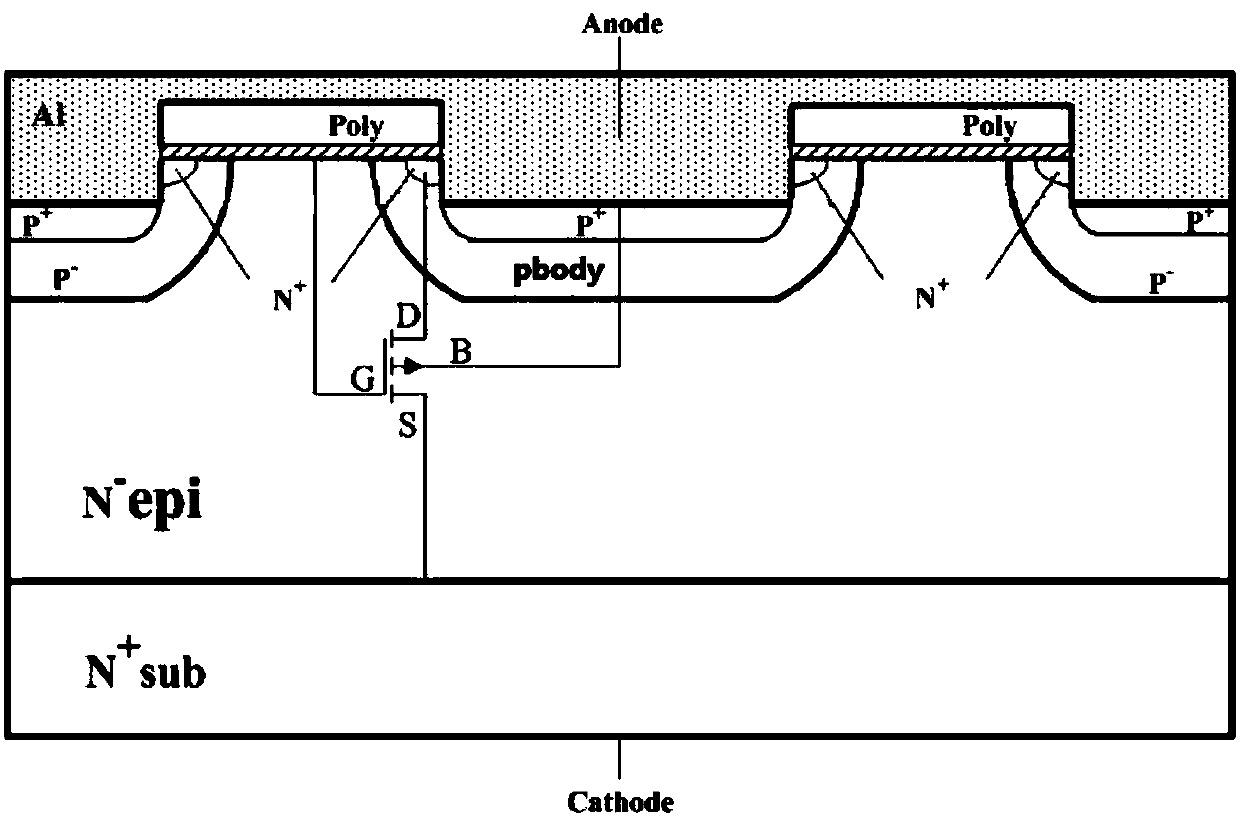

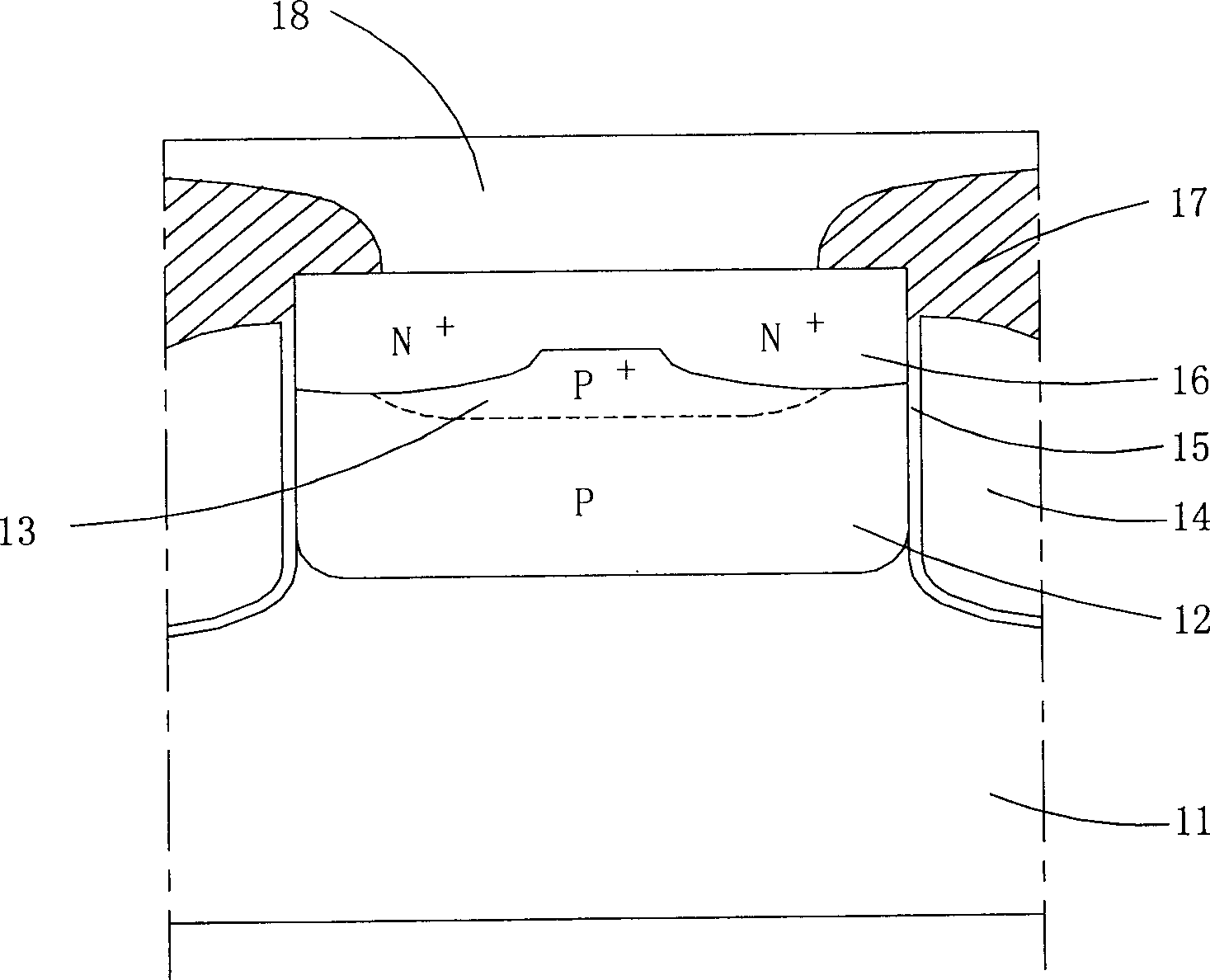

Reverse conducting IGBT

InactiveUS20110254050A1Simple and cost-effectiveHigh densityTransistorThyristorThyratronSemiconductor

An insulated gate bipolar transistor (IGBT) is provided comprising a semiconductor substrate having the following regions in sequence: (i) a first region of a first conductive type having opposing surfaces, a column region of a second conductive type within the first region extending from a first of said opposing surfaces; (ii) a drift region of the second conductive type; (iii) a second region of the first conductive type, and (iv) a third region of the second conductive type. There is provided a gate electrode disposed to form a channel between the third region and the drift region, a first electrode operatively connected to the second region and the third region, a second electrode operatively connected to the first region and the column region. The arrangement of the IGBT is such that the column region is spaced from a second surface of the opposing surfaces of the first region, whereby a forward conduction path extends sequentially through the third region, the second region, the drift region, and the first region, and whereby a reverse conduction path extends sequentially through the second region, the drift region, the first region and the column region. Reverse conduction of the IGBT occurs through a thyristor structure which is embedded in the IGBT. Such an IGBT structure is advantageous over a reverse conducting IGBT structure in which an anti-parallel diode is integrated or embedded because it provides improved reverse conduction and snapback performance.

Owner:SINOPOWER SEMICON

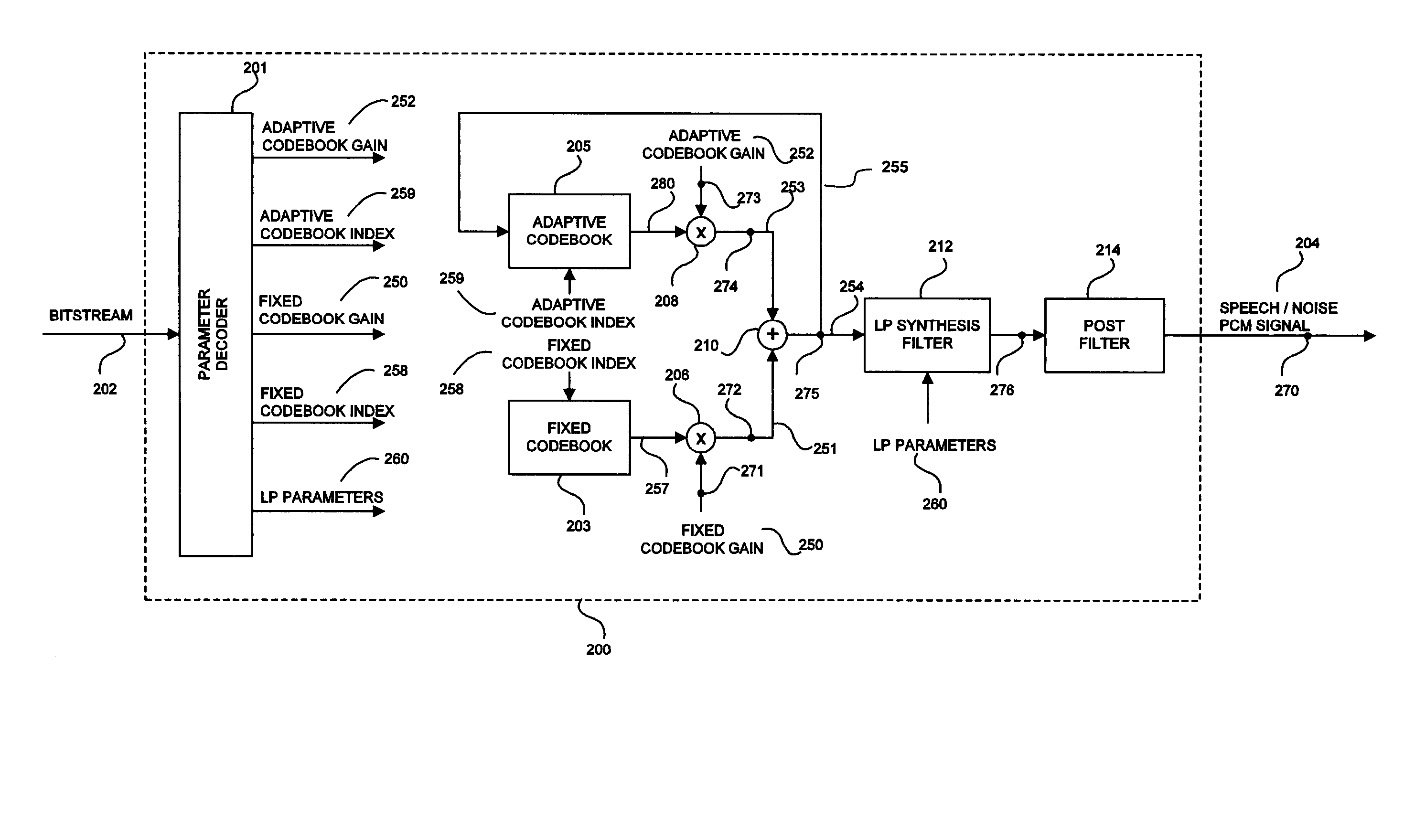

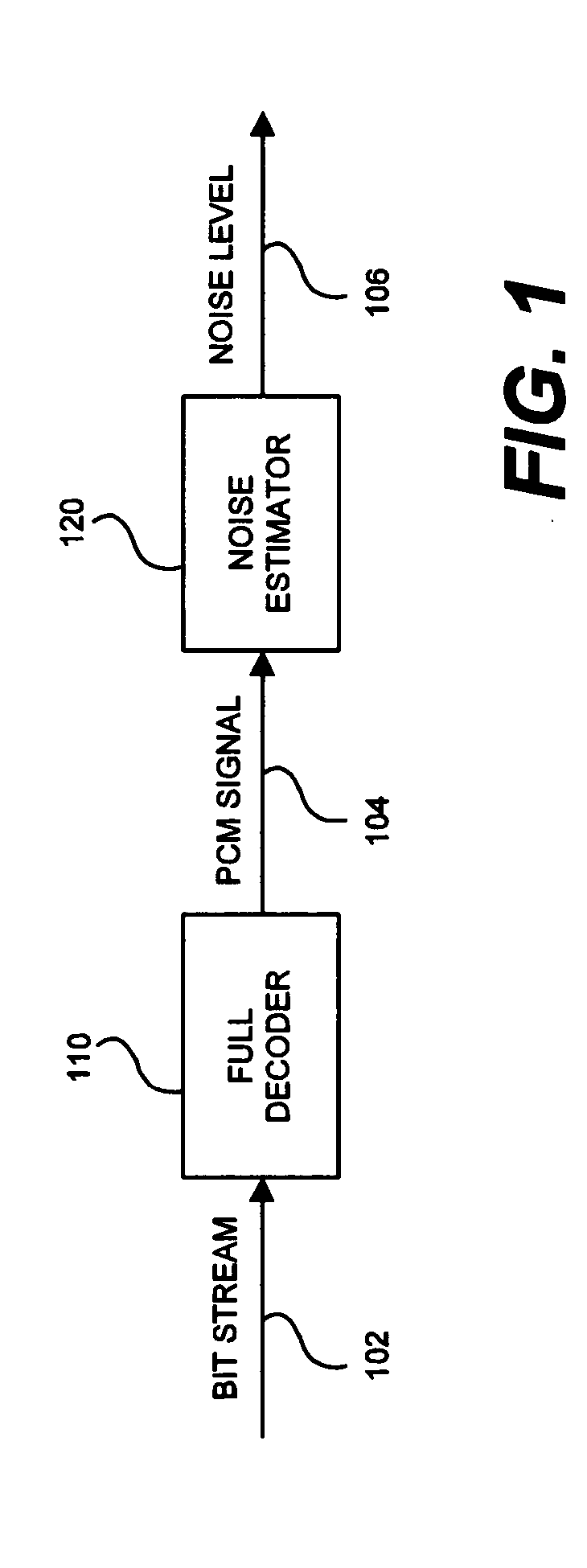

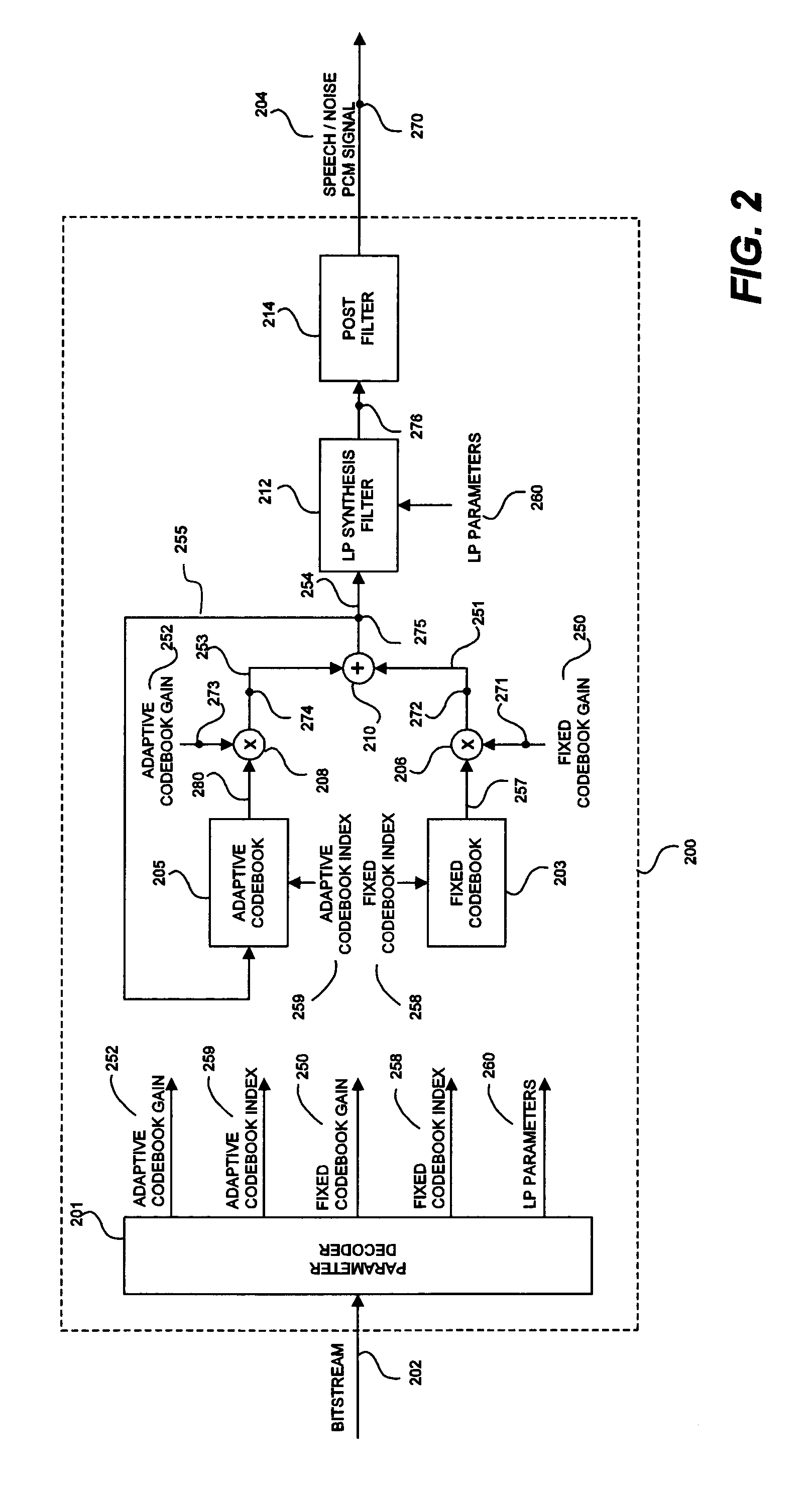

Method and apparatus for estimating noise in speech signals

InactiveUS20050071154A1Reduce computational complexityReduced Power RequirementsSpeech analysisNoise levelNoise estimation

Noise in a speech signal is estimated using only the excitation value of the speech signal. More specifically, an encoded speech signal (i.e., bit stream) is partially decoded to obtain an excitation parameter. The excitation parameter is used as input to estimate the noise level of the speech signal. In one example, the excitation parameter is the fixed codebook gain of the speech signal. The fixed codebook gain is multiplied by a scaling factor (e.g., constant value) and then used as input for noise estimation. The scaling factor can also be variable and computed as a function of adaptive codebook gain that is also obtained from the partially decoded bit stream.

Owner:LUCENT TECH INC

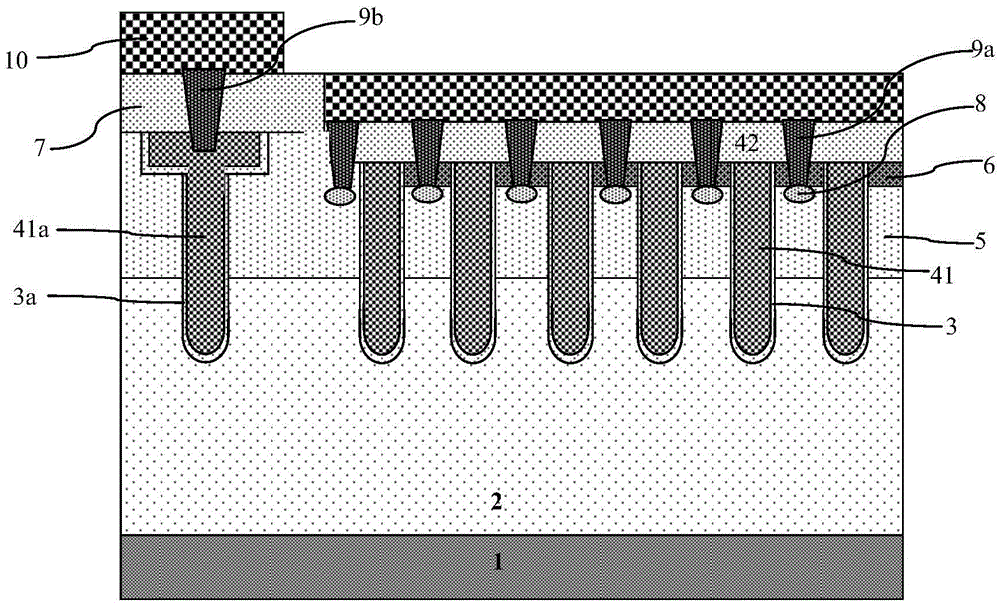

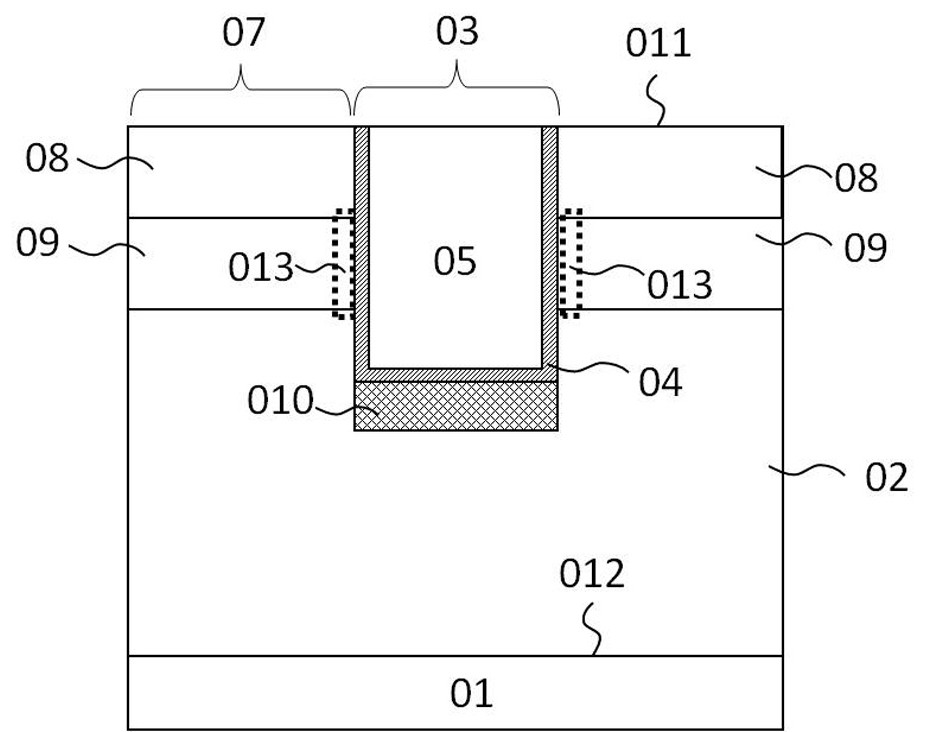

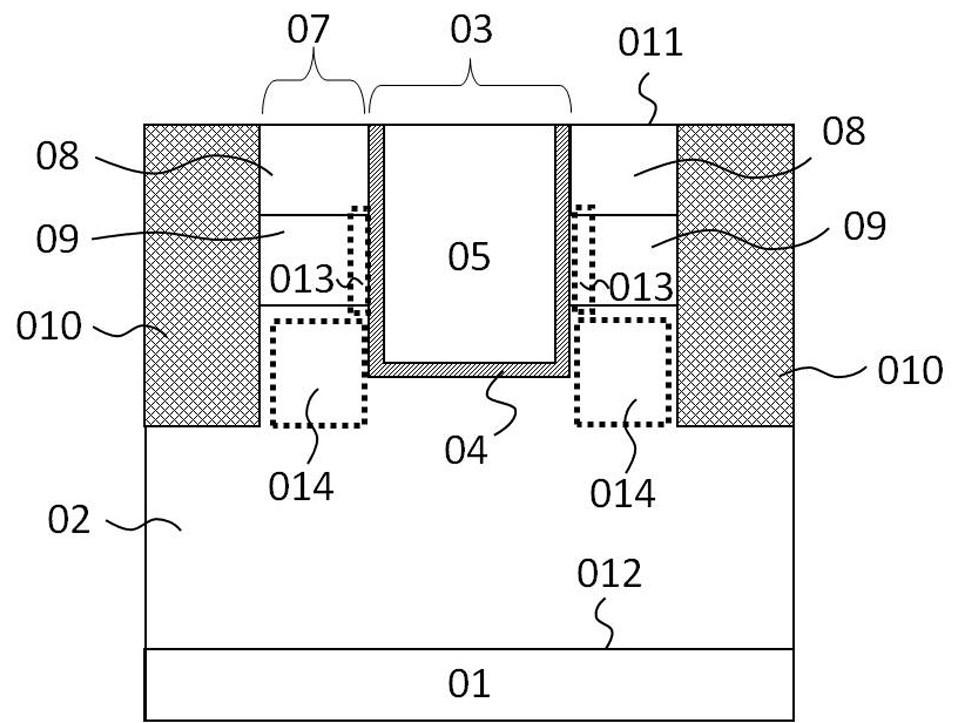

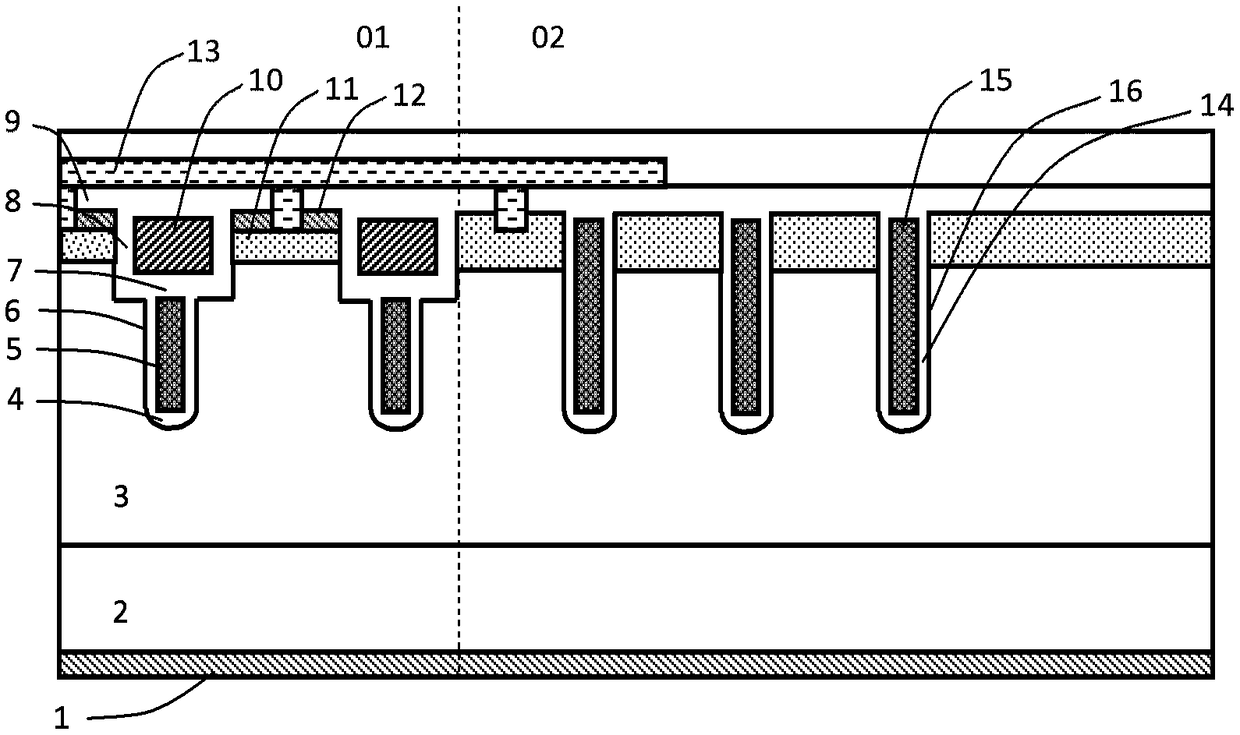

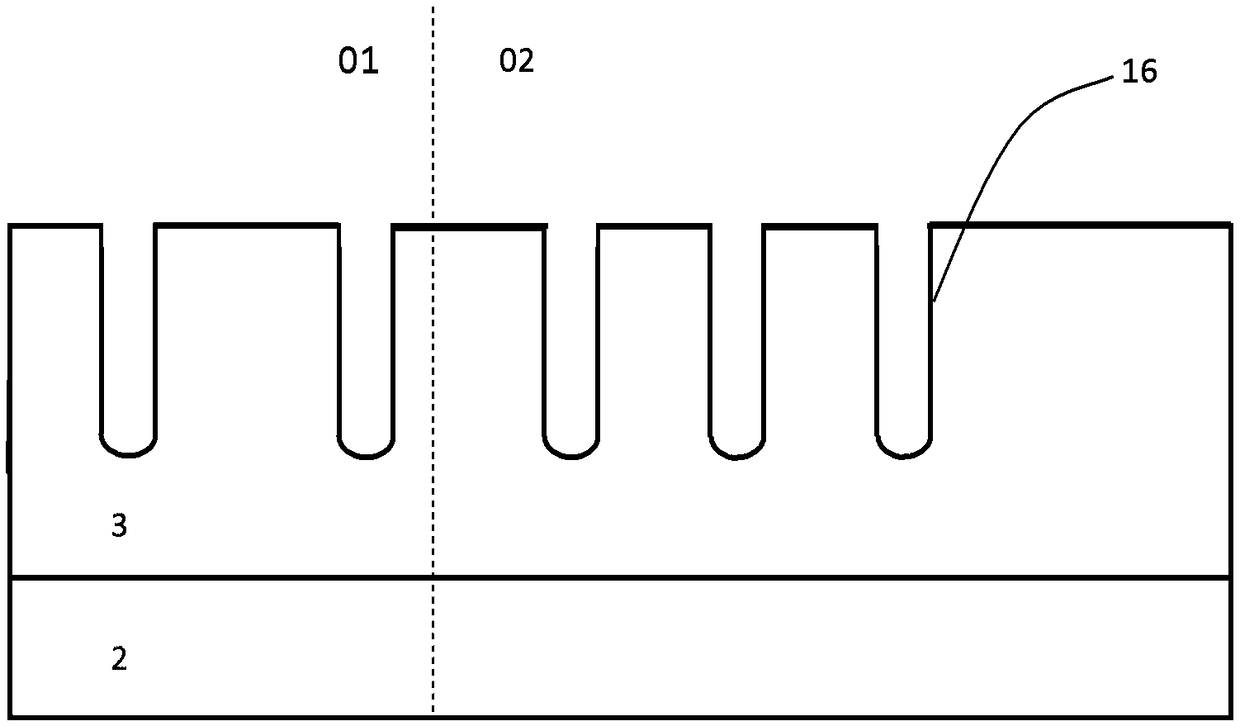

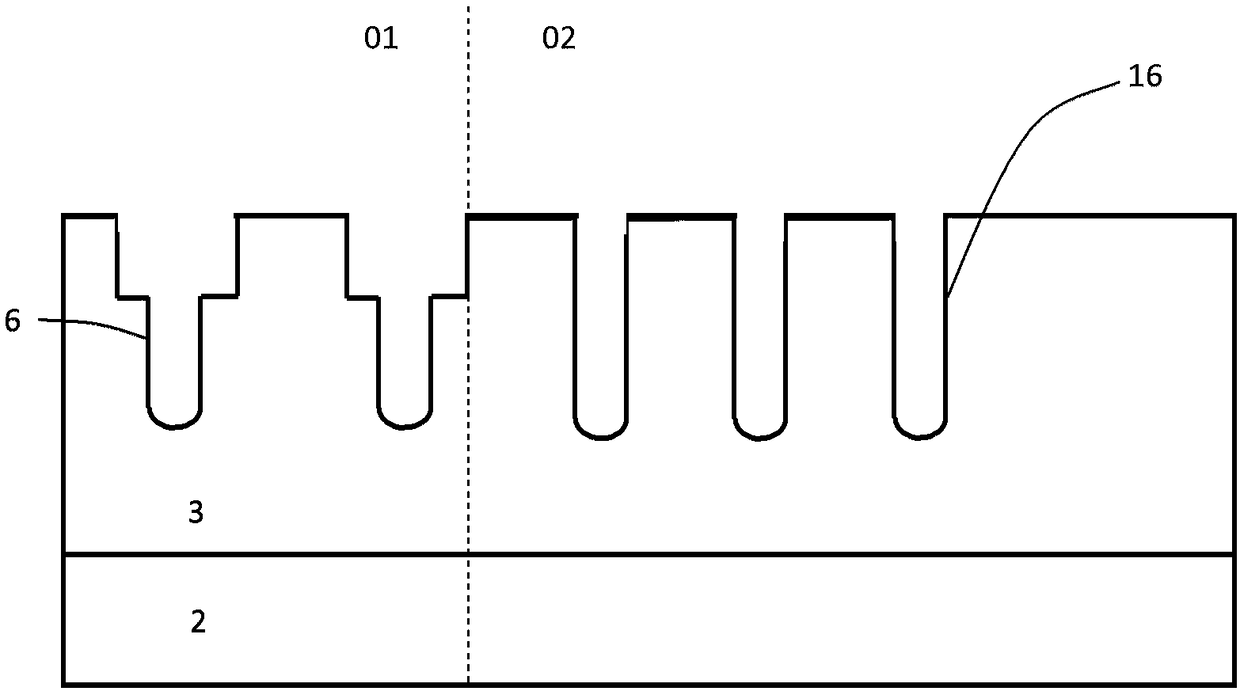

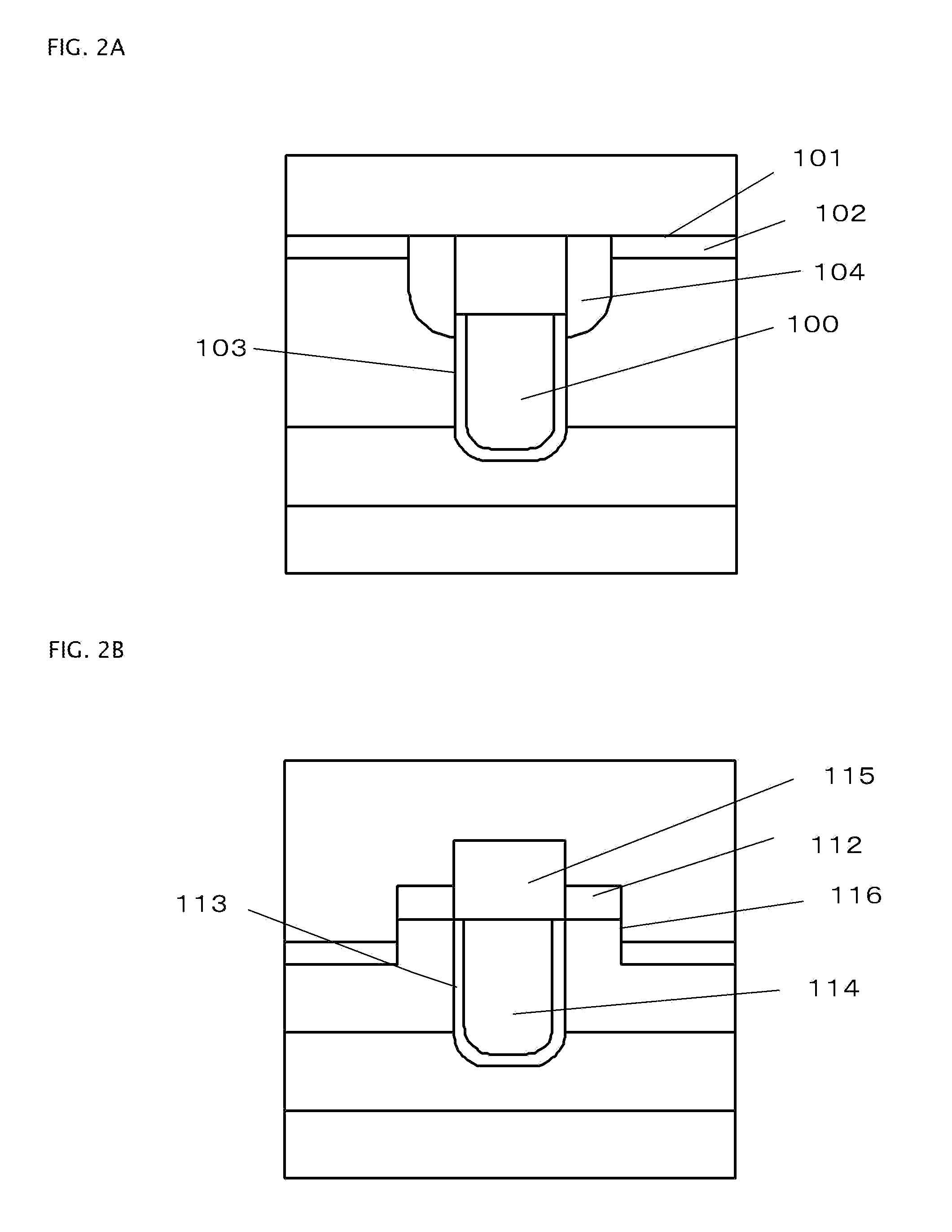

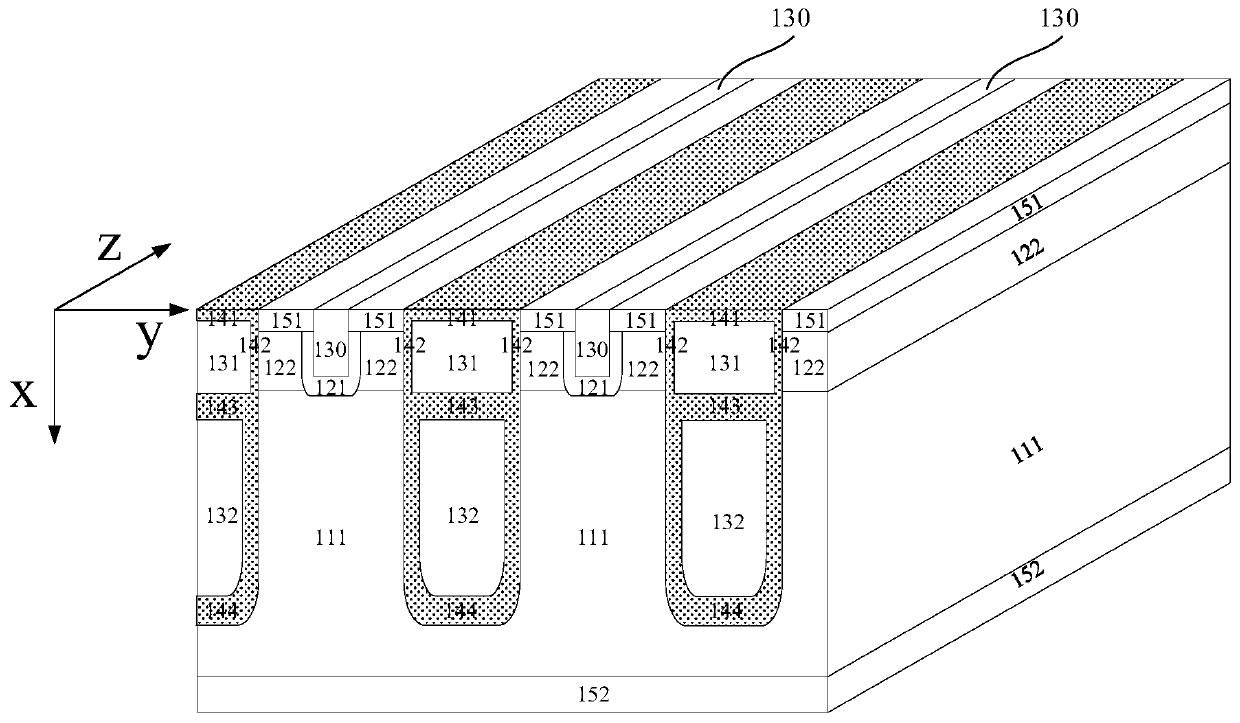

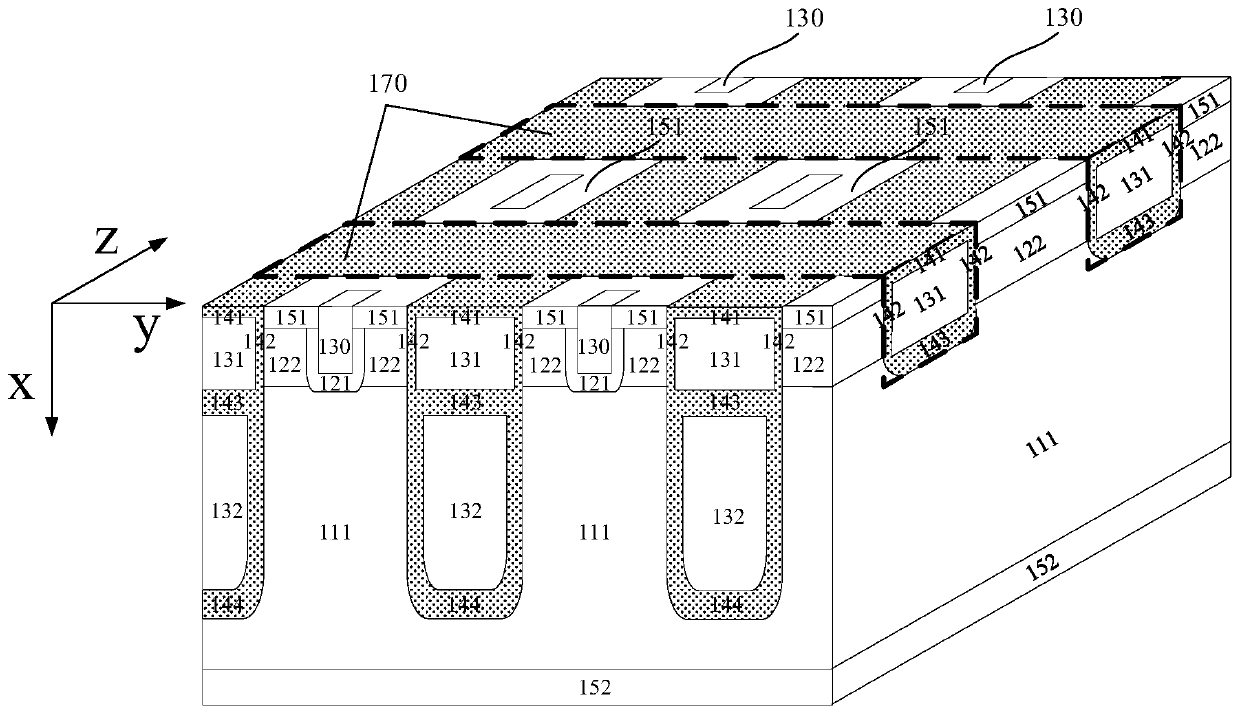

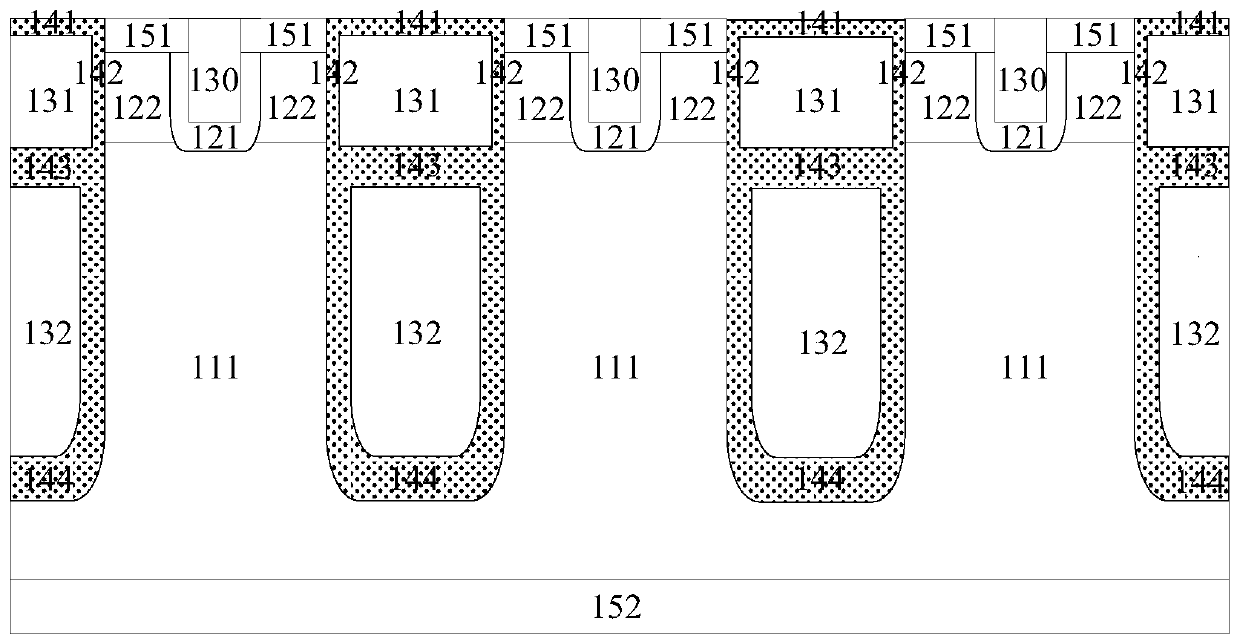

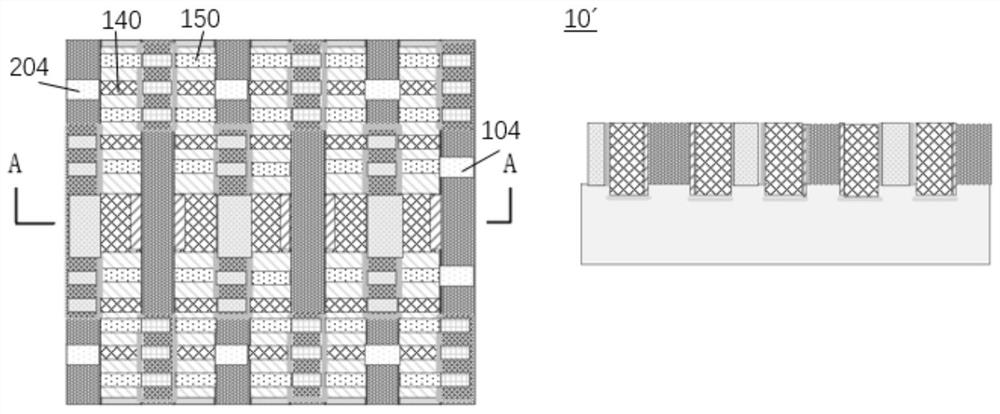

Trench gate power transistor and manufacturing method therefor

ActiveCN105470307AReduce spacingLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesDielectric layerTrench gate

The invention discloses a trench gate power transistor. The trench gate power transistor comprises a plurality of gate trenches with T-shaped structures, gate polycrystalline silicon is filled in a bottom trench of each gate trench, and a first dielectric layer is filled in a top trench of each gate trench; source regions are formed in body junction injection layers among the gate trenches; the depth of each source region is greater than that of the top trench of the corresponding gate trench; and a trench of a first contact hole in the top of each source region is formed by etching a semiconductor epitaxial layer between the first dielectric layers of the top trenches of the corresponding two adjacent gate trenches in a self-aligning manner, so that the distance between each two gate trenches can be reduced, and the density of channels is increased. Gate leading-out trenches are also T-shaped structure, a top trench of each gate leading-out trench is relatively wide, requirements of manufacturing of contact holes are met, the value of a bottom trench of each gate leading-out trench is relatively small, so that the depth of each gate leading-out trench is relatively small, and breakdown voltage of devices can be improved. The invention further discloses a manufacturing method for the trench gate power transistor.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

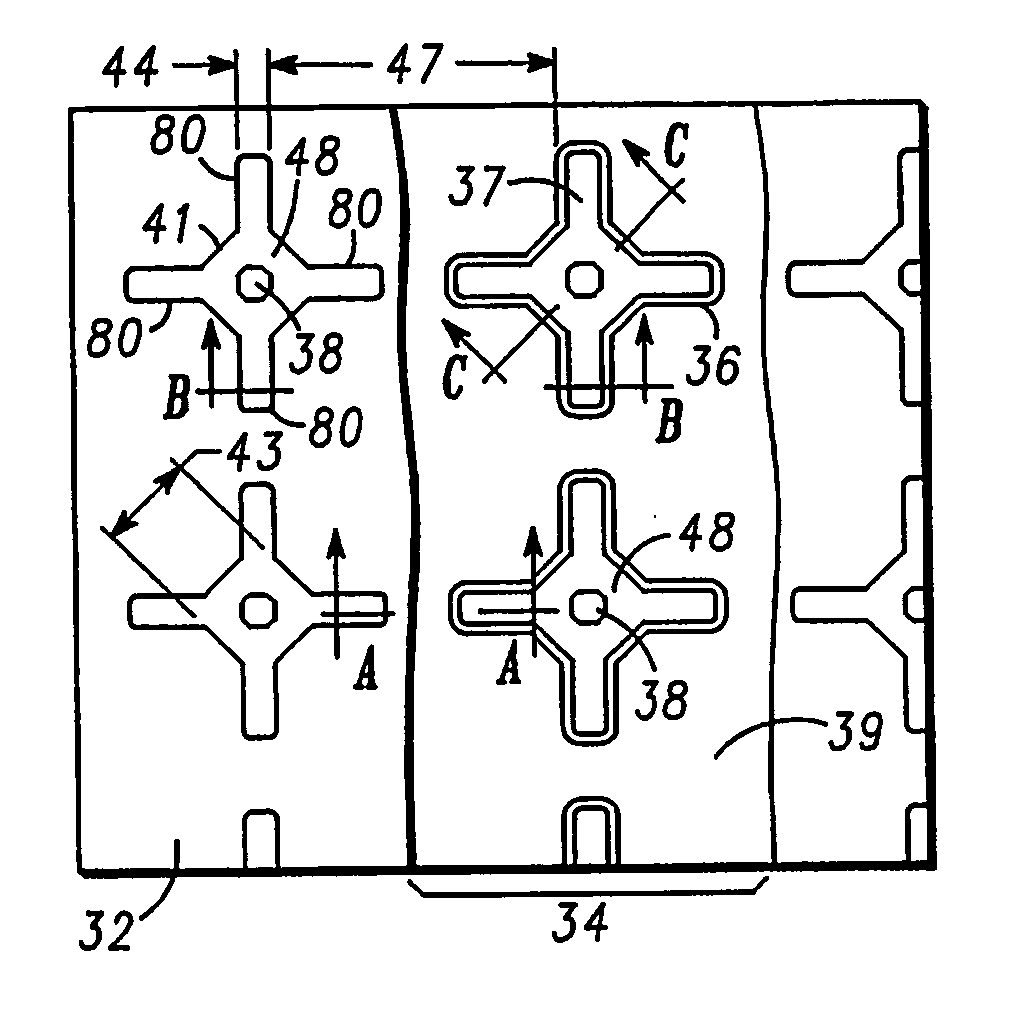

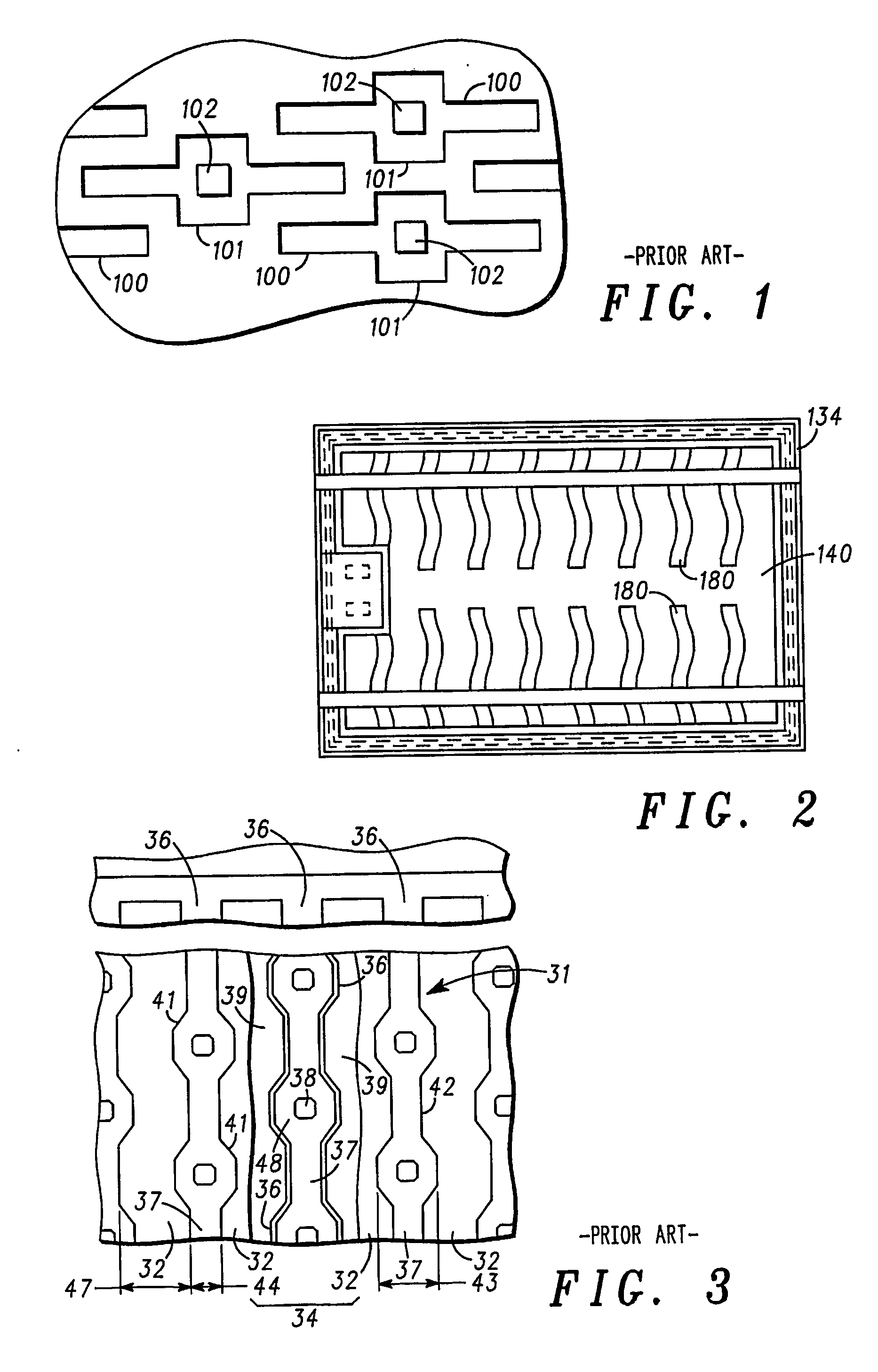

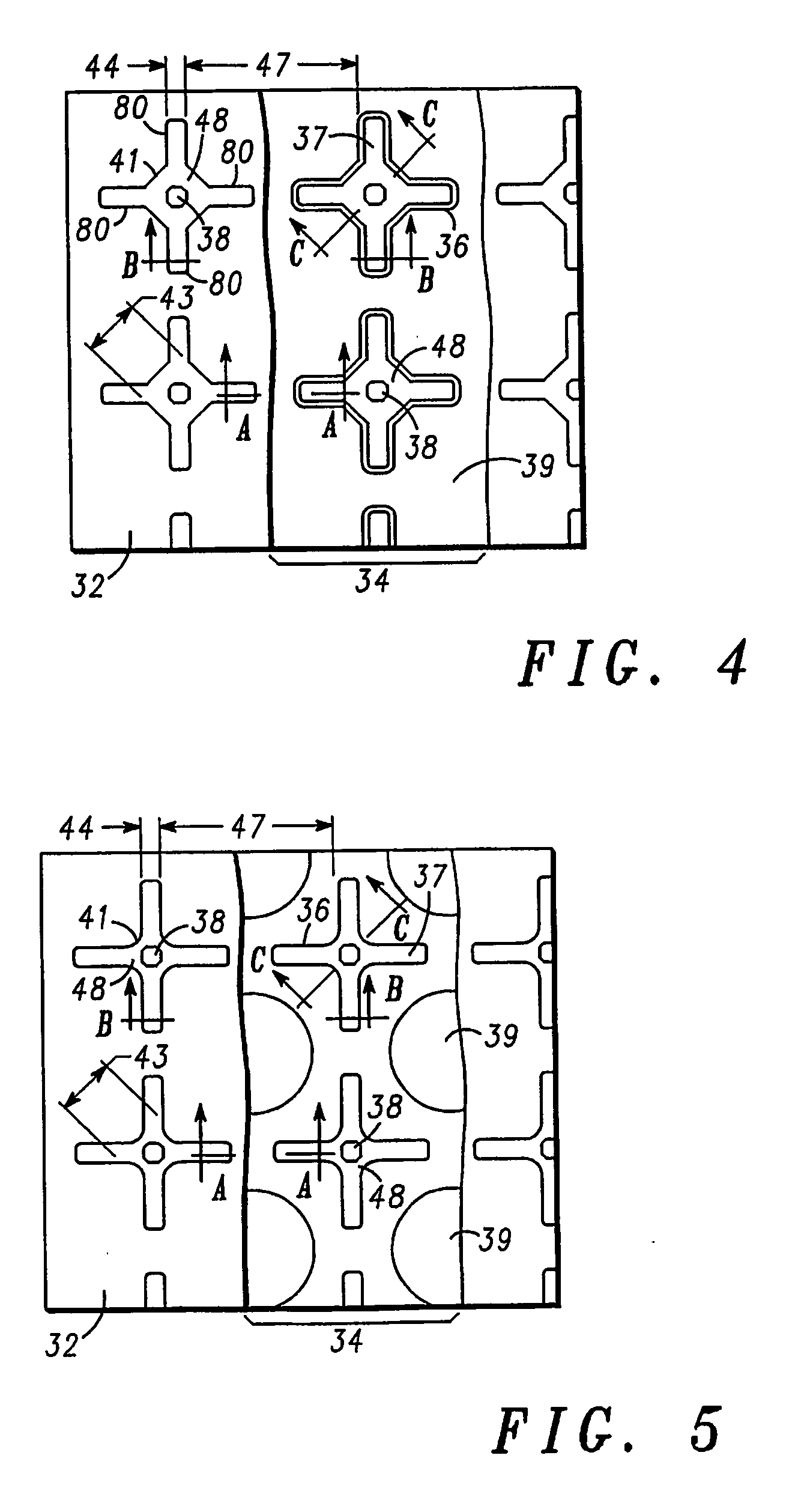

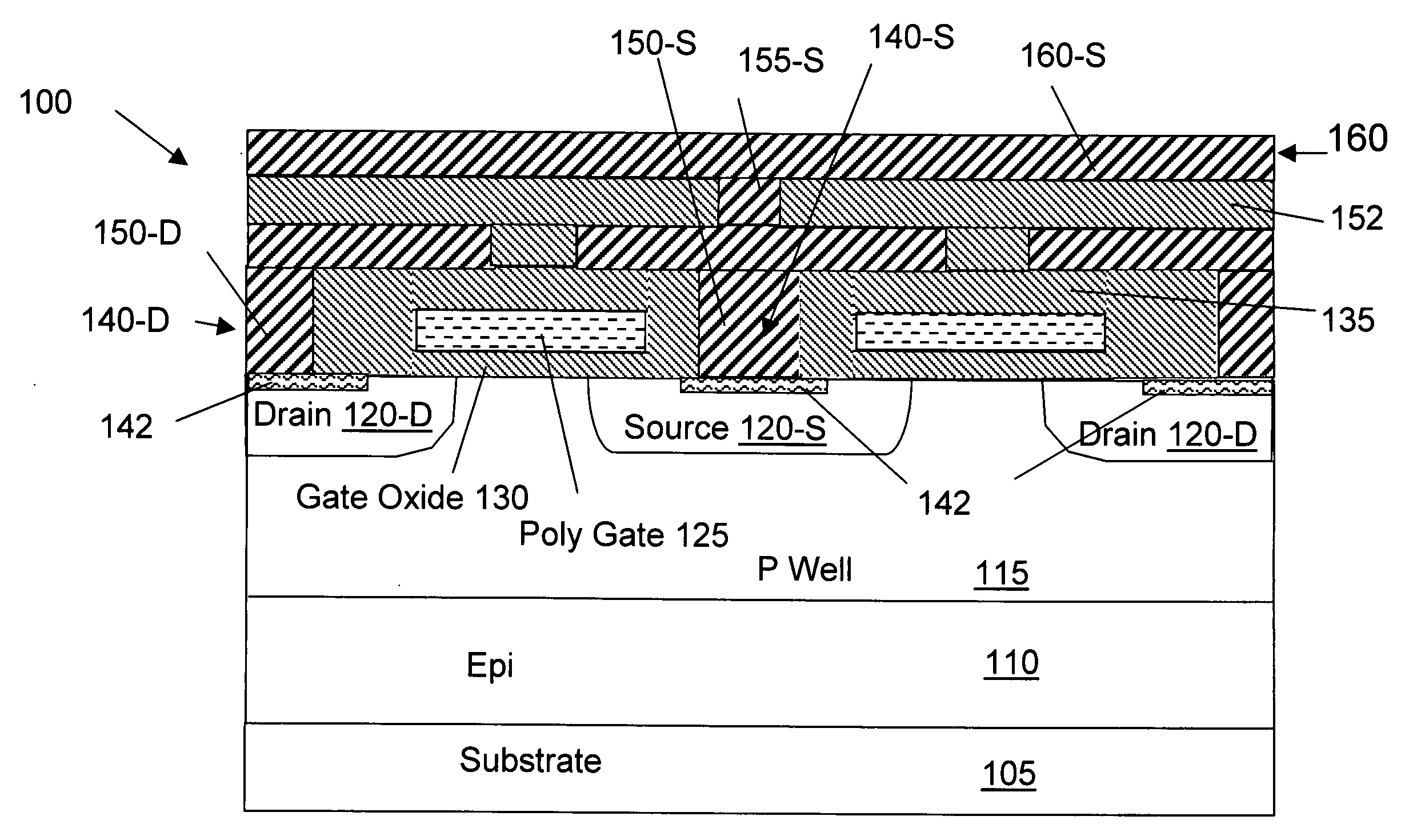

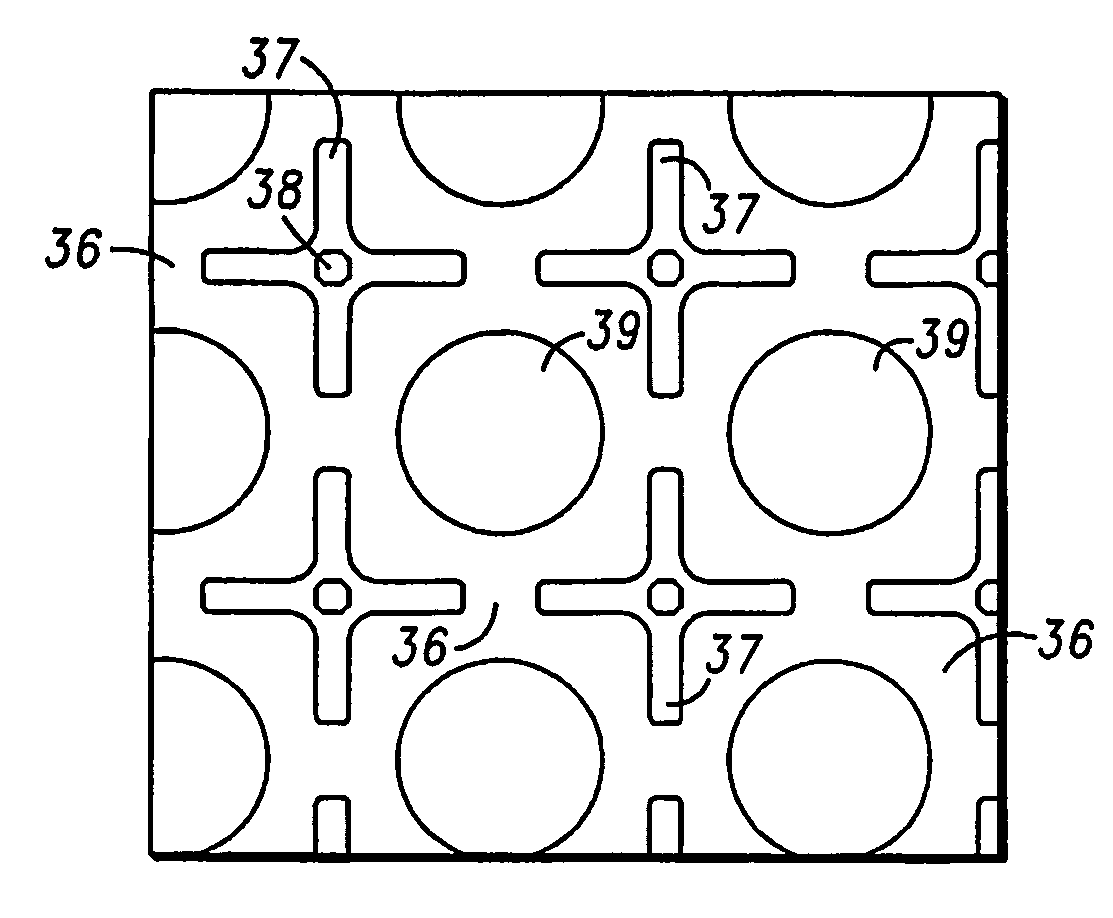

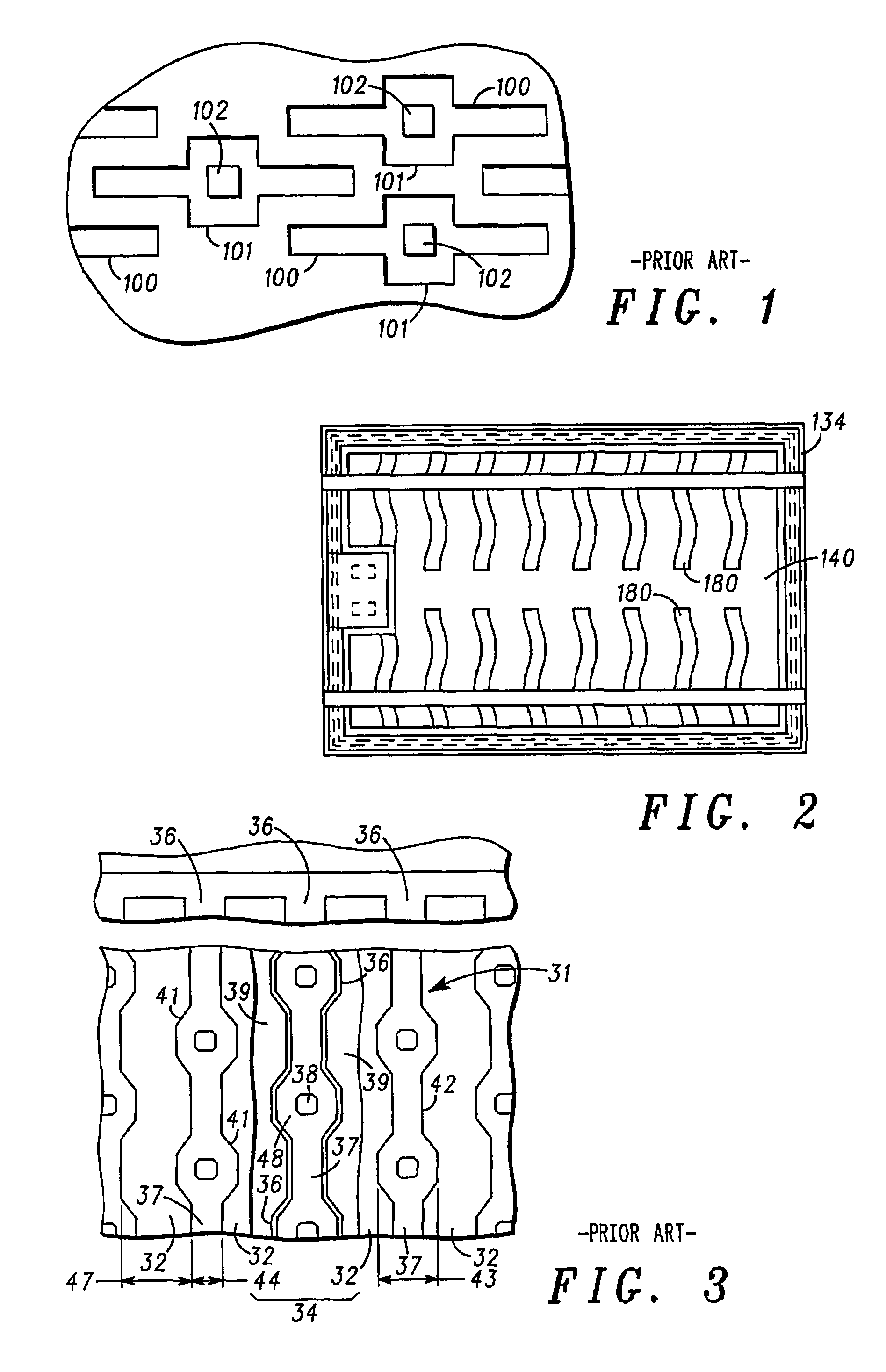

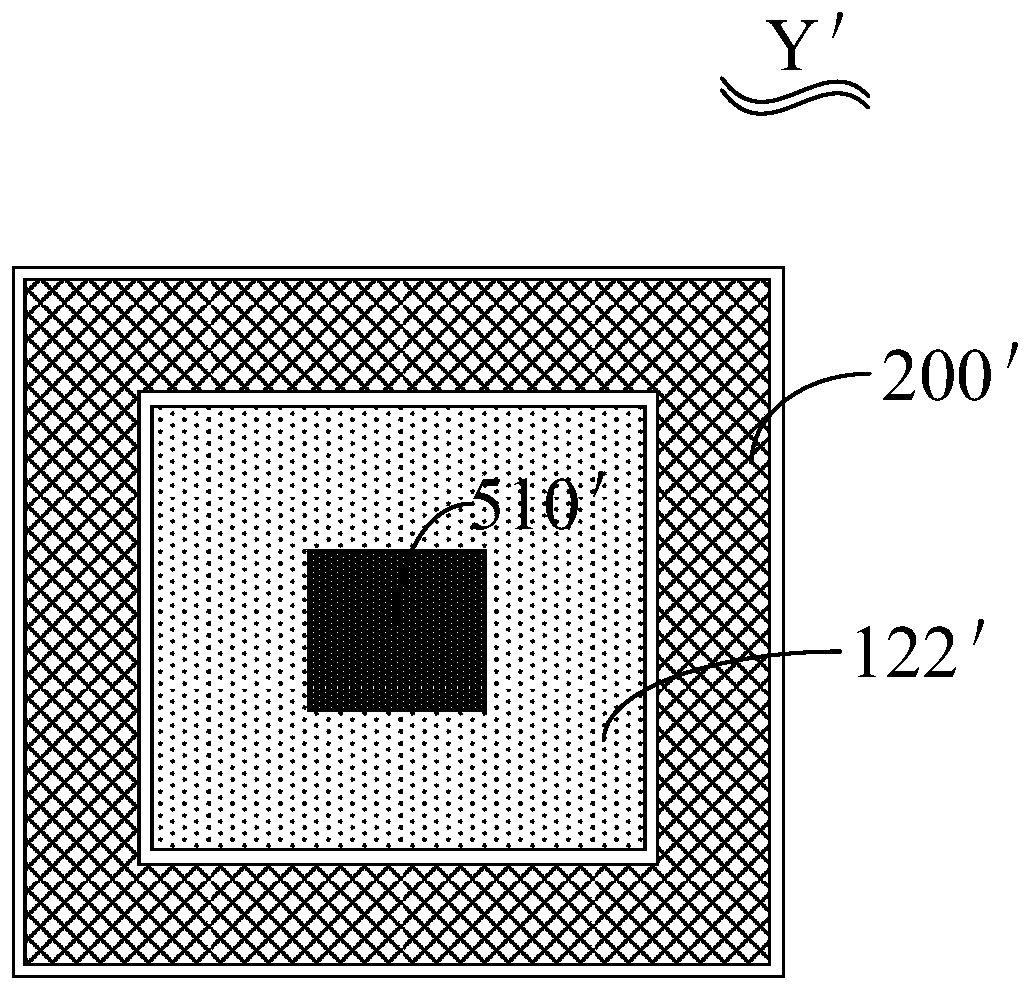

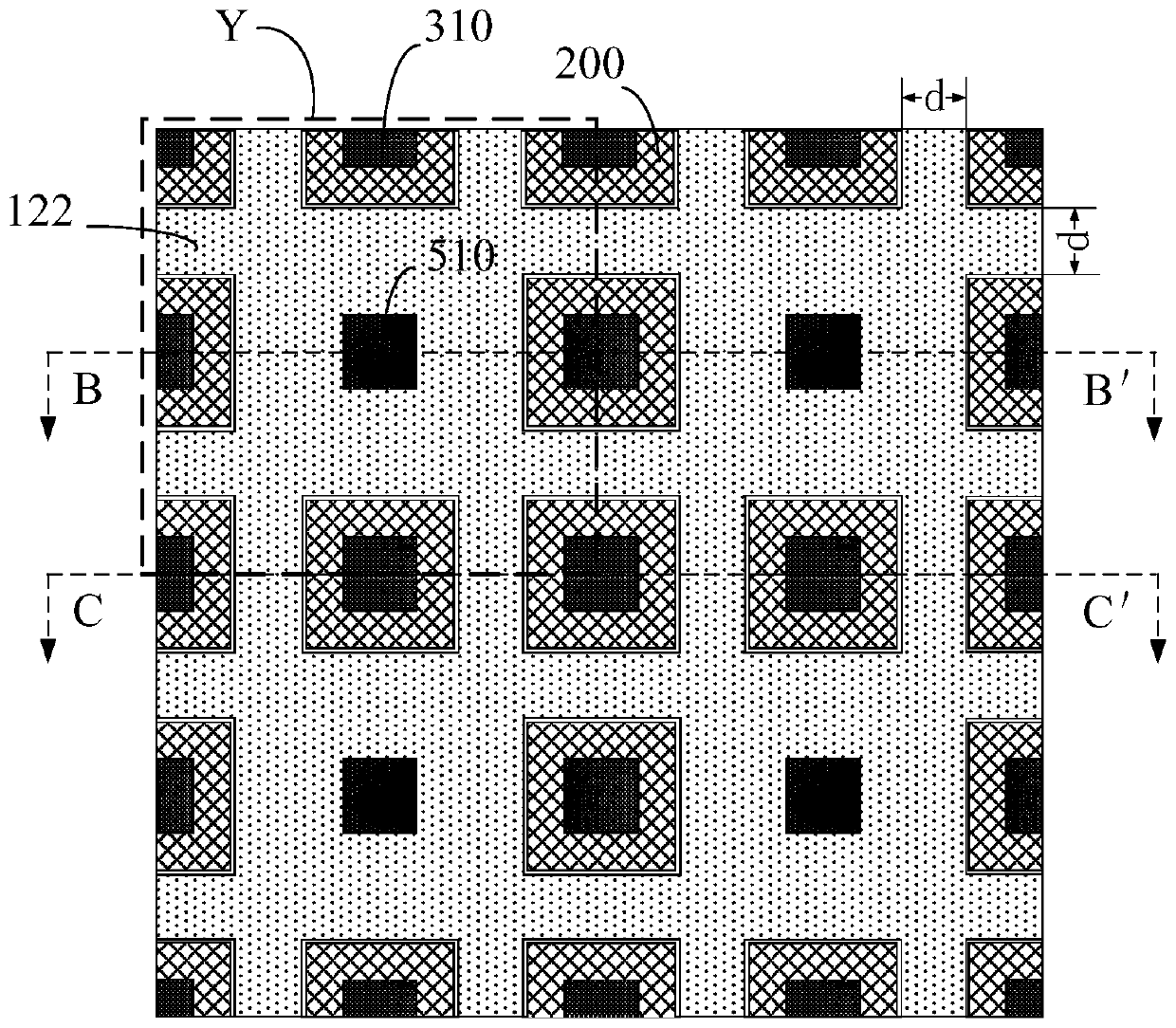

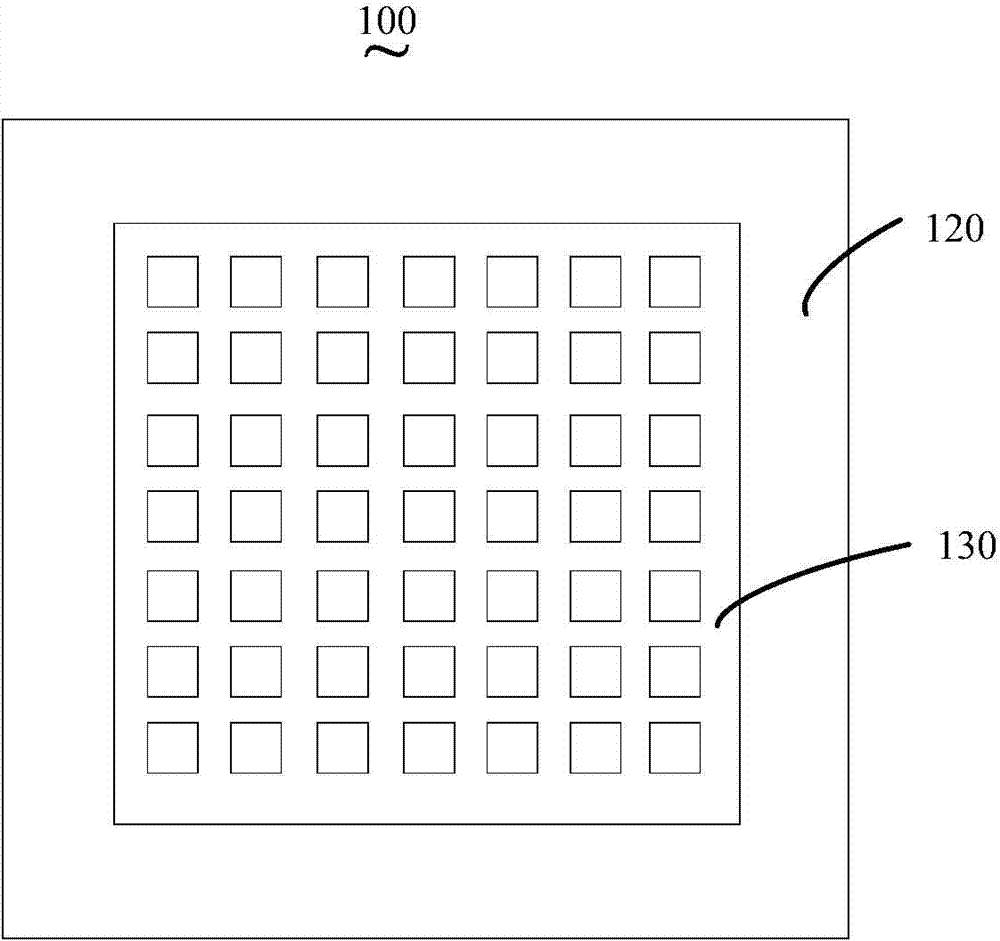

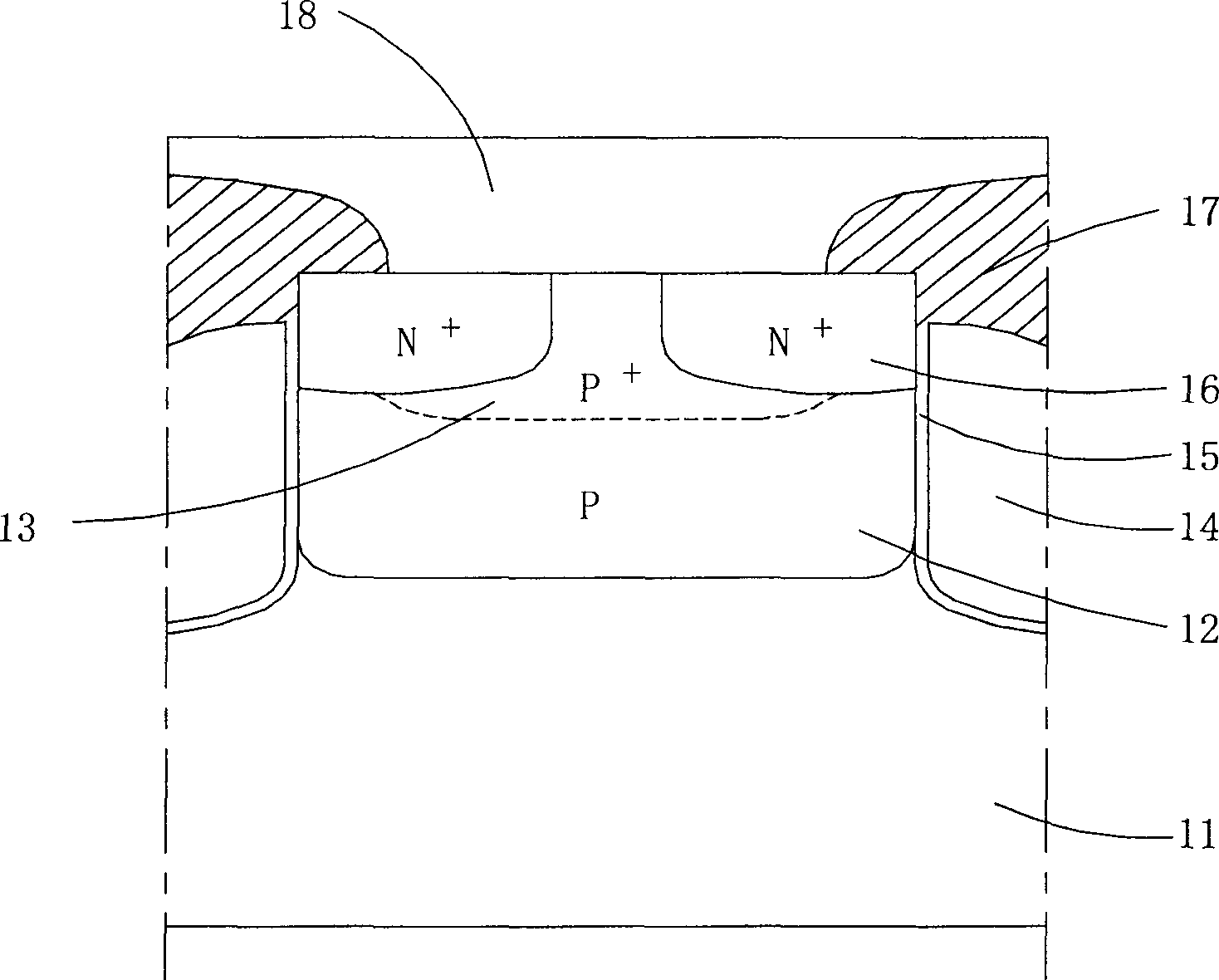

Power semiconductor device and method of manufacturing the same

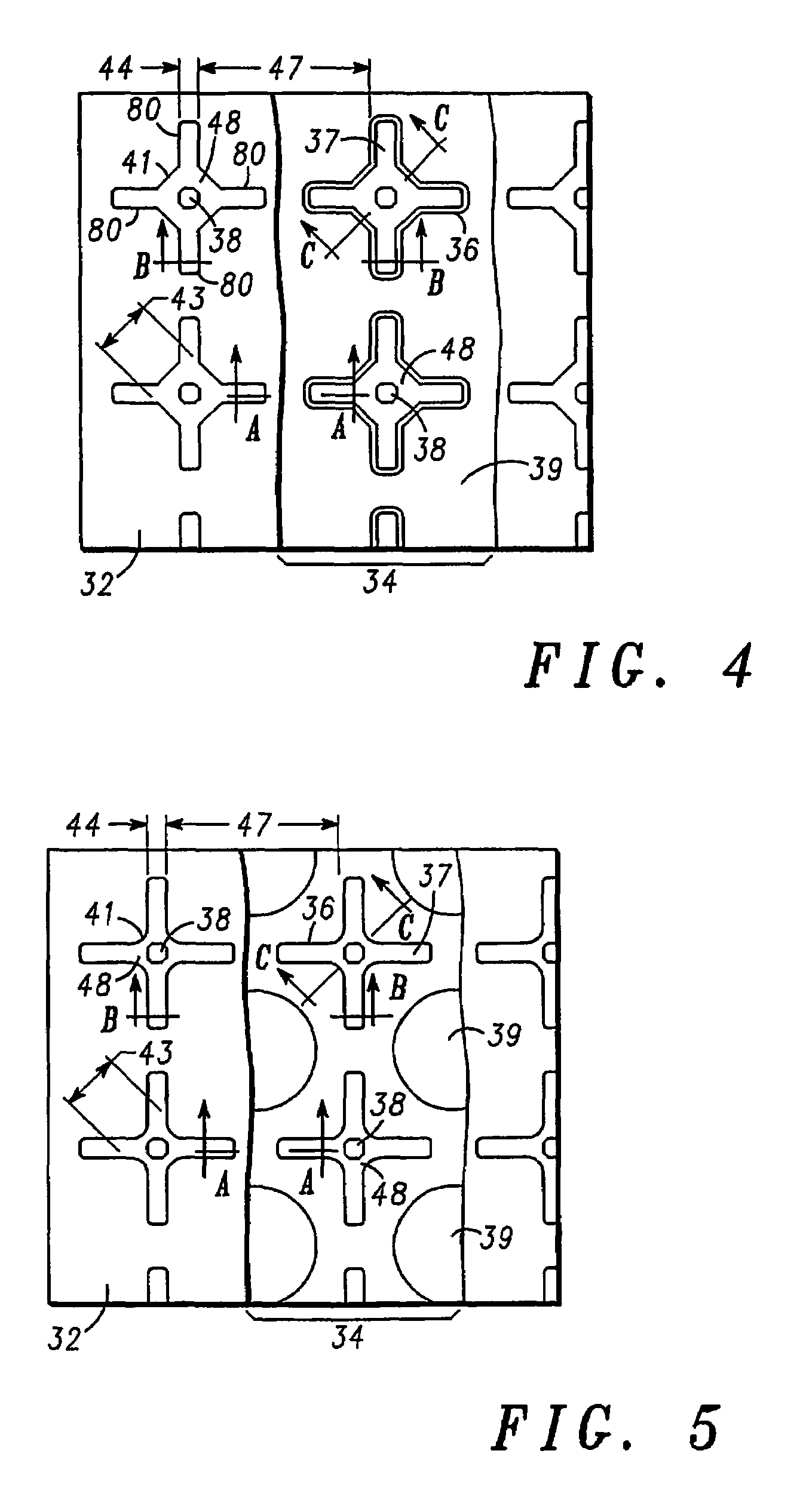

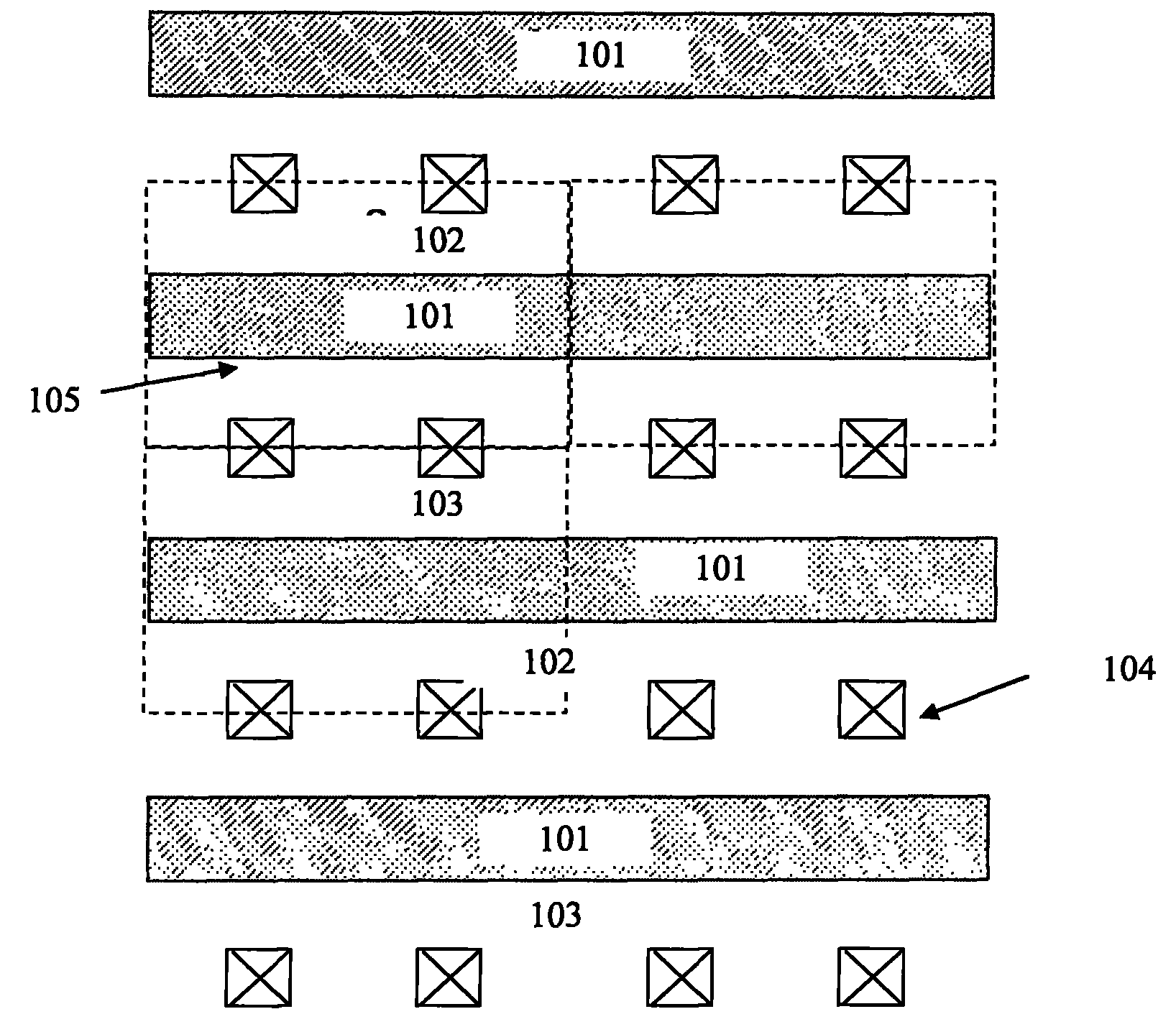

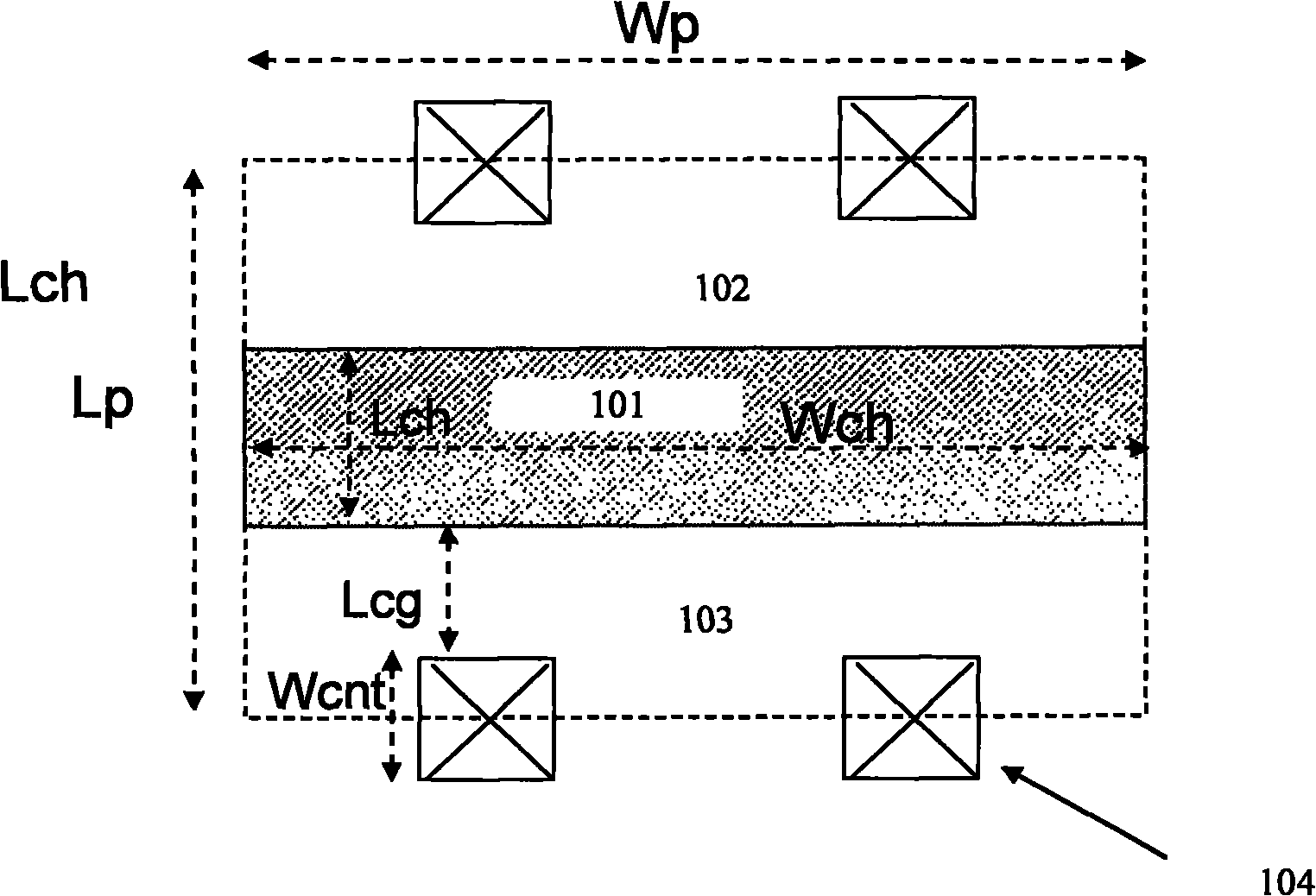

ActiveUS20060145252A1Improved channel density and on-state resistanceIncrease channel densitySemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceEngineering

A low on-state resistance power semiconductor device has a shape and an arrangement that increase the channel density and the breakdown voltage. The power semiconductor device comprises a plurality of individual cells formed on a semiconductor substrate (62). Each individual cell comprises a plurality of radially extending branches (80) having source regions (37) within base regions (36). The plurality of individual cells are arranged such that at least one branch of each cell extends towards at least one branch of an adjacent cell and wherein the base region (36) of the extending branches merge together to form a single and substantially uniformly doped base region (36) surrounding drain islands (39) at the surface of the semiconductor substrate (62).

Owner:NXP USA INC

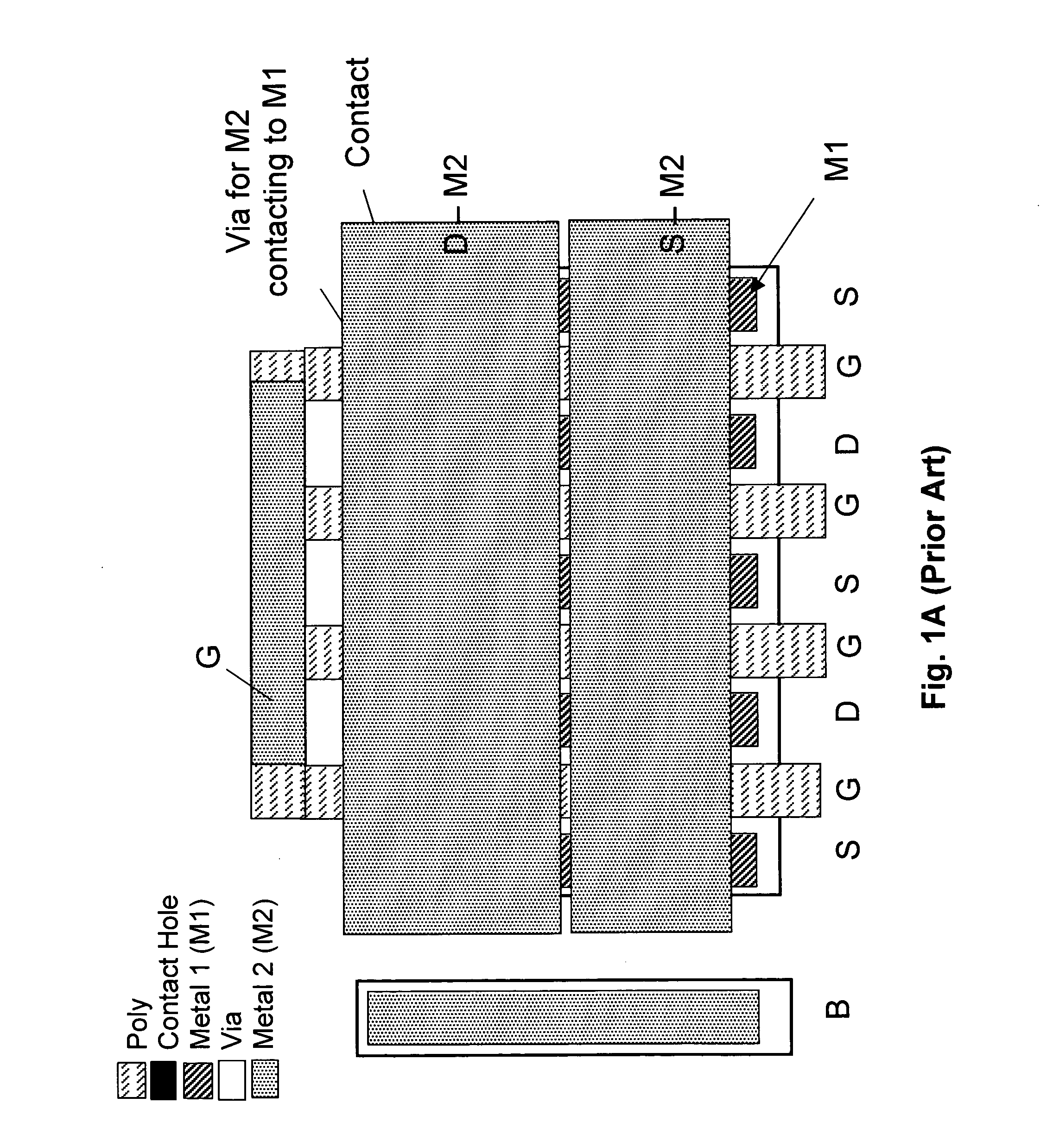

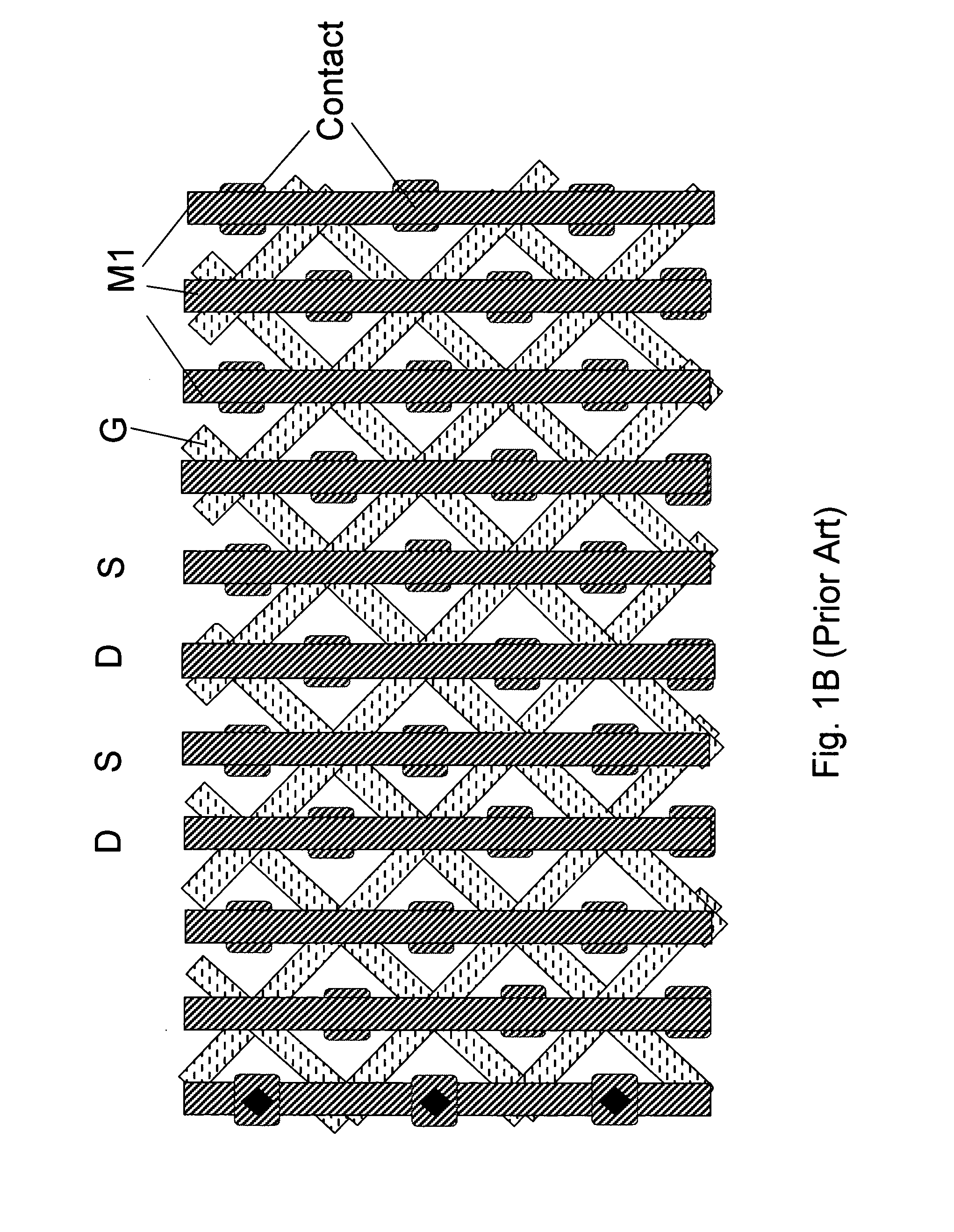

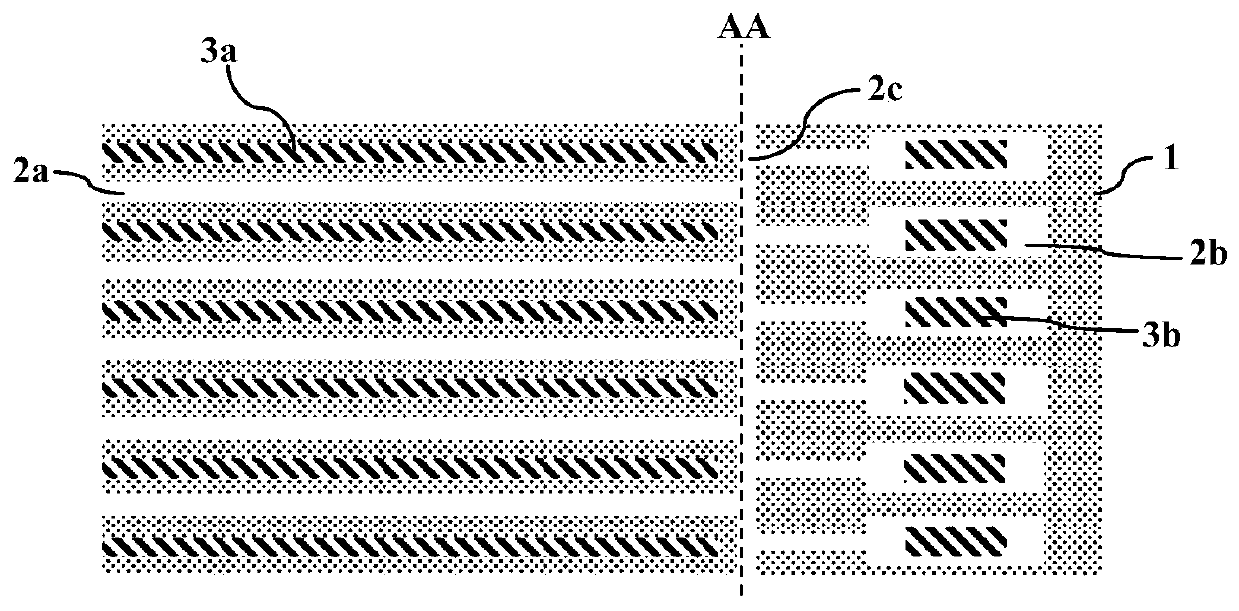

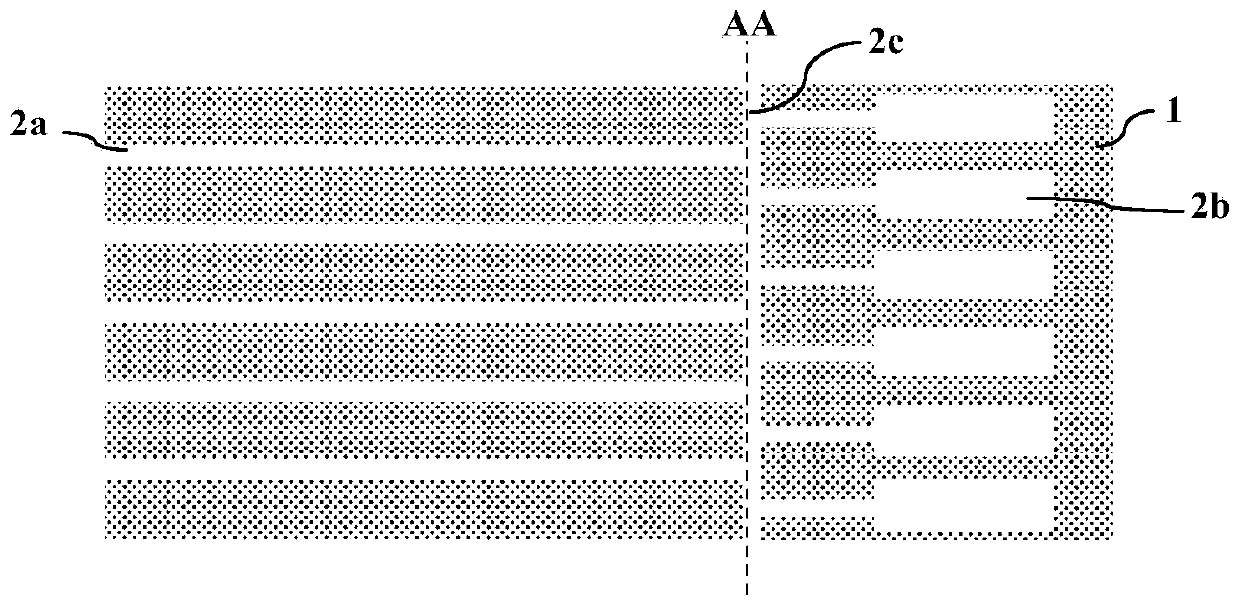

Closed cell configuration to increase channel density for sub-micron planar semiconductor power device

ActiveUS20070295996A1Increase channel width per unit areaIncrease the on-resistanceTransistorSemiconductor/solid-state device detailsChannel densityEngineering

A semiconductor power device supported on a semiconductor substrate that includes a plurality of transistor cells, each cell has a source and a drain region disposed on opposite sides of a gate region in the semiconductor substrate. A gate electrode is formed as an electrode layer on top of the gate region for controlling an electric current transmitted between the source and the drain regions. The gate electrode layer disposed on top of the semiconductor substrate is patterned into a wave-like shaped stripes for substantially increasing an electric current conduction area between the source and drain regions across the gate.

Owner:ALPHA & OMEGA SEMICON LTD

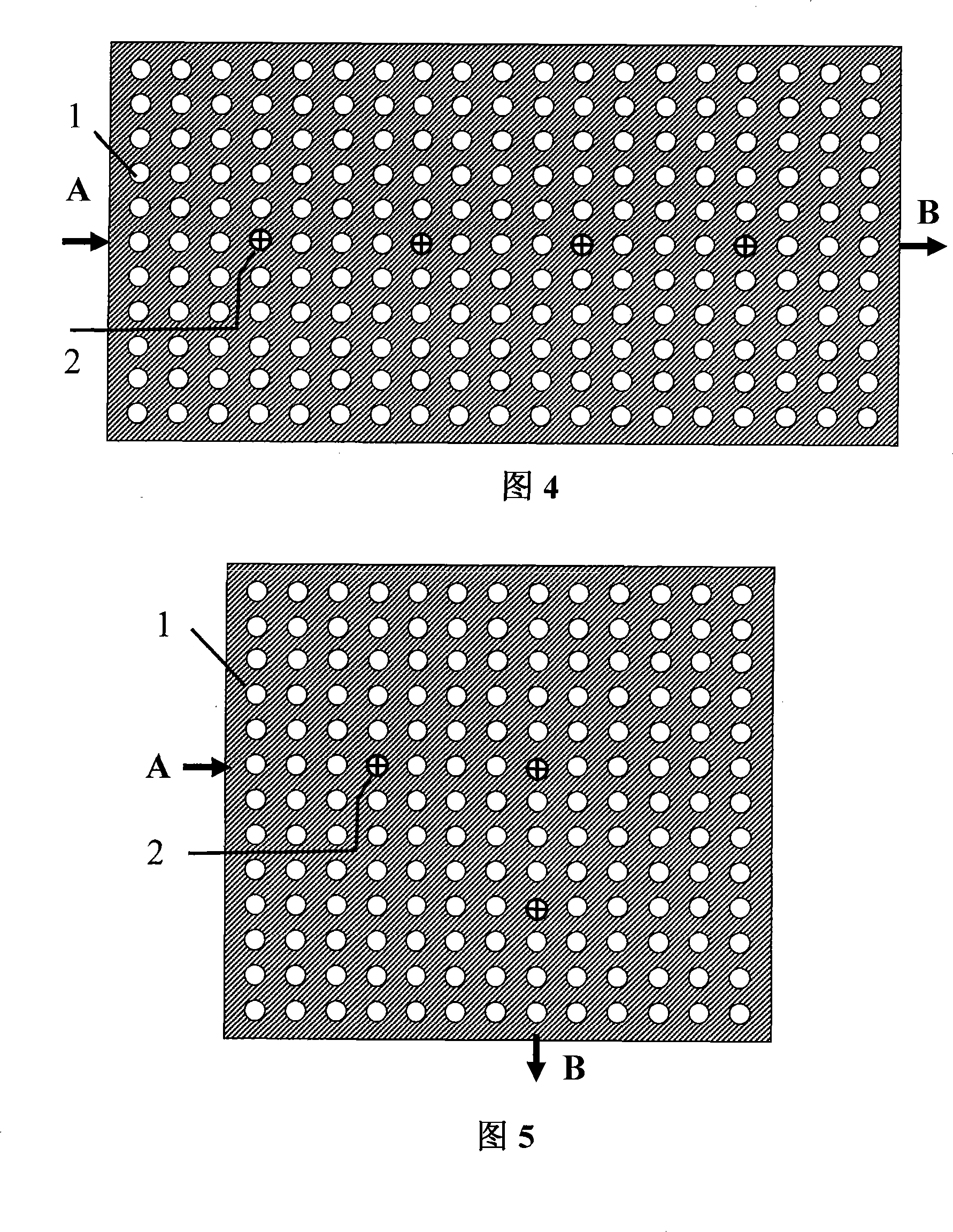

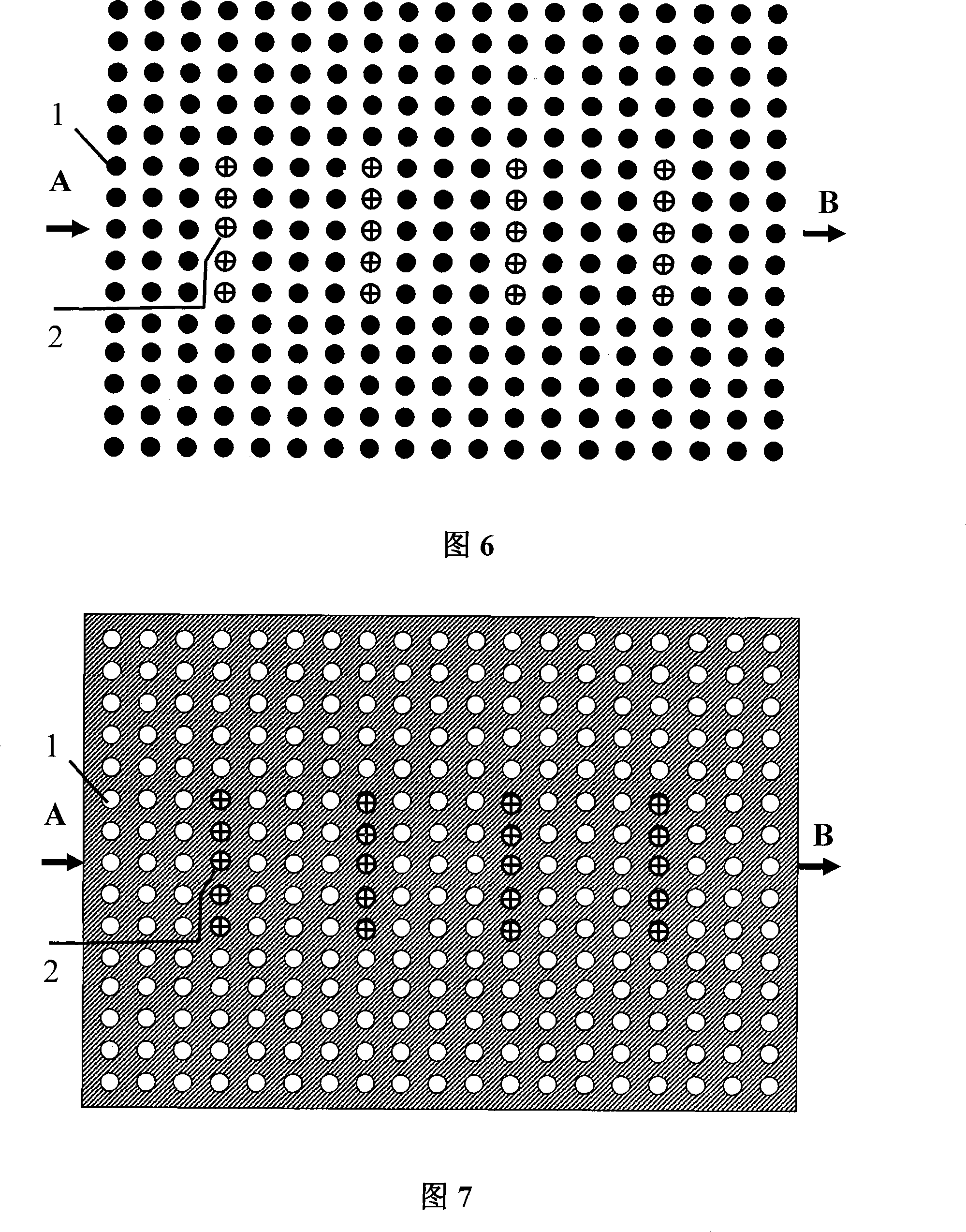

Multi-cavity cascade-connection photon crystal multicenter wave filter

InactiveCN101246237AIncrease channel densityReduce the number of cyclesOptical light guidesNon symmetricPhotonic crystal

The invention provides a multi-photons crystal imperfect cavity cascaded multi-channel filter, which has the structure as follows. A defect is equipped in the middle of the central symmetrical or non-symmetric periodical photos crystal, that is the photon crystal single defect cavity, many imperfect cavities cascade and form the multi-channel filter. The number of channel is equal to the number of cavity; the intensity of channel is proportional to the number of cavity. The position of channel is mainly determined by the thickness of imperfect layer, the channel range is determined by the periodicity of photon crystal.

Owner:SHENZHEN UNIV +1

Power semiconductor device with a base region and method of manufacturing same

ActiveUS7432145B2Increase channel densitySemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceChannel density

A low on-state resistance power semiconductor device has a shape and an arrangement that increase the channel density and the breakdown voltage The power semiconductor device comprises a plurality of individual cells formed on a semiconductor substrate (62). Each individual cell comprises a plurality of radially extending branches (80) having source regions (37) within base regions (36). The plurality of individual cells are arranged such that at least one branch of each cell extends towards at least one branch of an adjacent cell and wherein the base region (36) of the extending branches merge together to form a single and substantially uniformly doped base region (36) surrounding drain islands (39) at the surface of the semiconductor substrate (62).

Owner:NXP USA INC

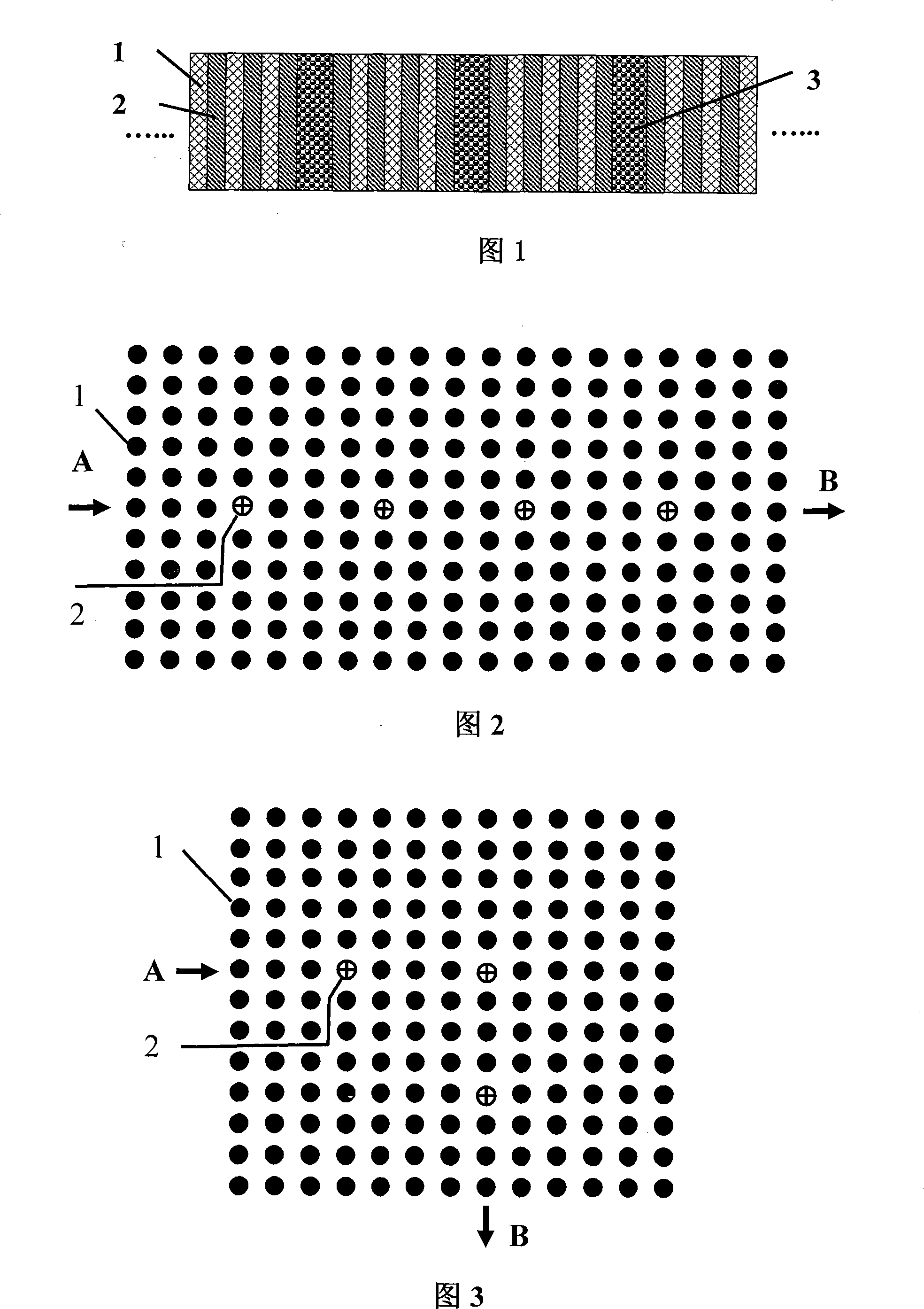

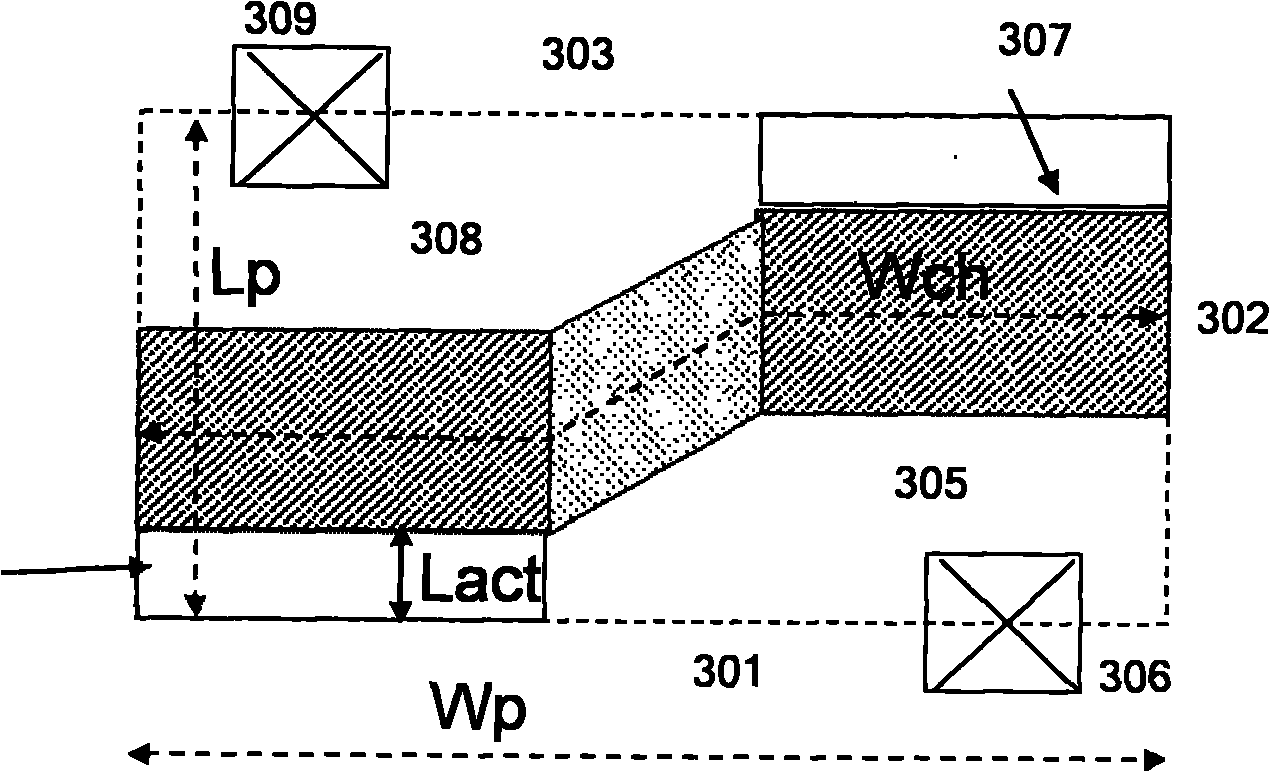

Power field effect transistor and layout method thereof

InactiveCN102110691AIncrease channel densityLower on-resistanceSolid-state devicesSemiconductor/solid-state device manufacturingChannel widthField-effect transistor

The invention relates to a power field effect transistor which is integrated on a single silicon slice and a layout method thereof. The power field effect transistor consists of a plurality of unit lattices which are arranged in parallel, wherein each unit lattice comprises a gate region, a source region and a drain region; and the drain region and the source region are distributed on the two sides of the gate region respectively. The power field effect transistor is characterized in that: the gate region is bent and bends towards the drain region at a first end to form a first concave region, a first bent region and a first contact region on the drain region; the gate region bends towards the source region at a second end to form a second concave region, a second bent region and a second contact region on the source region; by the bent gate region, an effective channel width is increased, so that on resistance RDSON is reduced; the corresponding drain region and source region are not rectangular any longer but have different shapes on different regions, so that the height of each unit lattice is reduced to further reduce the on resistance RDSON; and the channel density of the field effect transistor can also be increased, so that the on resistance RDSON is reduced. A method for implementing the field effect transistor is more favorable and practical.

Owner:SILERGY SEMICON TECH (HANGZHOU) CO LTD

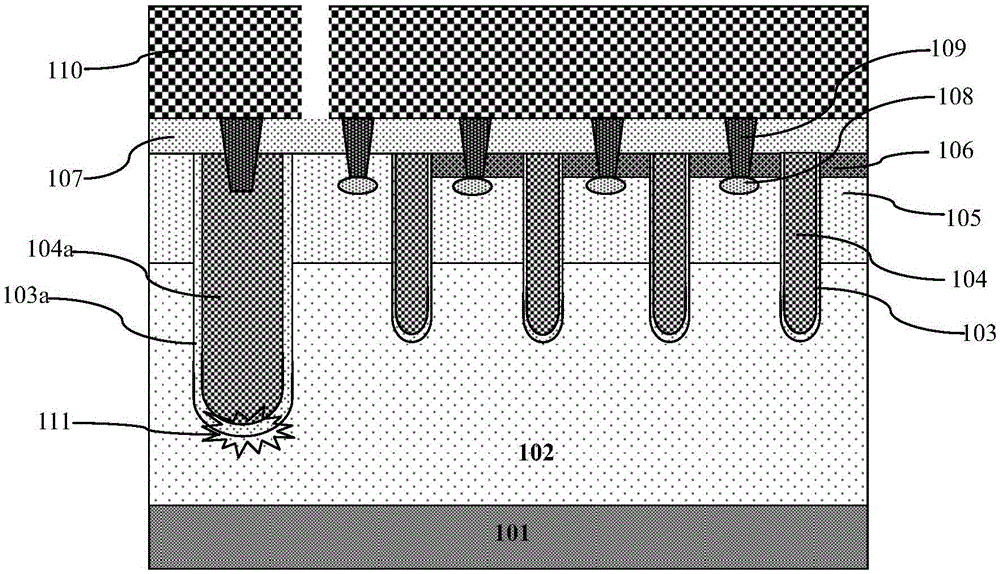

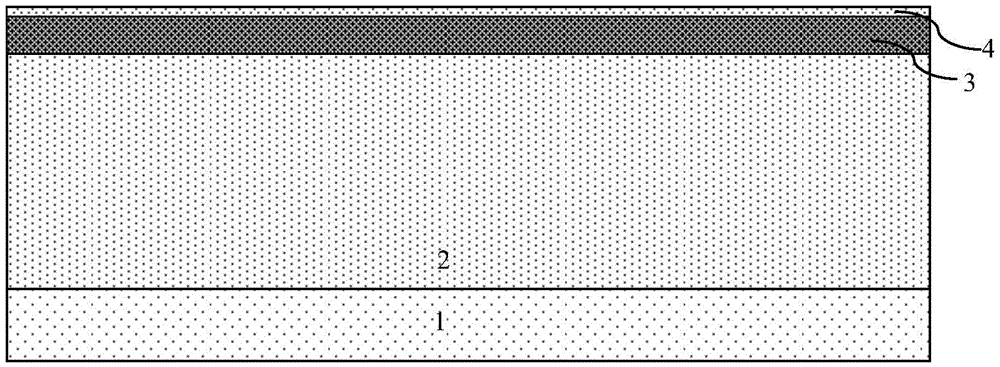

Trench gate power MOSFET (Metal Oxide Semiconductor Field Effect Transistor) and manufacturing method thereof

ActiveCN105551965AReduce spacingLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricEngineering

The invention discloses a trench gate power MOSFET (Metal Oxide Semiconductor Field Effect Transistor), which comprises a semiconductor epitaxial layer, wherein a hard mask layer is formed on the surface of the semiconductor epitaxial layer; a gate trench pattern and a source area contact hole pattern which are simultaneously defined by a first trench mask plate are formed in the hard mask layer; the sizes of gate trenches are defined by the gate trench pattern; bottom areas of source area contact holes are completely defined by the source area contact hole pattern of the hard mask layer; a gate dielectric layer and a polysilicon gate are formed in each gate trench; an interlayer film is formed on the surface of the hard mask layer and the surface of the polysilicon gate; top areas of the source area contact holes penetrate through the interlayer film and are defined by a contact hole mask plate; the source area contact holes are formed by self-aligned superposition of the top areas and the bottom areas; and structures without registration deviation are formed between the top areas of the source area contact holes and the gate trenches. The invention also discloses a manufacturing method of the trench gate power MOSFET. According to the trench gate power MOSFET and the manufacturing method thereof, a distance between the gate trenches can be reduced and the channel density is increased.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Reverse conducting IGBT

InactiveUS8564097B2High densityFacilitate conductionTransistorSolid-state devicesSemiconductorPhysics

An insulated gate bipolar transistor (IGBT) is provided comprising a semiconductor substrate having the following regions in sequence: (i) a first region of a first conductive type having opposing surfaces, a column region of a second conductive type within the first region extending from a first of said opposing surfaces; (ii) a drift region of the second conductive type; (iii) a second region of the first conductive type, and (iv) a third region of the second conductive type. There is provided a gate electrode disposed to form a channel between the third region and the drift region, a first electrode operatively connected to the second region and the third region, a second electrode operatively connected to the first region and the column region. The arrangement of the IGBT is such that the column region is spaced from a second surface of the opposing surfaces of the first region, whereby a forward conduction path extends sequentially through the third region, the second region, the drift region, and the first region, and whereby a reverse conduction path extends sequentially through the second region, the drift region, the first region and the column region. Reverse conduction of the IGBT occurs through a thyristor structure which is embedded in the IGBT. Such an IGBT structure is advantageous over a reverse conducting IGBT structure in which an anti-parallel diode is integrated or embedded because it provides improved reverse conduction and snapback performance.

Owner:SINOPOWER SEMICON

Trench gate MOSFET device with electric field shielding structure

ActiveCN113345965AReduce electric field strengthImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETElectrical field strength

The invention provides a trench gate MOSFET device with an electric field shielding structure, which comprises a substrate, a source electrode, a drain electrode, a gate trench, the electric field shielding structure, source electrode regions, a semiconductor region with a first conduction type, and one or more electric field shielding structures with a second conduction type positioned below the surface of the semiconductor region, the electric field shielding structures intersect with the side wall of the gate trench at an angle, and the source electrode regions are positioned on two sides or the periphery of the gate trench, and are divided into a plurality of source sub-regions by an electric field shielding structure. By arranging one or more electric field shielding structures intersecting with the side wall of the gate trench and reasonably arranging the arrangement mode of the electric field shielding structures, the cell size of the device can be effectively reduced, the channel density and the device conduction current density can be improved, the specific on-resistance of the device can be reduced, and the device conduction performance can be improved; meanwhile, the electric field shielding effect is enhanced, the electric field intensity in the gate oxide layer is reduced, and the long-term working stability and reliability of the device are improved.

Owner:ZHEJIANG UNIV HANGZHOU GLOBAL SCI & TECH INNOVATION CENT

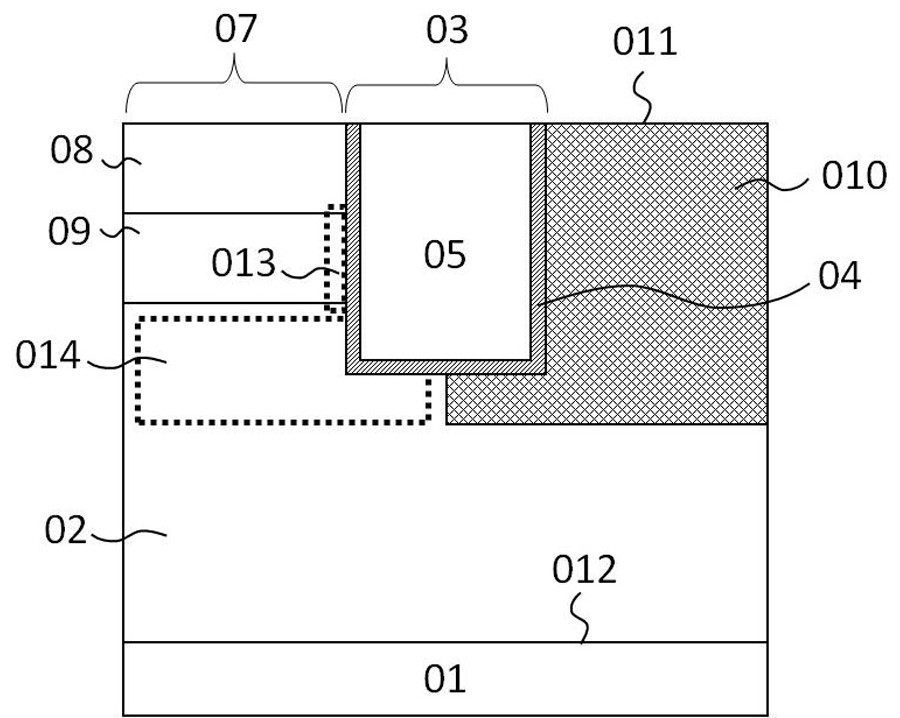

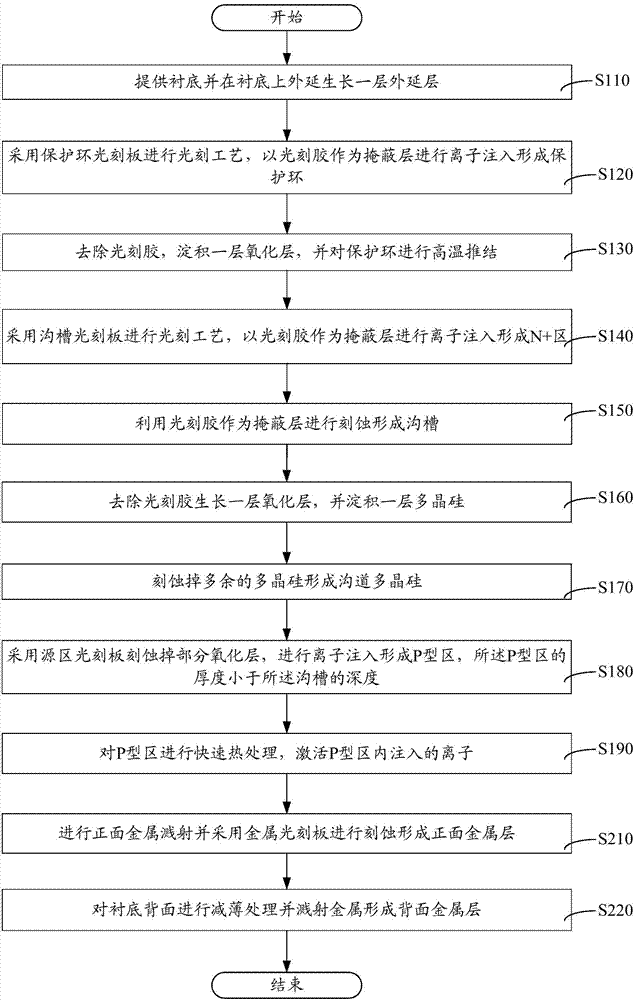

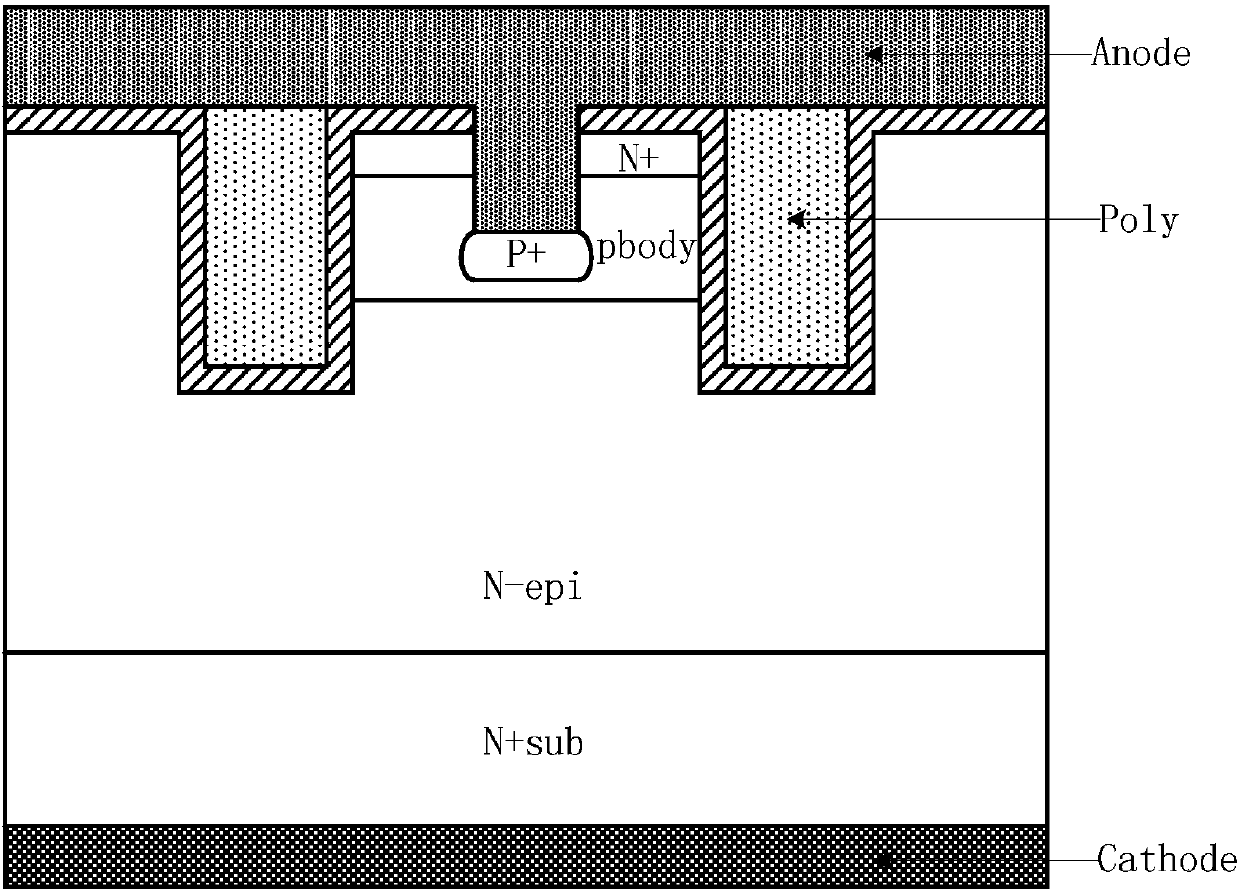

Rectifying device and preparation method thereof

InactiveCN106409827ASimple stepsReduce manufacturing costSolid-state devicesSemiconductor/solid-state device manufacturingChannel densityBody area

The present invention discloses a rectifying device and a preparation method thereof. The device comprises a substrate of a first conductive type, a cell area and a terminal area, wherein a groove type area is arranged on the right side of the substrate of the cell area, the bottom of the groove type area is equipped with a buried layer area of a second conductive type, and the rest areas of the right side of the substrate of the cell area except the groove type area are equipped with the body areas of the second conductive types. The rectifying device contains an MOS structure and a PN junction simultaneously, the advantages of the MOS device and a PN diode can be combined together, and by a groove type structure, the junction type field effect transistor parasitic resistance is not generated, the reduction of the positive conduction voltage drop is not limited, at the same time, the channel density of the device in the unit area also can be increased, and the device cost is reduced. The buried layer area of the second conductive type at the bottom of the groove type area enables a blocking voltage to be improved effectively. Therefore, the rectifying device is simple in structure and excellent in performance, and also has the low positive conduction voltage drop and the high blocking voltage.

Owner:WUXI CHINA RESOURCES HUAJING MICROELECTRONICS

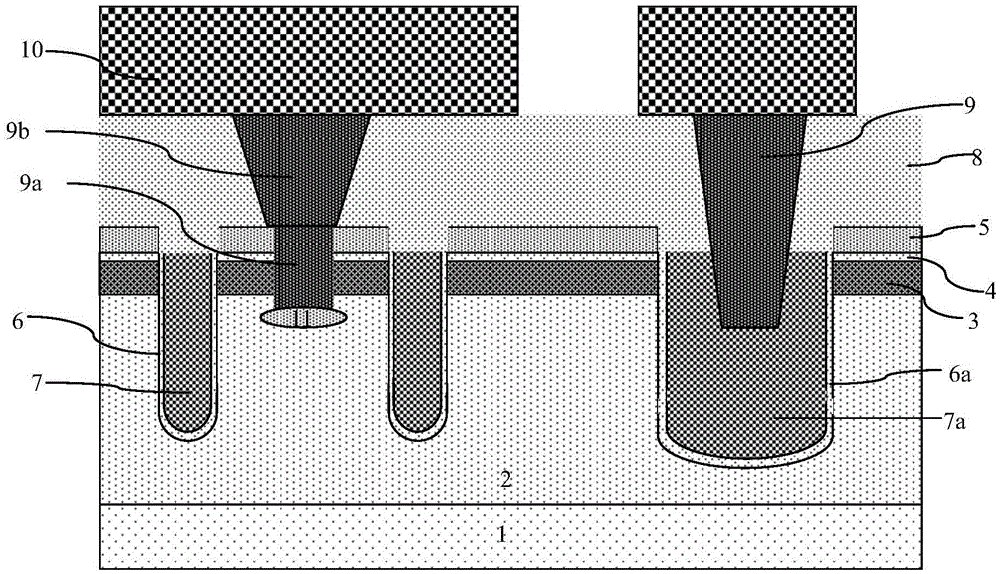

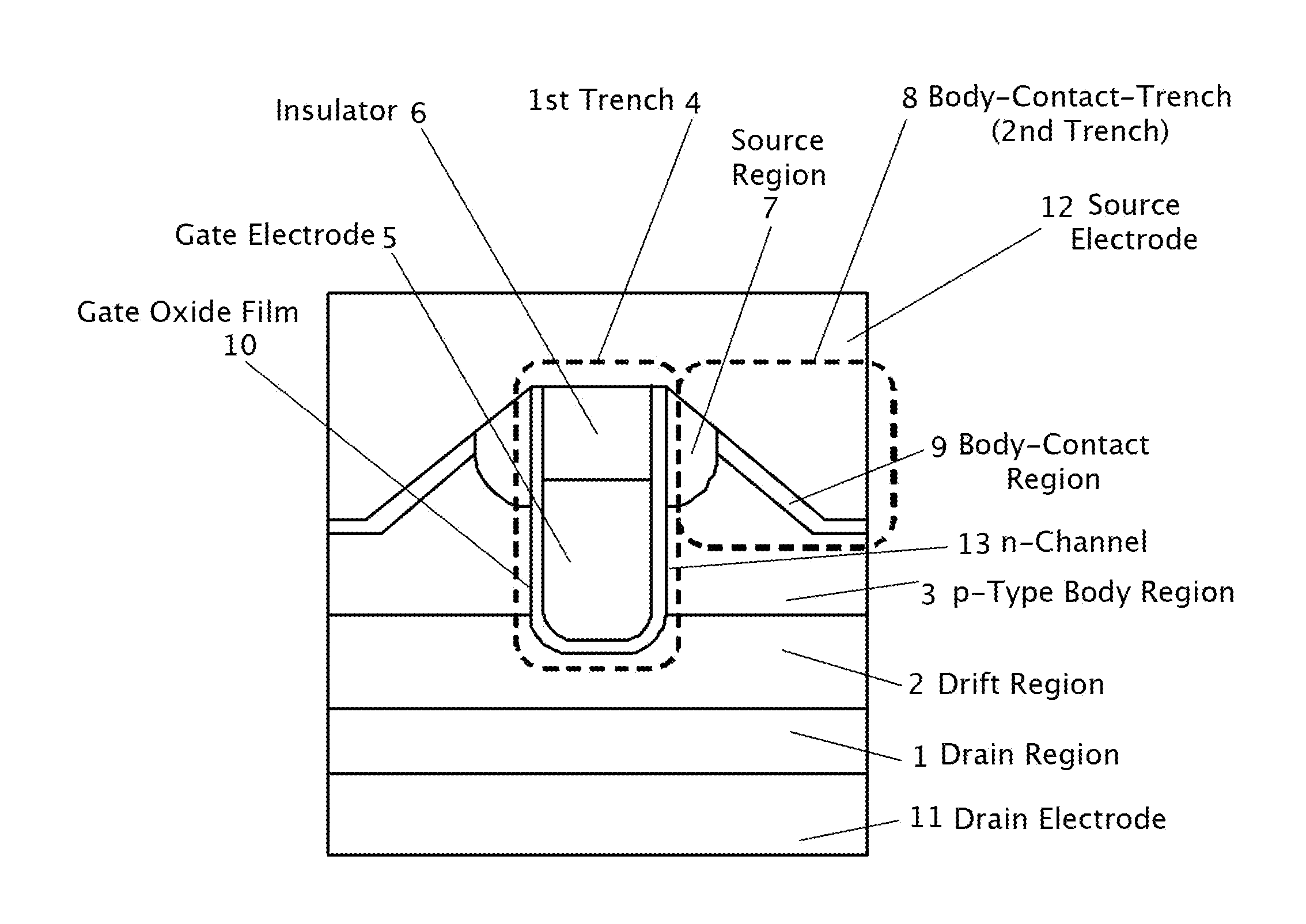

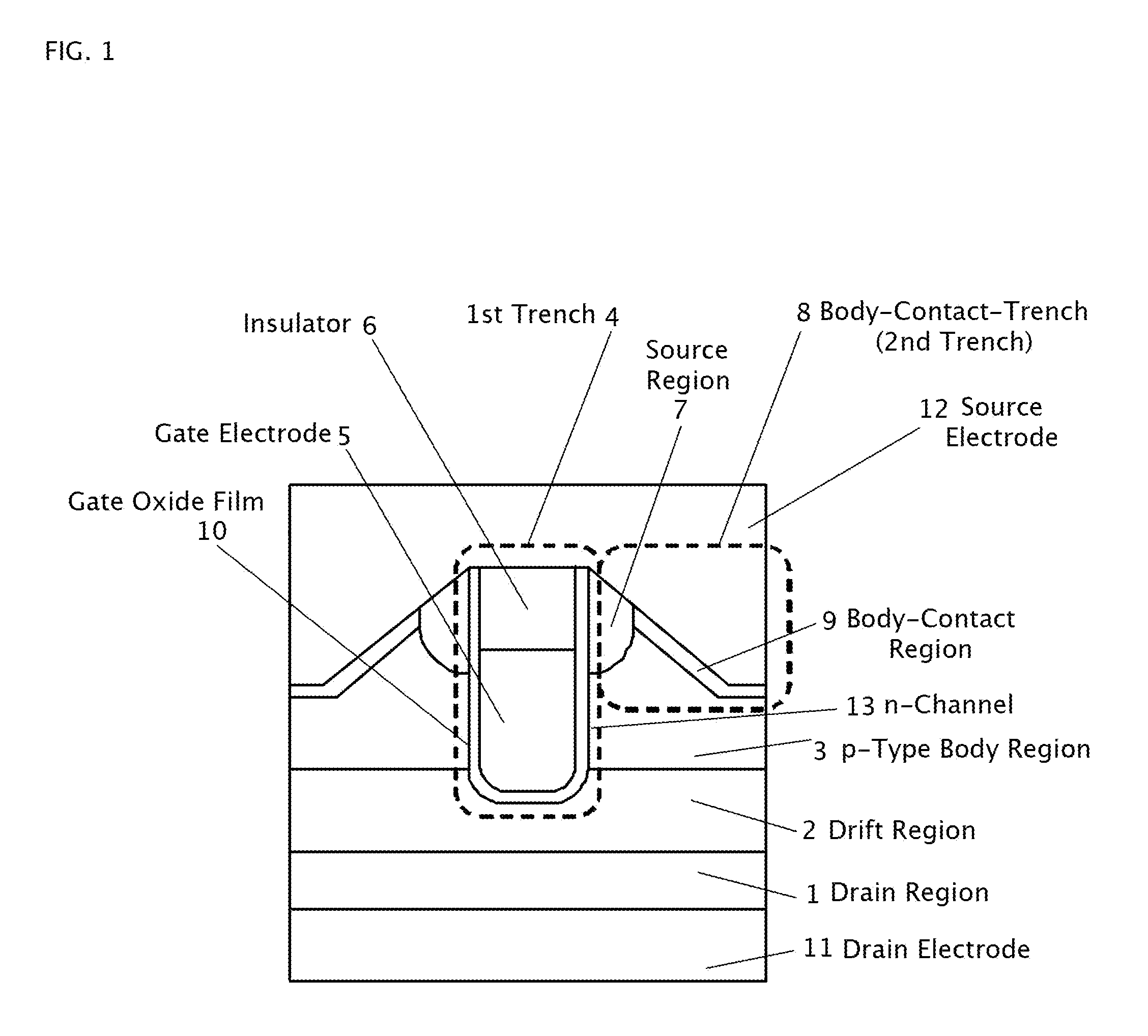

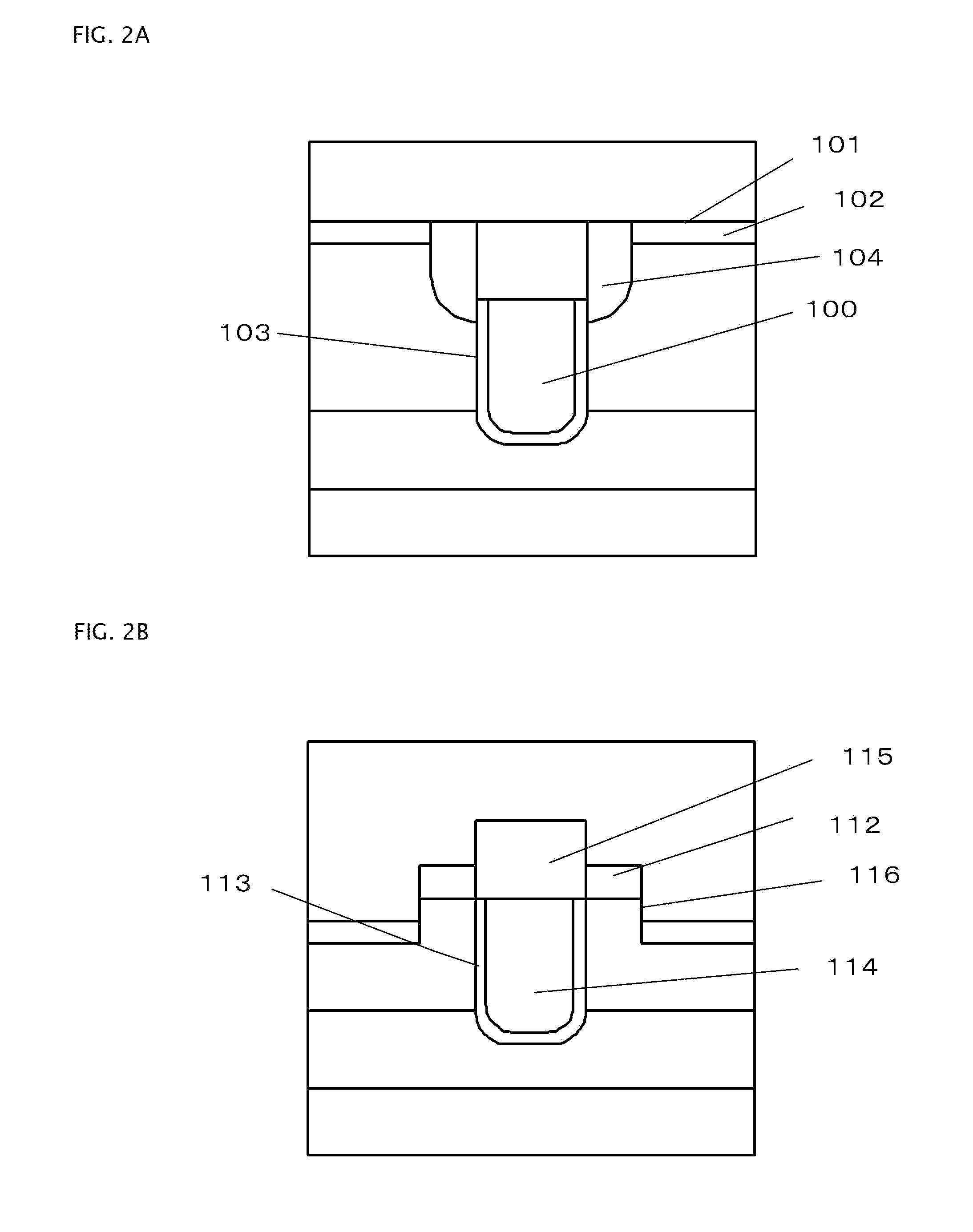

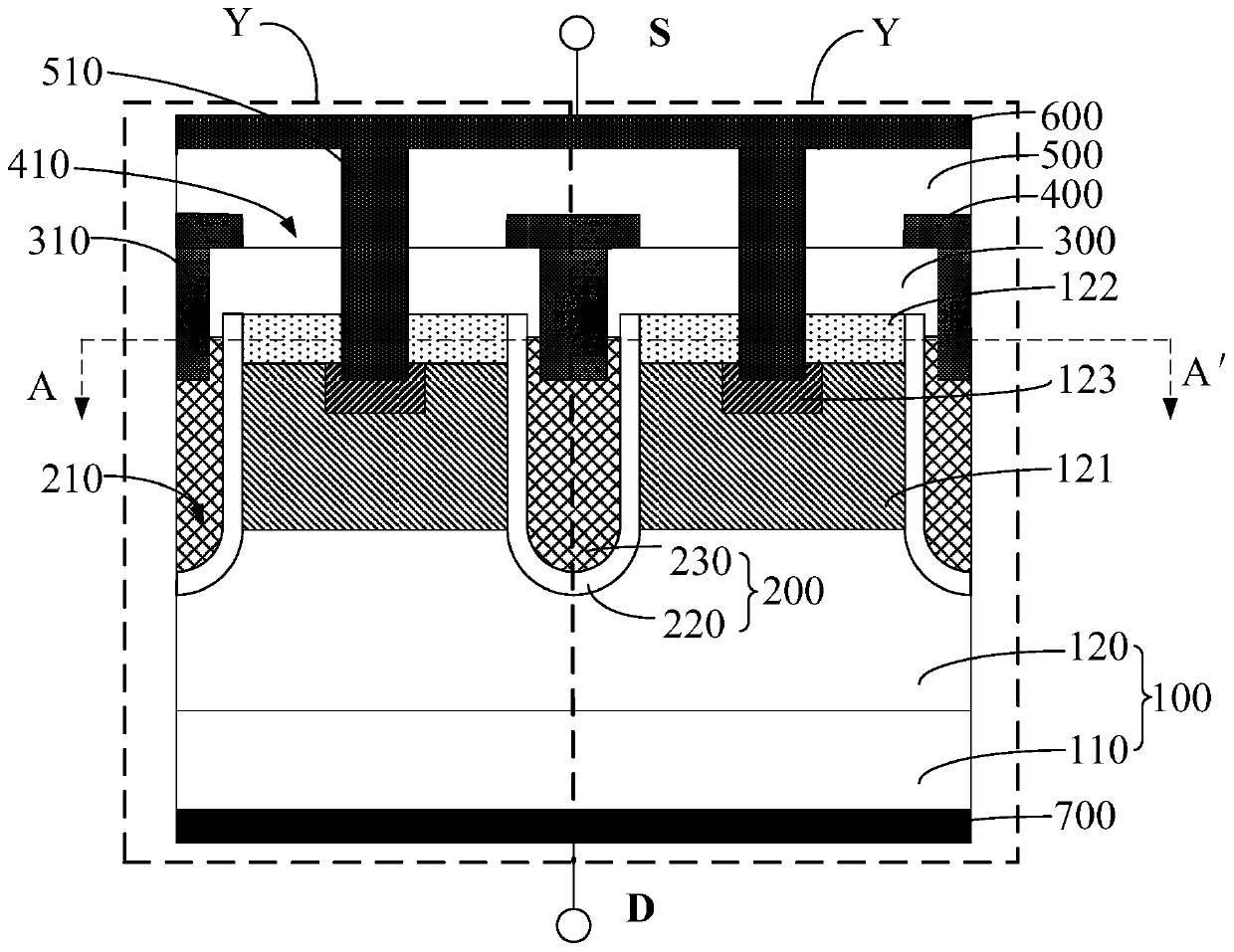

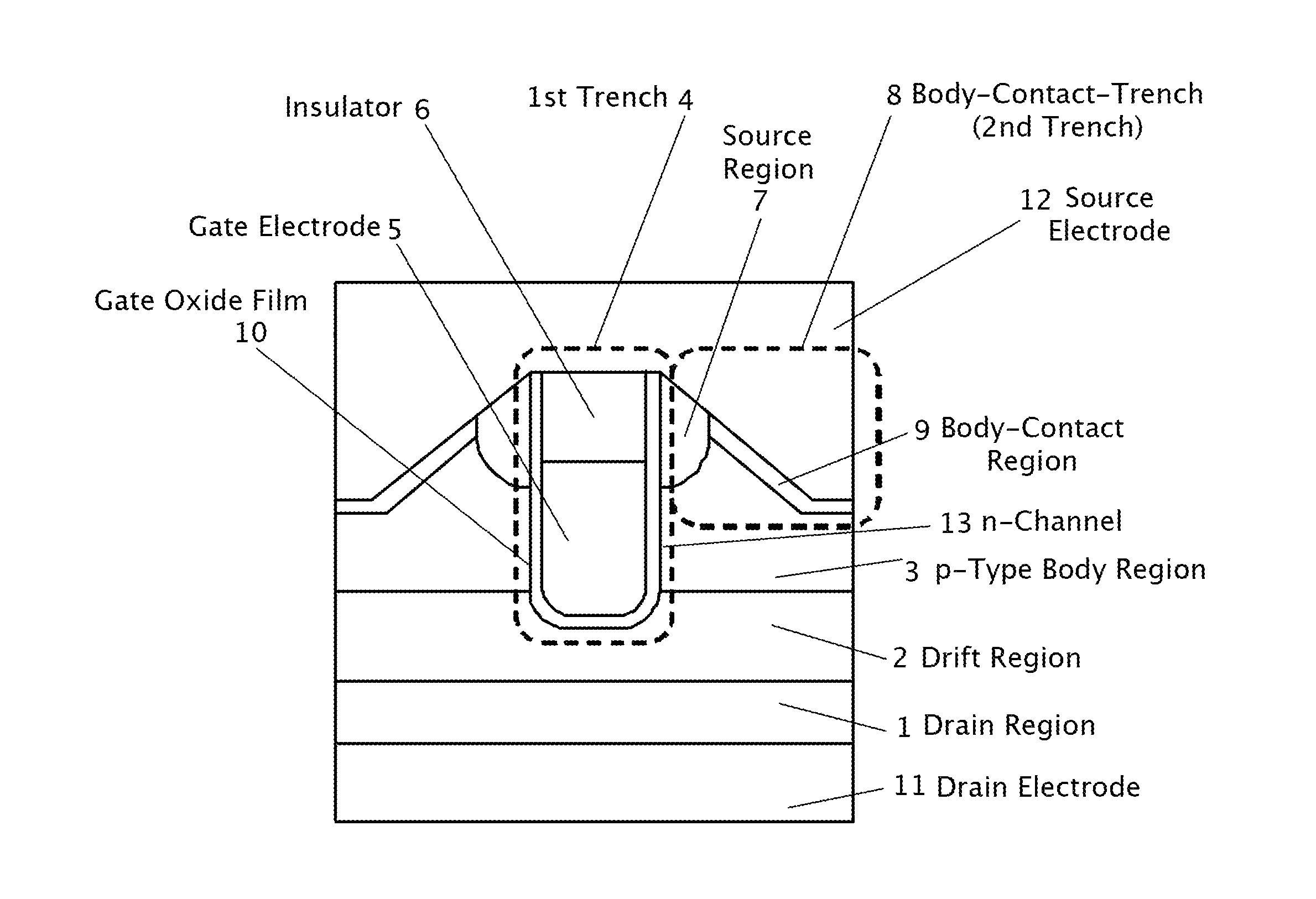

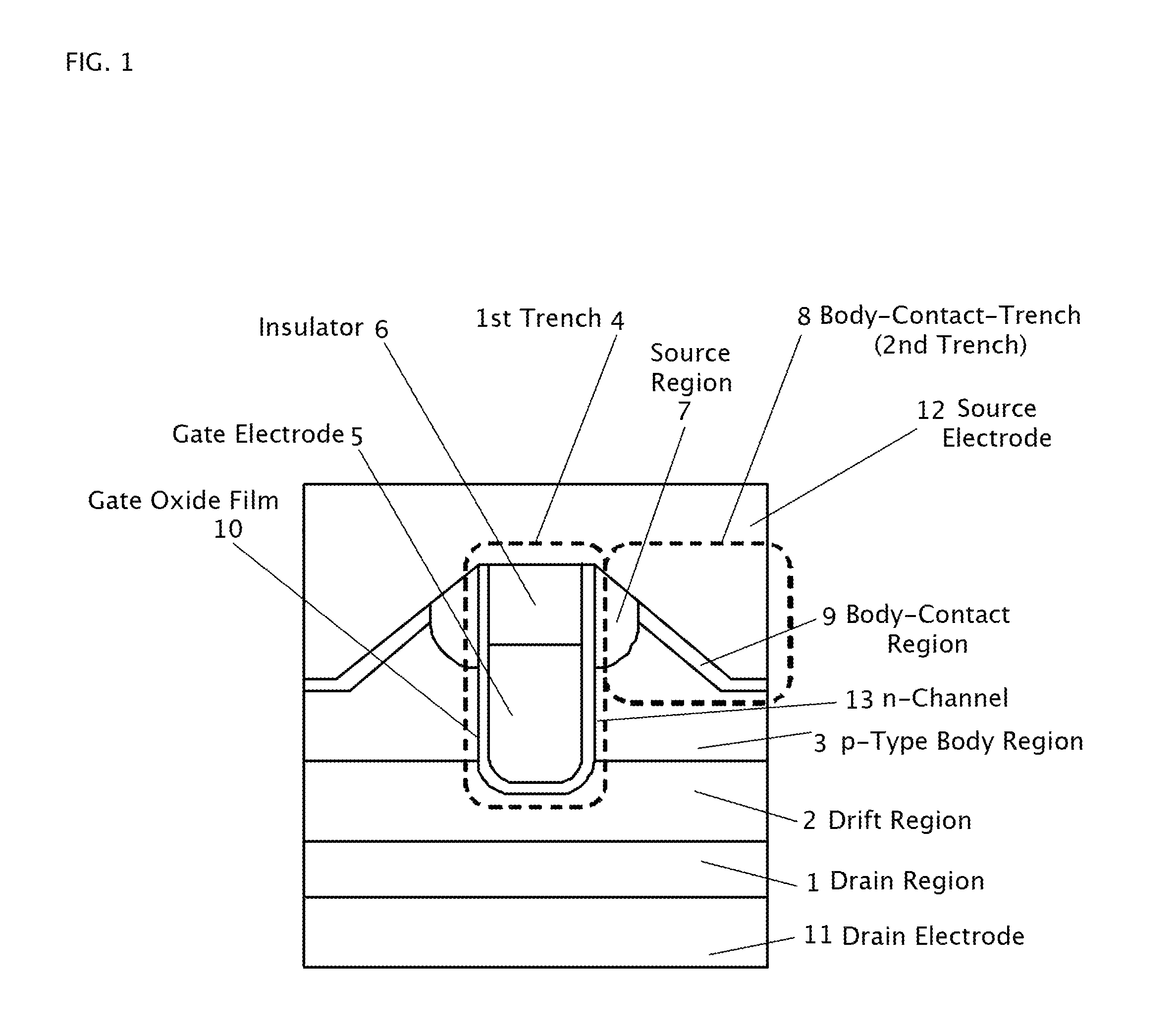

Trench gate semiconductor device and the method of manufacturing the same

InactiveUS20130115747A1Increase channel densityReduce parasitic resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialTrench gate

A trench gate semiconductor device is disclosed which has a trench gate structure including an insulator in the upper portion of a first trench, the insulator being on a gate electrode; a source region having a lower end surface positioned lower than the upper surface of the gate electrode; a second trench in the surface portion of a semiconductor substrate between the first trenches, the second trench having a slanted inner surface providing the second trench with the widest trench width at its opening and a bottom plane positioned lower than the lower end surface of the source region, the slanted inner surface being in contact with the source region; and a p-type body-contact region in contact with the slanted inner surface of the second trench. The trench gate semiconductor device and its manufacturing method facilitate increasing the channel density and lowering the body resistance of the parasitic BJT.

Owner:FUJI ELECTRIC CO LTD

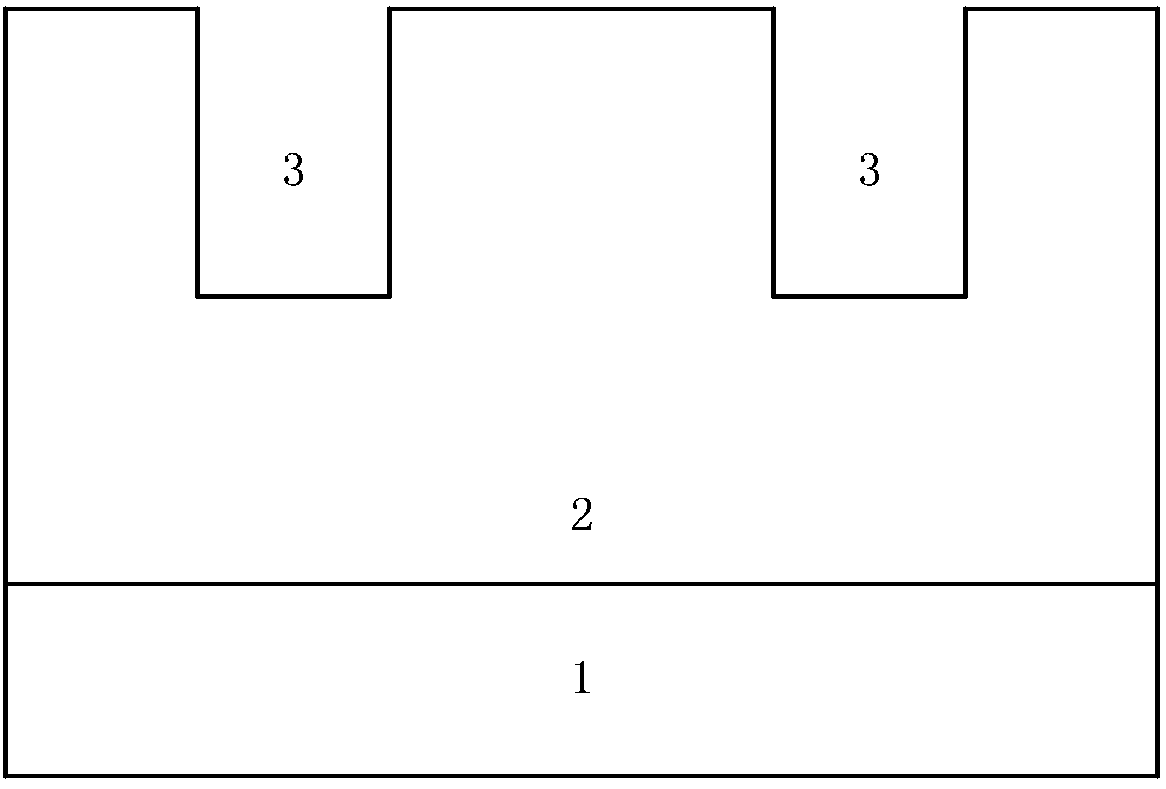

Integrated structure of trenches and manufacturing method thereof

ActiveCN111128853AImprove breakdown voltageAdd depthSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering physics

The invention discloses an integrated structure of trenches. A first trench and a second trench with large width difference are integrated on a semiconductor substrate at the same time; on the layoutstructure, the second trench is divided into a first sub-trench, a second sub-trench and a spacer region; the width difference between the first sub-trench and the first trench and the width difference between the second sub-trench and the first trench are small, and the depth difference among the first trench, the first sub-trench and the second sub-trench meets the required value after the anisotropic trench etching process; and the spacer region is removed by an isotropic anisotropic trench etching process to break through the first and second sub-trenches in the width direction and form asecond trench. The invention further discloses a manufacturing method of the integrated structure of the trenches. According to the invention, the defect that the trenches with large width differencehave large depth difference after the anisotropic etching process can be eliminated, the depth difference of the trenches with different widths is reduced or is not different, and when the integratedstructure of the trenches is applied to a trench gate semiconductor device, the breakdown voltage of the device can be improved or the specific on-resistance of the device can be reduced.

Owner:HUA HONG SEMICON WUXI LTD

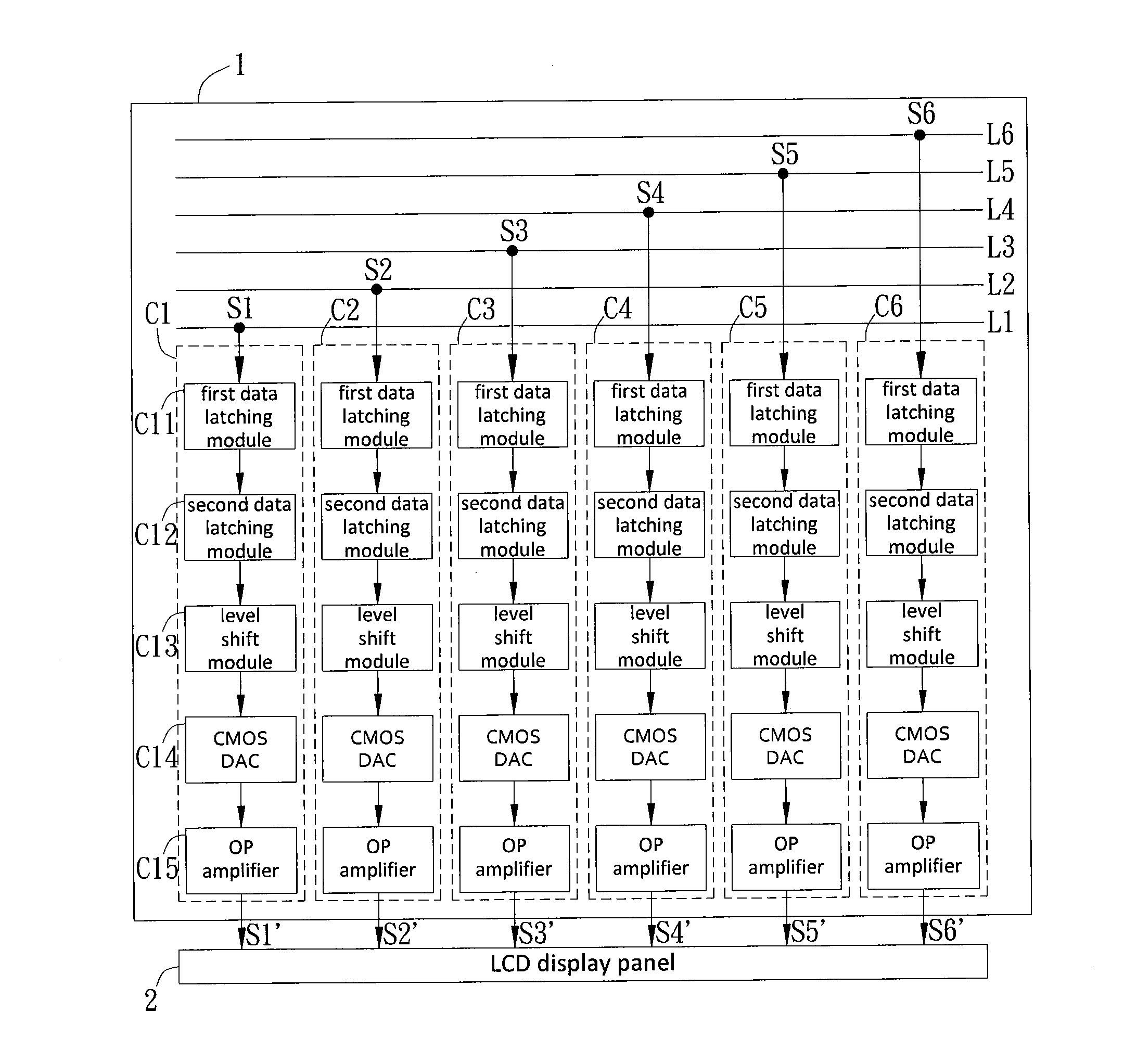

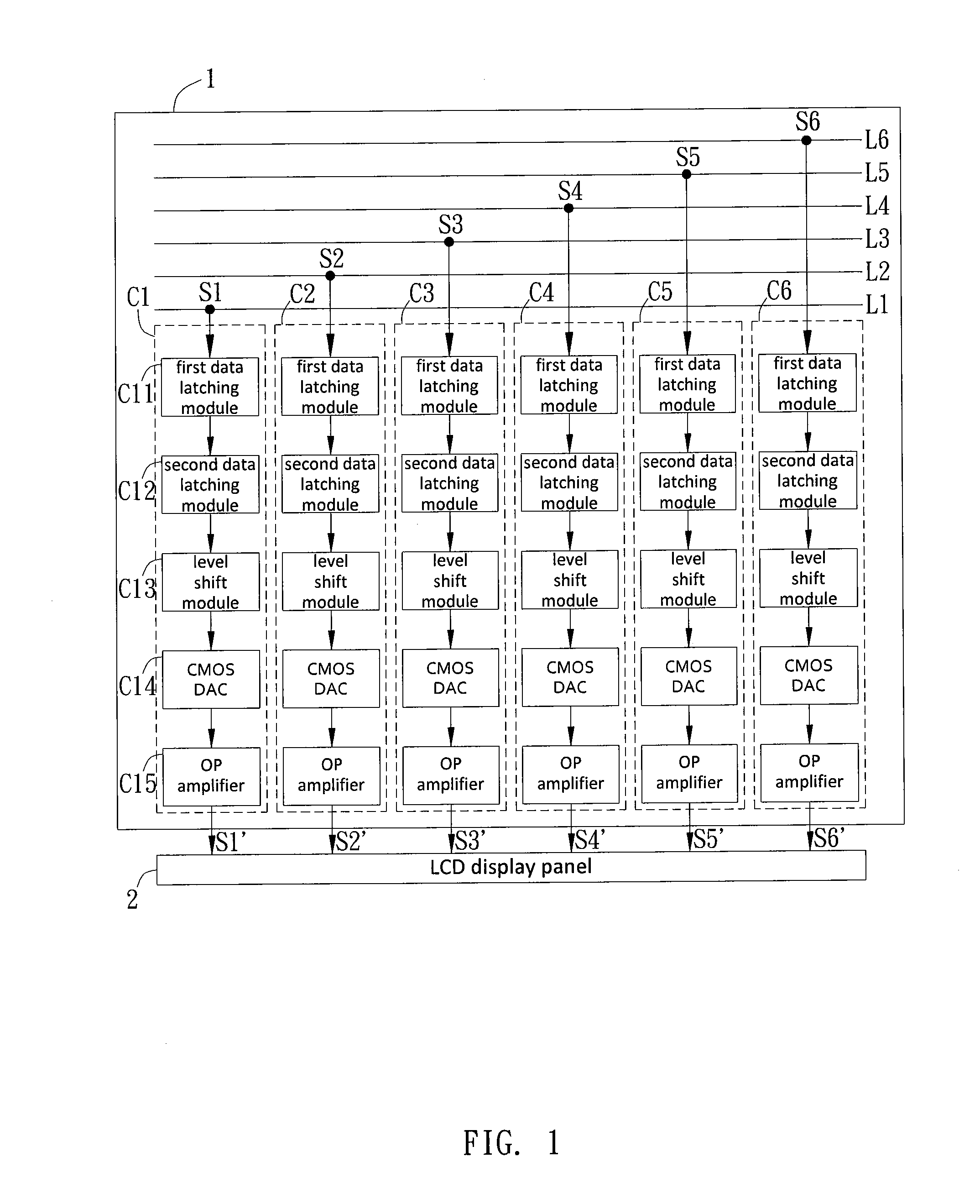

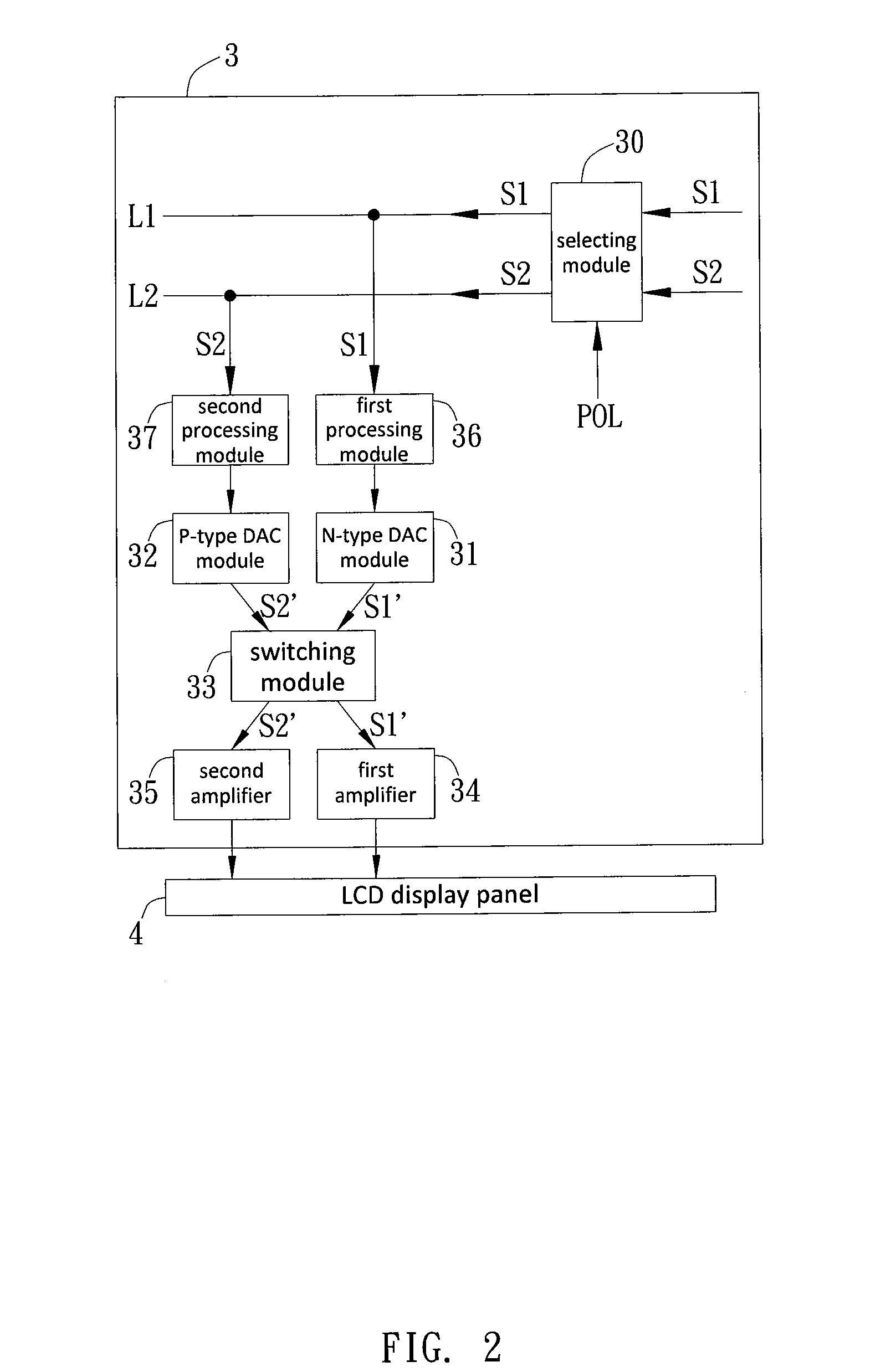

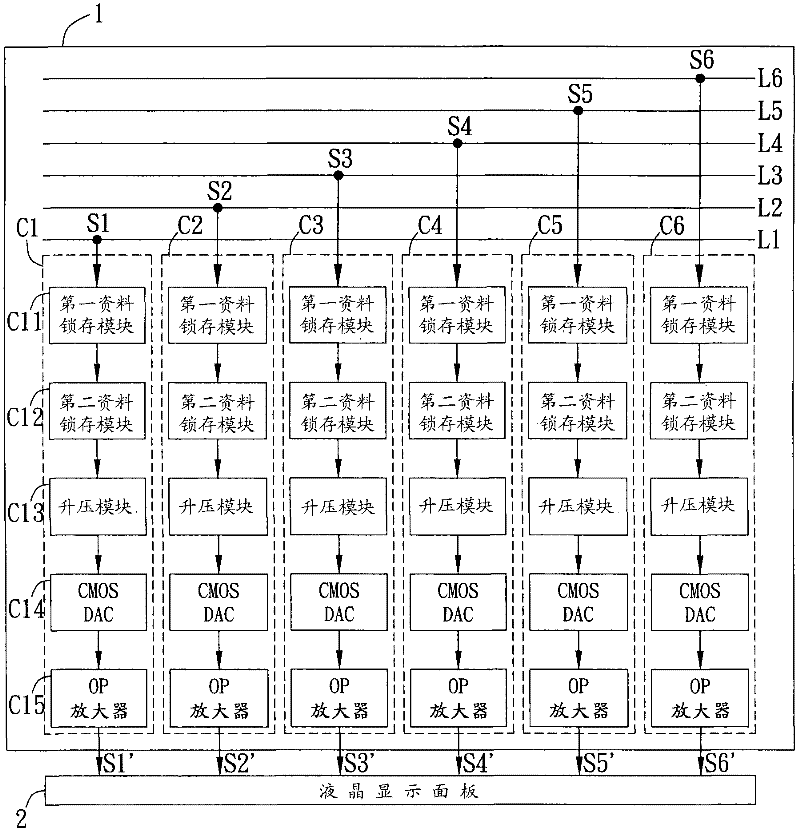

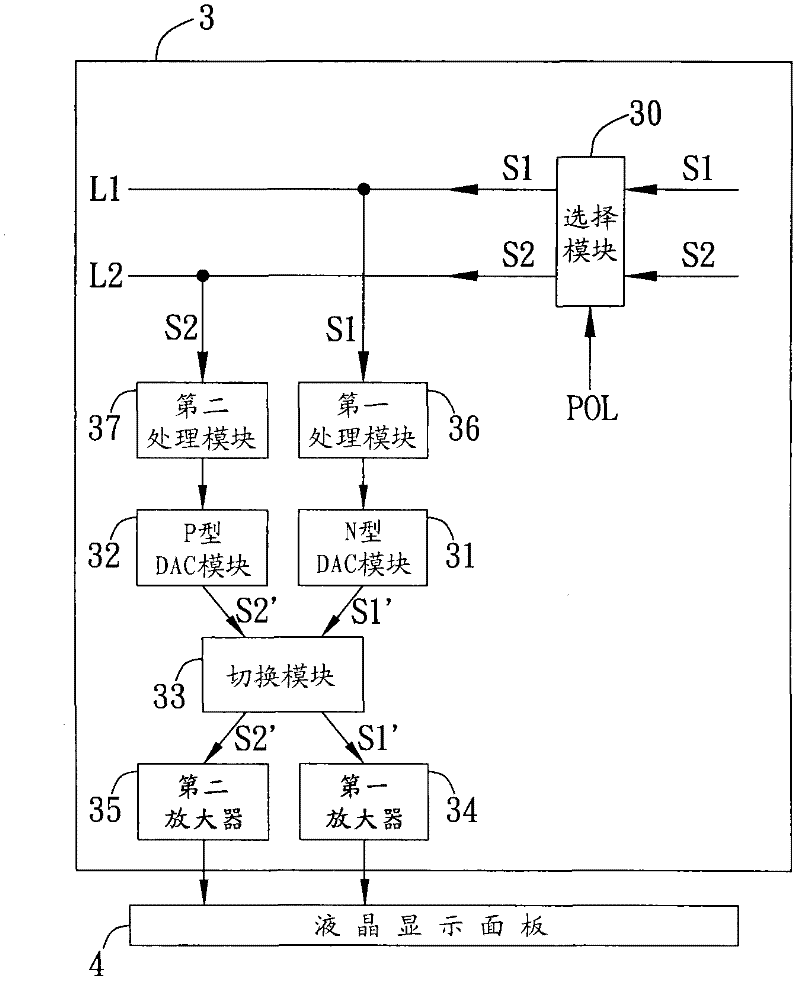

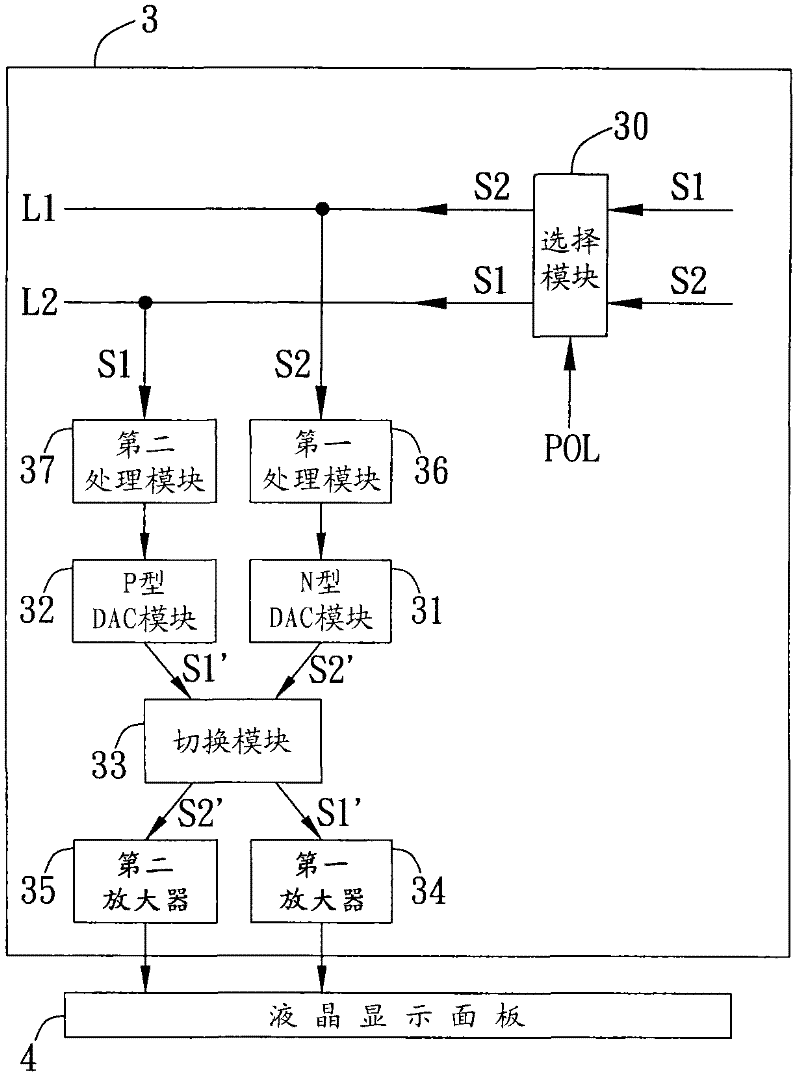

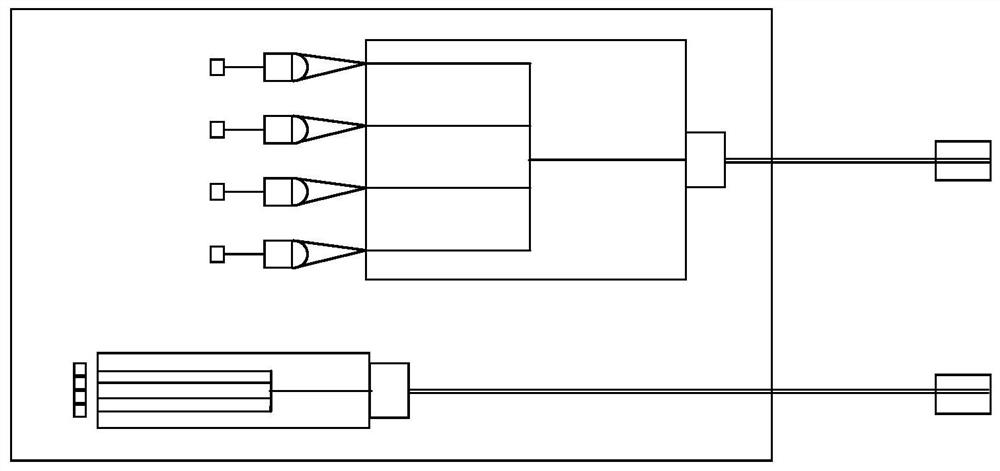

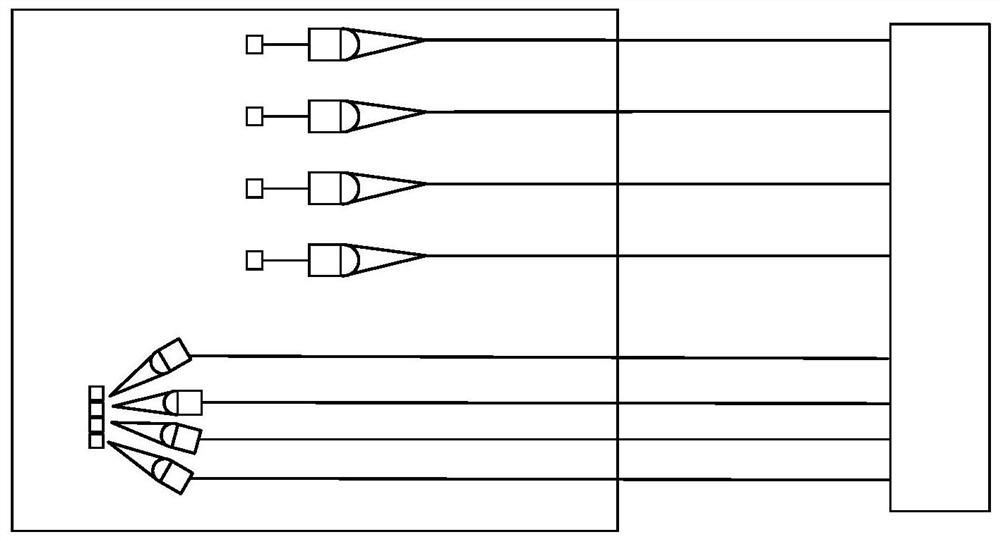

Driving circuit and operating method thereof

InactiveUS20120075263A1Reduce usageIncrease channel densityCathode-ray tube indicatorsInput/output processes for data processingComputer moduleOperation mode

A driving circuit and an operating method thereof are disclosed. The driving circuit includes at least one first channel, at least one second channel, a selecting module, and at least one switching module. The selecting module is coupled to input ends of the first channel and the second channel. The at least one switching module is coupled to output ends of the at least one first channel and the at least one second channel. The selecting module and the switching module will perform corresponding switching actions to make the driving circuit selectively under a first operating mode or a second operating mode.

Owner:RAYDIUM SEMICON

Driving circuit and operation method thereof

InactiveCN102456311AReduce the occupied areaIncrease channel densityStatic indicating devicesControl signalOperation mode

The invention discloses a driving circuit and an operation method thereof. The drive circuit comprises at least one first channel, at least one second channel, a selection module and at least one switching module. The selection module is coupled with input terminals of the first channel and the second channel; and the at least one switching module is coupled with output terminals of the at least one first channel and the at least one second channel. The selection module and the switching module carry out corresponded switching motions according to a control signal, so that the driving circuit is selectively in a first operation mode or a second operation mode.

Owner:RAYDIUM SEMICON

Preparation method for nano-TiO2 modified micro-channel reactor

ActiveCN104941553ASimple processIncrease channel densityWater/sewage treatment by irradiationEnergy based chemical/physical/physico-chemical processesIonChemistry

The invention provides a preparation method for a nano-TiO2 modified micro-channel reactor. The preparation method comprises the following steps: preparing a micro-channel reactor made of a transparent material, and cleaning the micro-channel reactor for later use; adding a titanium source in an acidic water solution or ammonia water to obtain a mixture, and stirring the mixture to form nano-TiO2 sol; injecting the nano-TiO2 sol in a channel of the later-use micro-channel reactor, staying for 5-30 min, and injecting deionized water in the channel of the micro-channel reactor for cleaning to obtain a nano-TiO2 sol particle modified micro-channel reactor; placing the nano-TiO2 sol particle modified micro-channel reactor in a 500-1,000 W infrared source to be illuminated, ultrasonically cleaning the passage with an acidic cleaning solution and deionized water in sequence, and obtaining the nano-TiO2 modified micro-channel reactor. The preparation method has the characteristics of being simple in preparation process, and easy to achieve industrial production; the micro-channel reactor, prepared according to the preparation method, has the characteristics of being high in density, convenient and high in efficiency.

Owner:QUZHOU UNIV

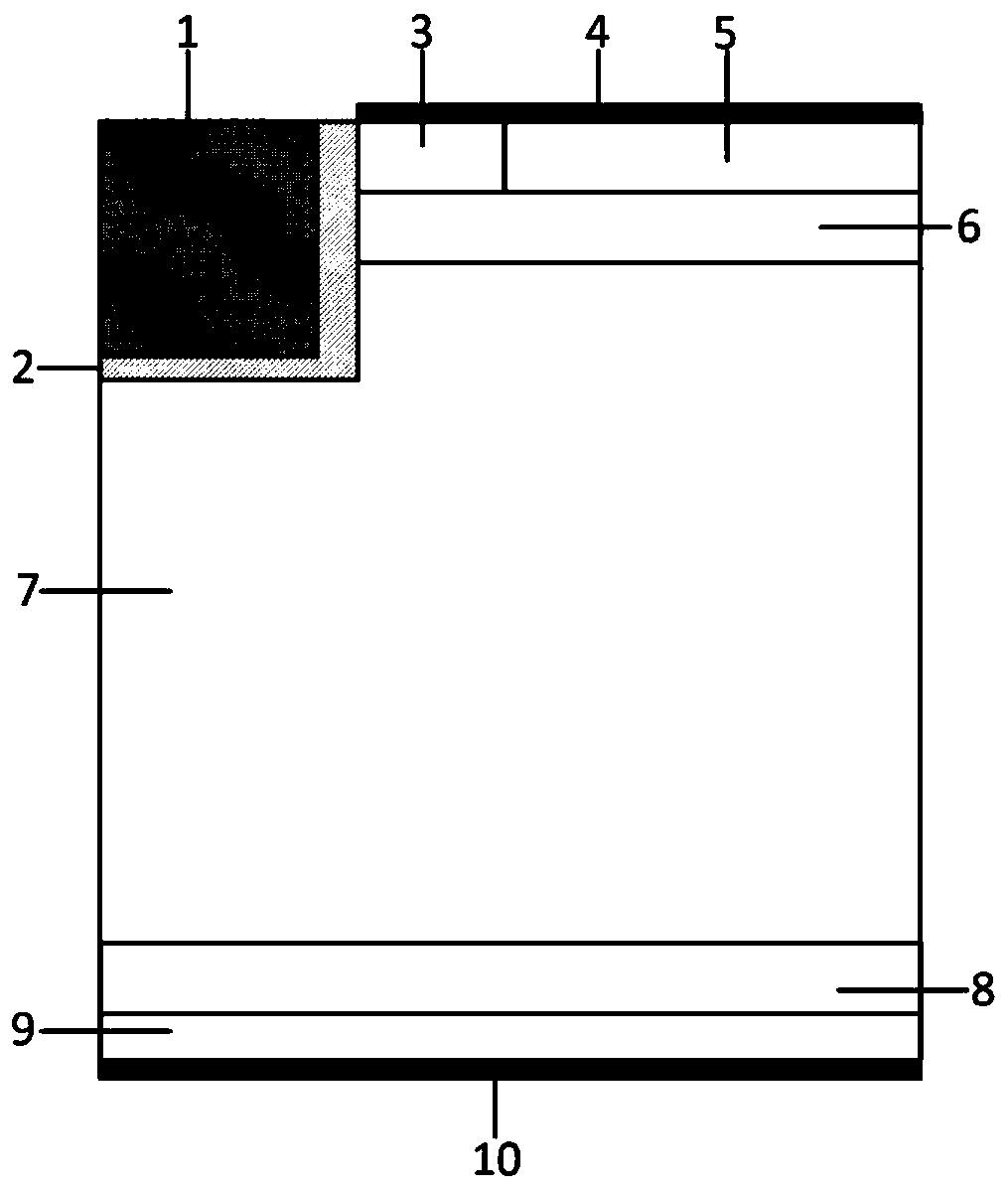

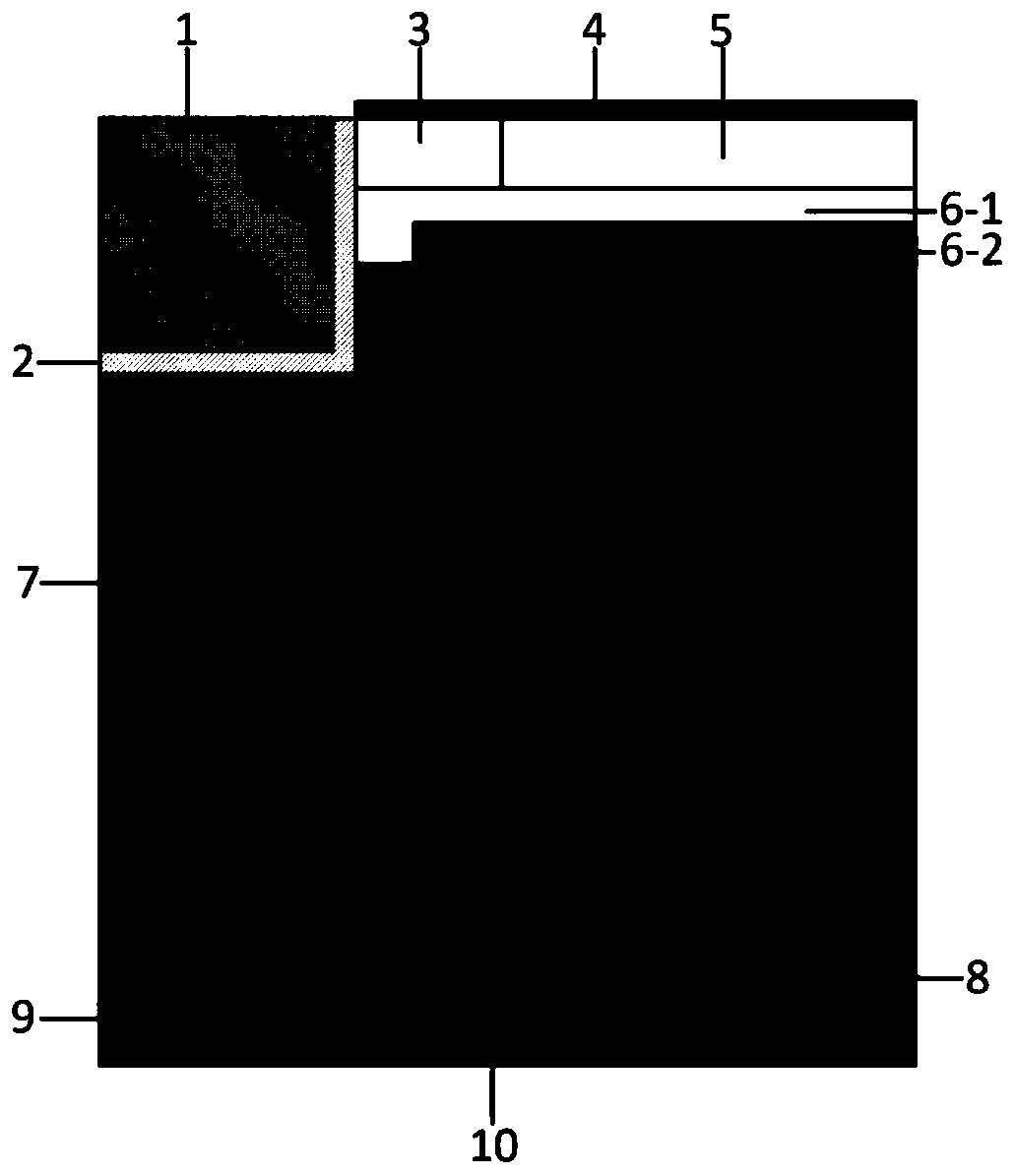

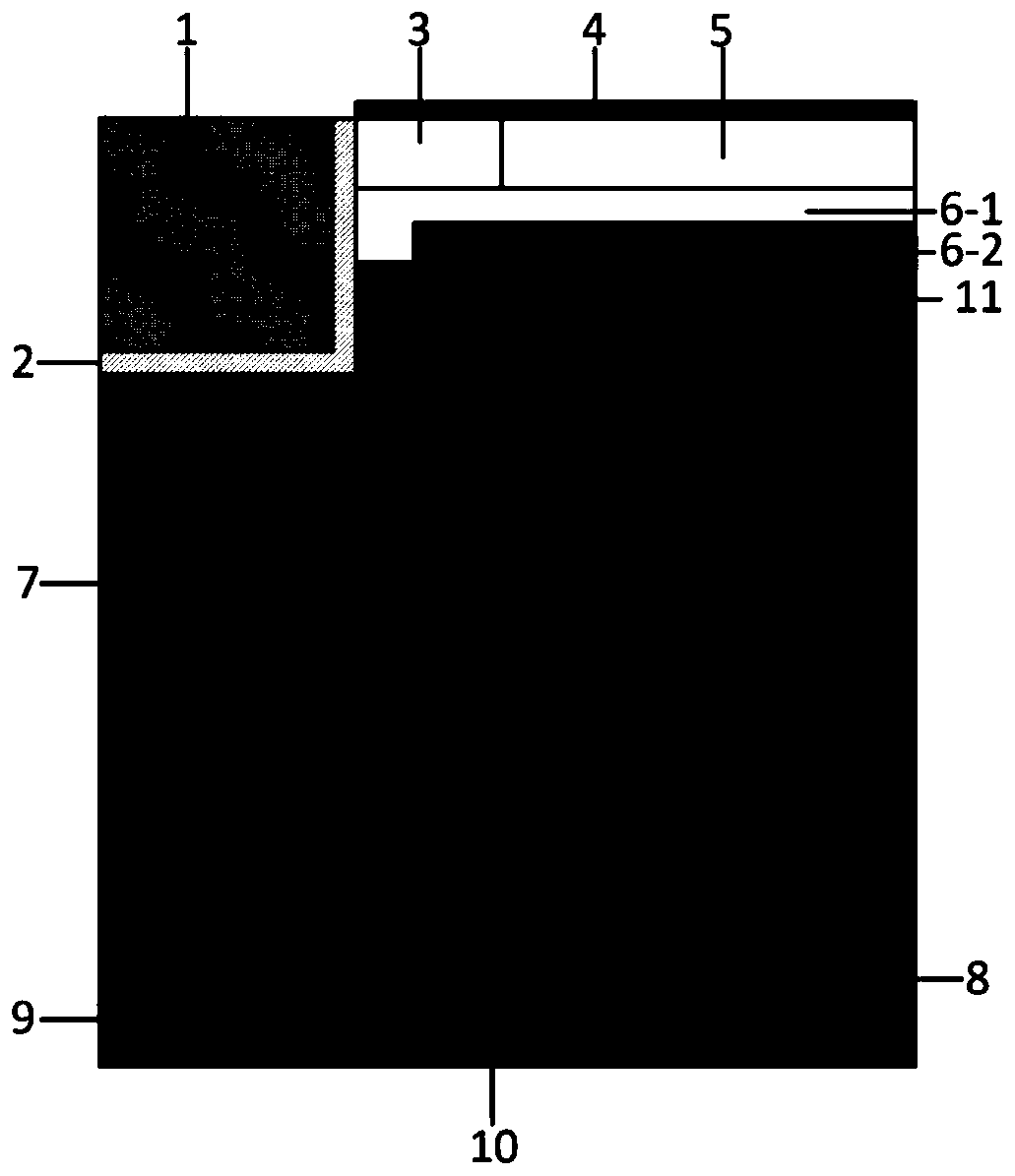

Deep groove power device and manufacturing method thereof

PendingCN109494255AGuaranteed yieldEnsure consistencySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringBody region

The invention relates to a deep groove power device, wherein the power device is divided into a cellular area and a terminal area; the power device comprises a substrate, a drain metal is arranged atthe lower portion of the substrate, an epitaxial layer is arranged on the substrate, a body region is arranged on the epitaxial layer, a cellular area groove and a terminal area groove are formed in the body area, the cellular area groove and the terminal area groove extend downwards from the surface of the body area to the inside of the epitaxial layer. The groove is filled with first conductivepolycrystalline silicon connected with the source electrode and second conductive polycrystalline silicon connected with the grid electrode. A second insulating medium body is arranged between the first conductive polycrystalline silicon and the second conductive polycrystalline silicon.

Owner:上海昱率科技有限公司

Trench type vertical double-diffusion metal oxide semiconductor field effect transistor

ActiveCN111370485AHighly integratedSmall footprintSolid-state devicesSemiconductor devicesGate dielectricEngineering

The invention relates to a VDMOS, which comprises a semiconductor substrate, a body region formed in the substrate and a source region formed in the body region, wherein a trench penetrates through the source region and the body region and extends to the substrate, each trench gate structure comprises a gate dielectric layer formed on the inner wall of the trench and a gate layer filled in the trench, a first interlayer dielectric layer, a first metal layer, a second interlayer dielectric layer and a second metal layer are sequentially stacked on the source region and each trench gate structure, one of the first metal layer and the second metal layer is a gate metal layer and is connected with each gate layer through a gate region contact hole, the other one is a source metal layer and isconnected with the body region through a source region contact hole, and the number N of the trench gate structures on the same side of the source region contact hole in each cell structure is greaterthan or equal to 2. According to the invention, the number N of the trench gate structures on the same side of the source region contact holes in the cell structure is larger than or equal to 2, so that large breakover current can be obtained under the condition that the occupied area of trench gates is small.

Owner:CSMC TECH FAB2 CO LTD

Trench gate semiconductor device and the method of manufacturing the same

InactiveUS8362549B2Increase channel densityReduce parasitic resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesChannel densityBody contact

Owner:FUJI ELECTRIC CO LTD

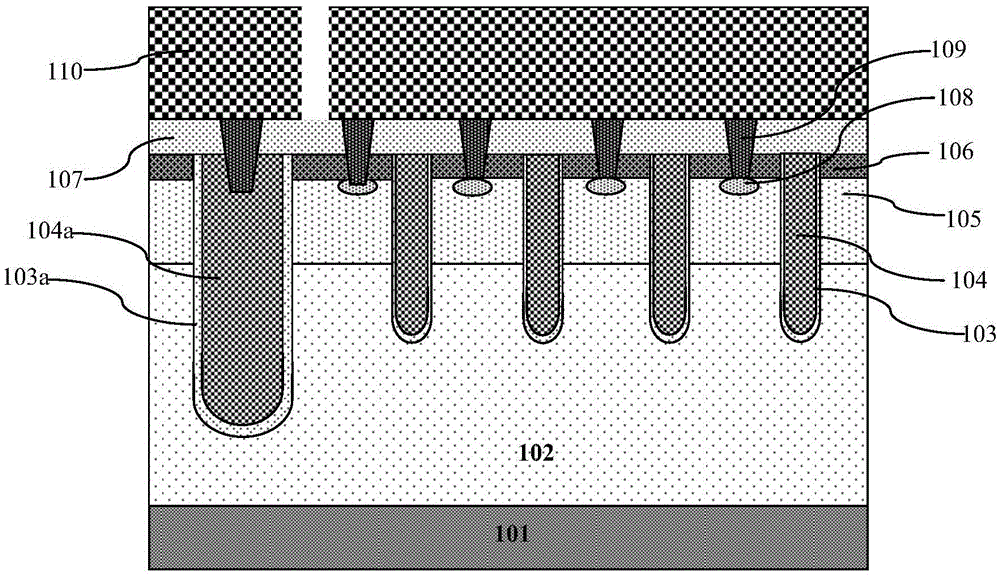

Trench type insulated gate bipolar transistor and preparation method thereof

ActiveCN110416295AReduce capacitanceFast switching speedSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsTrade offs

The invention provides a trench type insulated gate bipolar transistor and a preparation method thereof, which belong to the technical field of power semiconductors. According to the invention, a narrow bandgap semiconductor material is used to form a conductive channel and form ohmic contact with emitter metal due to the characteristics of high channel mobility of a narrow bandgap material such as silicon and small ohmic contact resistance with the emitter metal; channel resistance and ohmic resistance are reduced; the forward conduction voltage drop of a device is reduced; in addition, due to the characteristic of high critical breakdown field strength of a wide bandgap material such as silicon carbide, the device is not limited by a gate oxide layer and prevented from avalanche breakdown; the position of a breakdown point is changed; the breakdown voltage of the device is improved to a certain extent, so that the thickness of a drift region can be appropriately reduced at a certainvoltage level; the forward conduction voltage drop and the turn-off loss are further reduced; and the trade-off relationship between the turn-on voltage drop and the turn-off loss is optimized. In addition, the invention further provides a preparation method of the trench type insulated gate bipolar transistor.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Separated gate VDMOS device with high channel density and manufacturing method thereof

InactiveCN110491935AIncrease the conductive channelIncrease channel densitySemiconductor/solid-state device manufacturingSemiconductor devicesConductive channelOxide

The invention provides a separated gate VDMOS device with high channel density and a manufacturing method. The device comprises a first conductive type substrate, a first conductive type drift region,a first conductive type source electrode contact region, a second conductive type well region, a second conductive type source end contact region, a source electrode metal contact, a first dielectricoxide layer, a second dielectric oxide layer, a third dielectric oxide layer, a fourth dielectric oxide layer, a control gate polycrystalline silicon electrode and a separation gate polycrystalline silicon electrode. According to the invention, a control gate shallow groove is introduced into a device mesa region; the limitation of the existing process is met and the width of the device mesa region is not reduced; the conductive channel is added, the channel density of the device is improved, and the introduced control gate shallow groove hardly influences the withstand voltage of the device,so that the VDMOS provided by the invention has lower specific on resistance under the condition of keeping the same withstand voltage of the device, and the working loss of the device is reduced.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

MOS power device and manufacturing method thereof

PendingCN107680933AReduce lossReduce conduction voltage dropSemiconductor/solid-state device detailsSolid-state devicesEtchingElectrical conductor

The present invention discloses a MOS (Metal Oxide Semiconductor) power device and a manufacturing method thereof. The method comprises the steps that: generating a first insulation dielectric layer,a first semiconductor layer, a second insulation dielectric layer and a second semiconductor layer in order above the substrate, and forming a first multi-layer structure; performing etching on the first multi-layer structure until a partial region of the first insulation dielectric layer is exposed, and forming a second multi-layer structure; injecting impurities in the substrate to form a well region and source region in the substrate, and obtaining a third multi-layer structure; depositing a third insulation dielectric layer above the third multi-layer structure, and forming a fourth multi-layer structure; performing etching of the fourth multi-layer structure through a self-aligned mode, forming a connection hole, and forming a fifth multi-layer structure; and depositing a metal layerabove the fifth multi-layer structure, and forming an emission electrode. Therefore, migration is avoided, and consistency and stability of performance parameters of an MOS power device can be ensured.

Owner:BYD SEMICON CO LTD

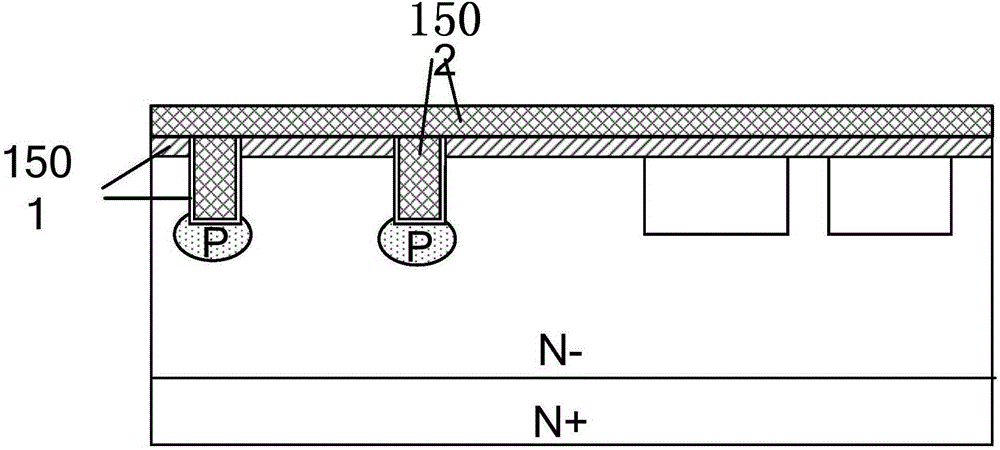

Rectifier and manufacturing method thereof

ActiveCN104517961AReduce manufacturing costSimple processSolid-state devicesSemiconductor/solid-state device manufacturingBiochemical engineeringRectifier diodes

The invention provides a rectifier and a manufacturing method thereof. The rectifier comprises a cellular region and a protection ring region. The cellular region comprises multiple rectifier diodes. Each rectifier diode comprises a substrate, an epitaxial layer arranged on the substrate, a P-type region arranged on the epitaxial layer, a groove penetrating through the P-type region, groove poly-crystalline silicon arranged in the groove, an oxide layer arranged between the groove wall of the groove and the groove poly-crystalline silicon, an N+ region arranged in the P-type region and positioned at the two sides of the groove, a front surface metal layer arranged on the P-type region, the N+ region and the groove poly-crystalline silicon, and a back surface metal layer arranged at the back surface of the substrate. The rectifier adopts a groove-type MOS structure so that parasitic JFET resistance is eliminated, and forward conduction voltage drop of the rectifier can be further reduced. Meanwhile, area of the chip is reduced and cost of the device is reduced. The manufacturing method of the rectifier adopts four photo-etching boards of a protection ring photo-etching board, a groove photo-etching board, a source region photo-etching board and a metal photo-etching board so that the manufacturing method of the rectifier has advantages of being simple in technology and low in manufacturing cost.

Owner:CSMC TECH FAB2 CO LTD

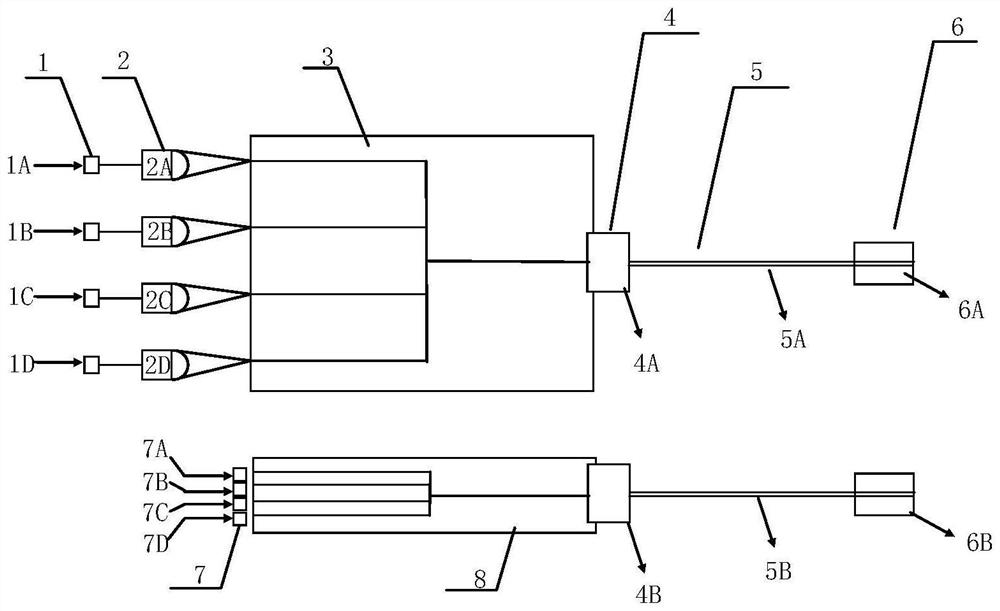

Multi-channel optical module based on double LC interfaces

The invention discloses a multi-channel optical module based on double LC interfaces, and belongs to the technical field of optical modules. The optical module comprises an LD module with N channels, a multi-core optical fiber fan-in device with N input ports, a multi-core optical fiber which is coupled with the output port of the multi-core optical fiber fan-in device and is provided with N cores, and a multi-core optical fiber LC connector which is connected with the multi-core optical fiber, which are sequentially arranged along the direction of an output optical axis; the other multi-core optical fiber LC connector, the other N-core multi-core optical fiber connected with the other multi-core optical fiber LC connector, the multi-core optical fiber fan-out device coupled with the other N-core multi-core optical fiber and provided with N output ports, and a detector array connected with the N output ports of the multi-core optical fiber fan-out device, which are sequentially arranged in the direction of the input optical axis. According to the invention, the transmission of the optical module with 2N transceiving channels can be realized by using two multi-core optical fibers with N cores, so that the overall cost is better while the wiring space is saved.

Owner:YANGTZE OPTICAL FIBRE & CABLE CO LTD

Preparation method of nano-titanium dioxide modified microchannel reactor

ActiveCN104941553BSimple processEase of industrial productionWater/sewage treatment by irradiationEnergy based chemical/physical/physico-chemical processesVolumetric Mass DensityAmmonia

The invention provides a preparation method for a nano-TiO2 modified micro-channel reactor. The preparation method comprises the following steps: preparing a micro-channel reactor made of a transparent material, and cleaning the micro-channel reactor for later use; adding a titanium source in an acidic water solution or ammonia water to obtain a mixture, and stirring the mixture to form nano-TiO2 sol; injecting the nano-TiO2 sol in a channel of the later-use micro-channel reactor, staying for 5-30 min, and injecting deionized water in the channel of the micro-channel reactor for cleaning to obtain a nano-TiO2 sol particle modified micro-channel reactor; placing the nano-TiO2 sol particle modified micro-channel reactor in a 500-1,000 W infrared source to be illuminated, ultrasonically cleaning the passage with an acidic cleaning solution and deionized water in sequence, and obtaining the nano-TiO2 modified micro-channel reactor. The preparation method has the characteristics of being simple in preparation process, and easy to achieve industrial production; the micro-channel reactor, prepared according to the preparation method, has the characteristics of being high in density, convenient and high in efficiency.

Owner:QUZHOU UNIV

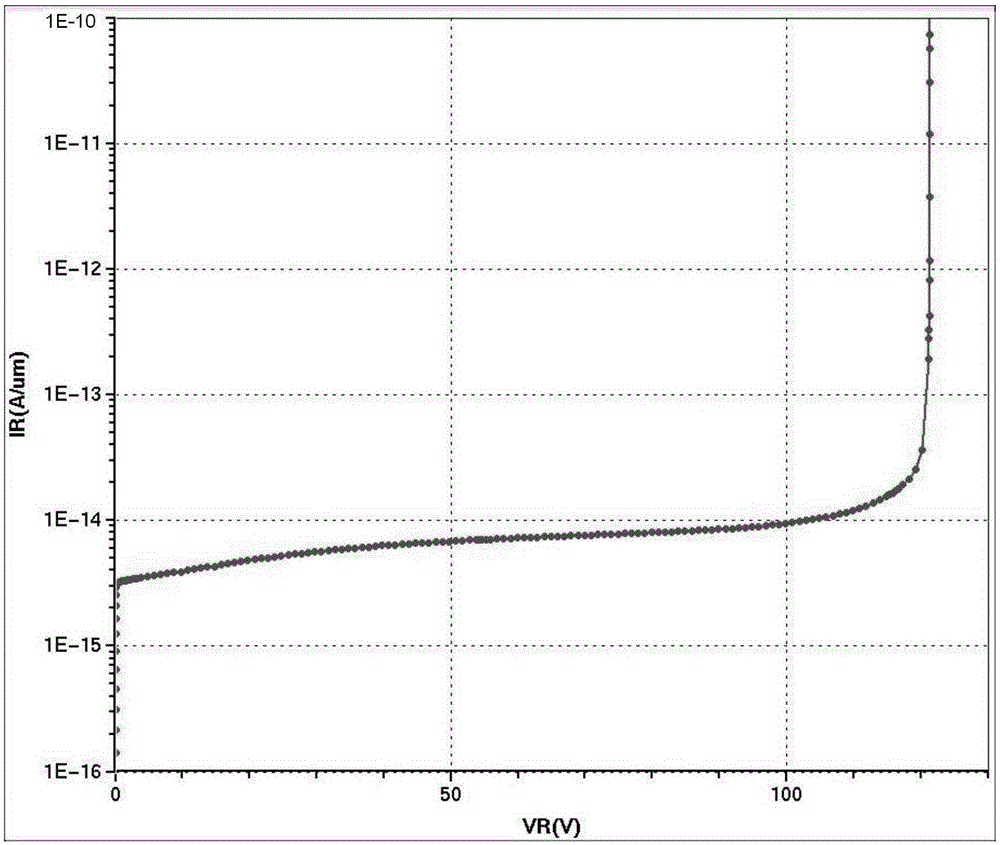

Trench gate super-barrier rectifier

InactiveCN109873029ALower channel resistanceIncrease channel densitySemiconductor devicesElectrical resistance and conductanceLead bonding

The invention provides a trench gate super-barrier rectifier, and belongs to the technical field of semiconductor power devices; the improvement of an existing super-barrier rectifier is as follows: atrench gate structure is adopted to replace a plane gate structure; on one hand, the cell size of the trench gate super-barrier rectifier is small, and the channel resistance is low; on the other hand, a gate oxide layer is located below the surface of a silicon wafer, so that damage to a lead bonding process is avoided, and the reliability is improved; and in addition, a channel region can be formed by adopting a conventional ion implantation method, so that the repeatability and the yield are high.

Owner:GUIZHOU E CHIP MICROELECTRONICS TECH CO LTD

Power semiconductor device with L shaped source

InactiveCN1862830ADoes not affect electrical propertiesReduce spacingSemiconductor devicesPower semiconductor deviceBody area

This invention relates to L type source region power semiconductor device. It includes one substrate, one trap area formed in the substrate, one body area formed on trap area, one groove grid formed at both sides of the trap area, one grid oxide layer is formed on the lateral wall and bottom surface of the groove grid, one L type source region, and one flat roof area and one straight lateral area are formed on roof and sides of the body, one dielectric insulating layer formed on the groove grid area and part of the L type area, and one contact window is defined, one metal layer formed on the insulating layer, the body and the L type area, and it is connected to the L type area through the contact window to form the power semiconductor device with L type area flush type groove grid.

Owner:ONIZUKA ELECTRONICS

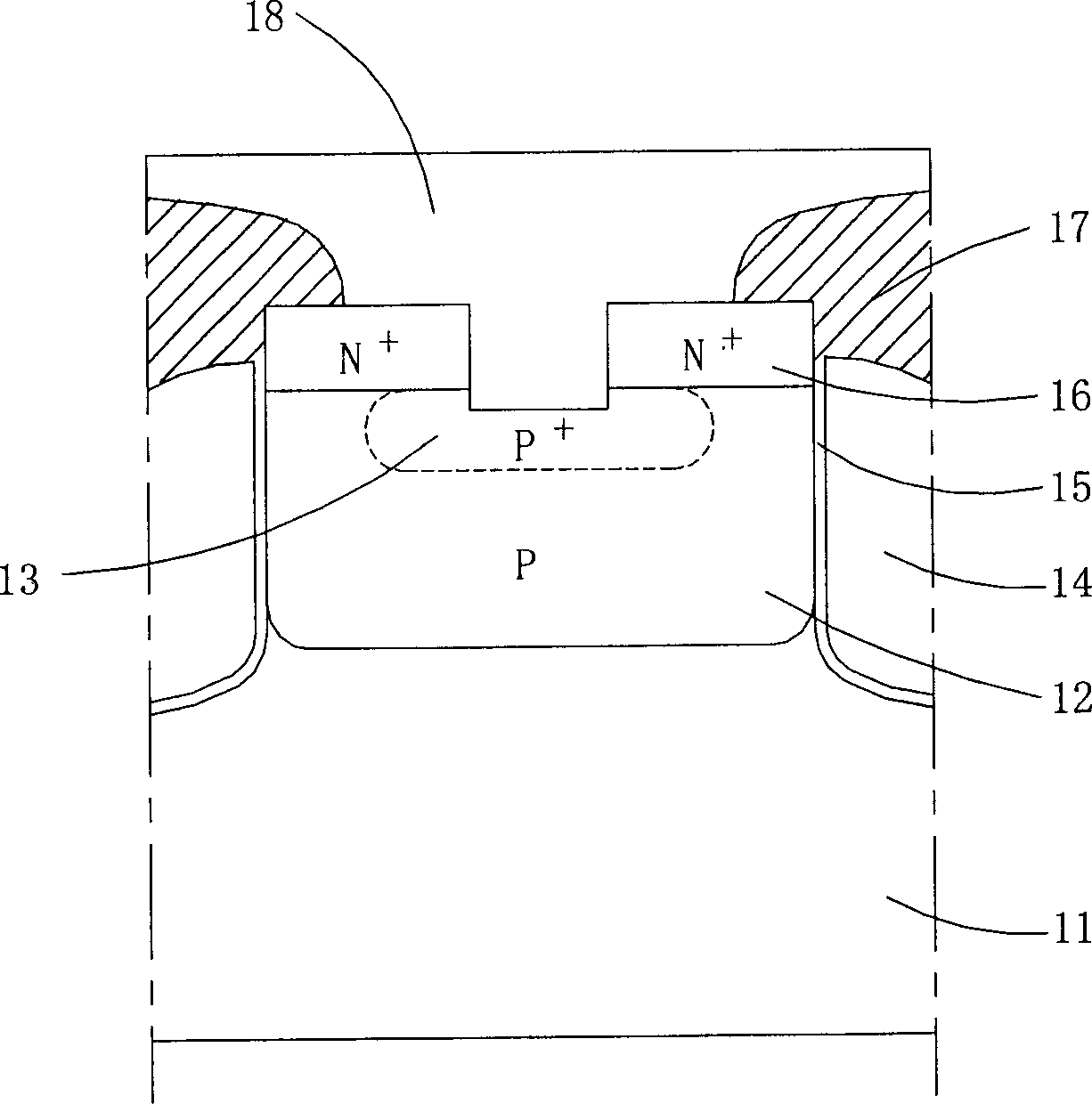

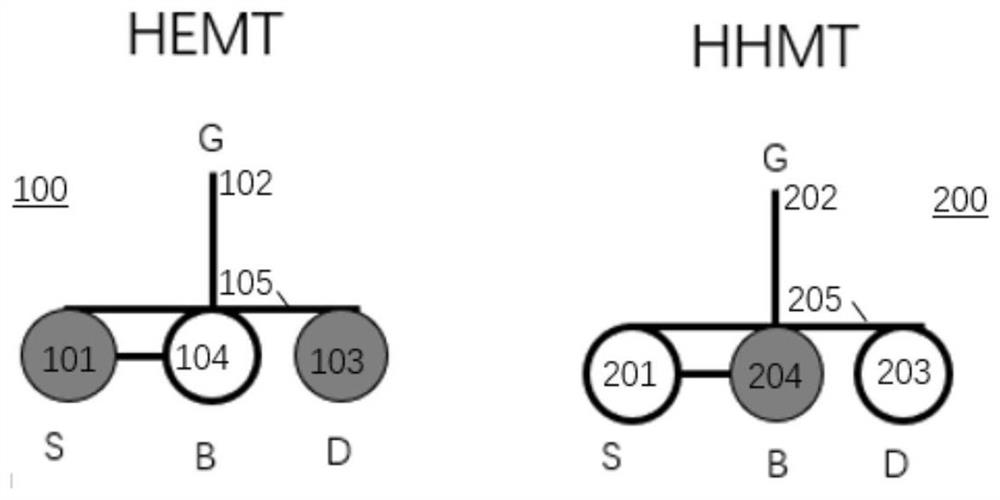

Group III nitride semiconductor integrated circuit structure, manufacturing method and application thereof

PendingCN113571516ALower on-resistanceReduce parasitic inductanceTransistorSolid-state devicesCMOSConduction current

The invention provides a group III nitride semiconductor integrated circuit structure, a manufacturing method and application thereof. The integrated circuit structure is a complementary circuit based on an HEMT and an HHMT of a group III nitride semiconductor, integration of the HEMT and the HHMT can be achieved on the same substrate, the HEMT and the HHMT are respectively provided with polarization junctions of a vertical interface, the crystal orientations of the polarization junctions of the HEMT and the HHMT are different, two-dimensional carrier gas forms a carrier channel in the direction parallel to the polarization junctions, and almost depleting the corresponding channel carriers by means of the buried doped region. Compared with a traditional silicon-based CMOS, the integrated circuit structure has the advantages in the aspects of carrier mobility, conduction current density, switching speed and the like, low conduction resistance, low parasitic inductance and a normally-off state of a device can be achieved, and the technical effects of higher conduction current density, higher integration level and small energy consumption can be achieved.

Owner:GUANGDONG ZHINENG TECH CO LTD

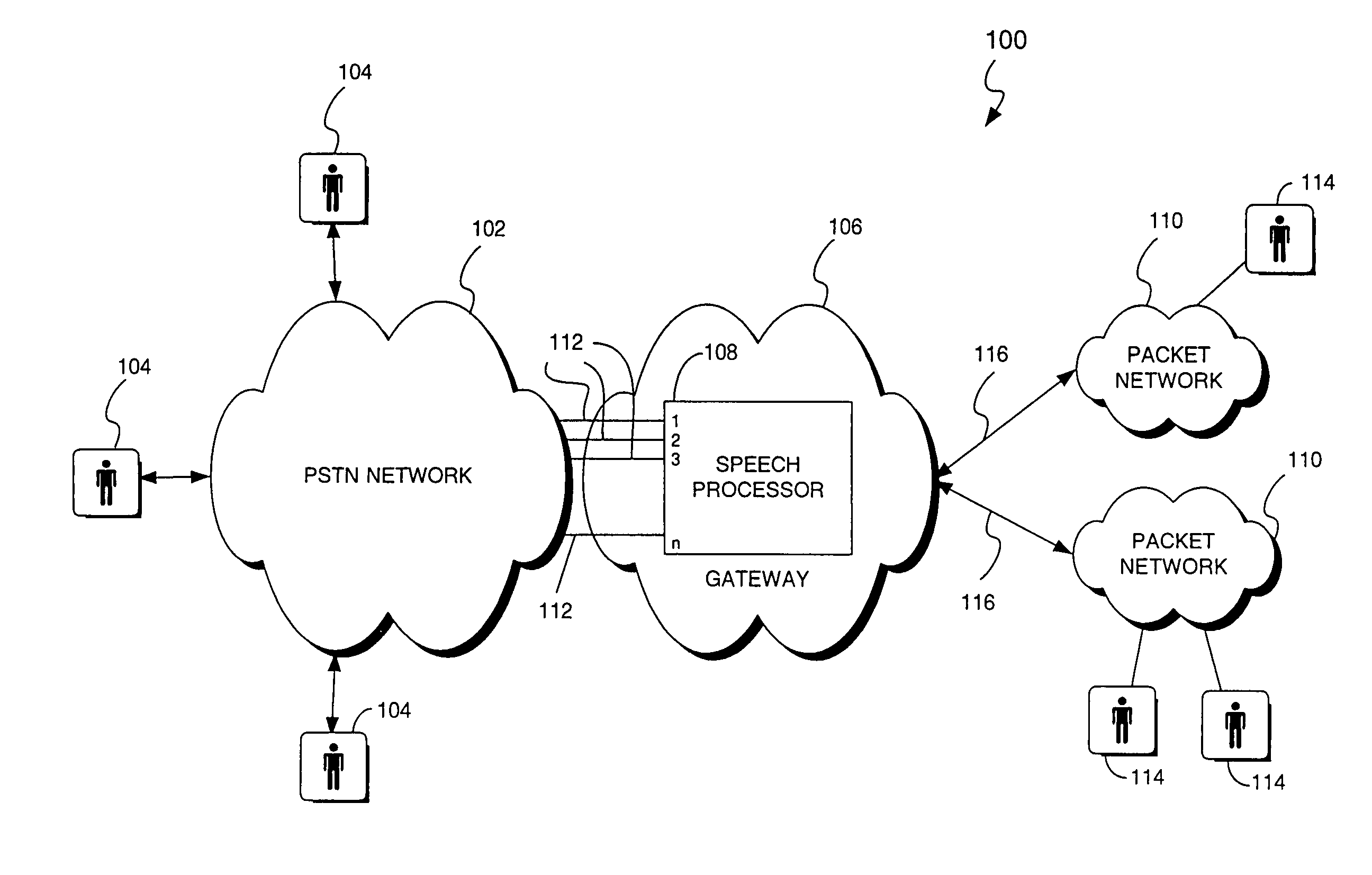

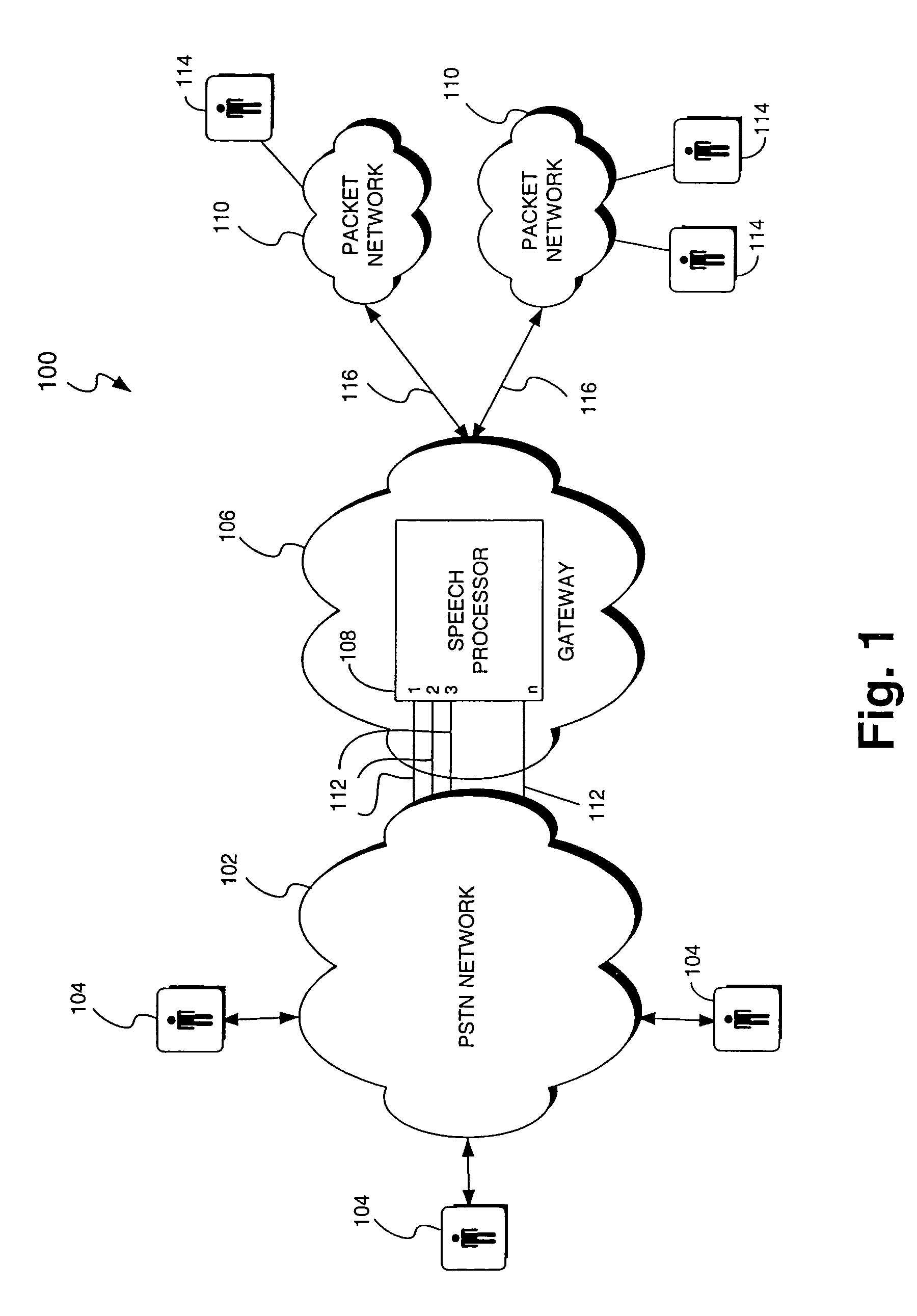

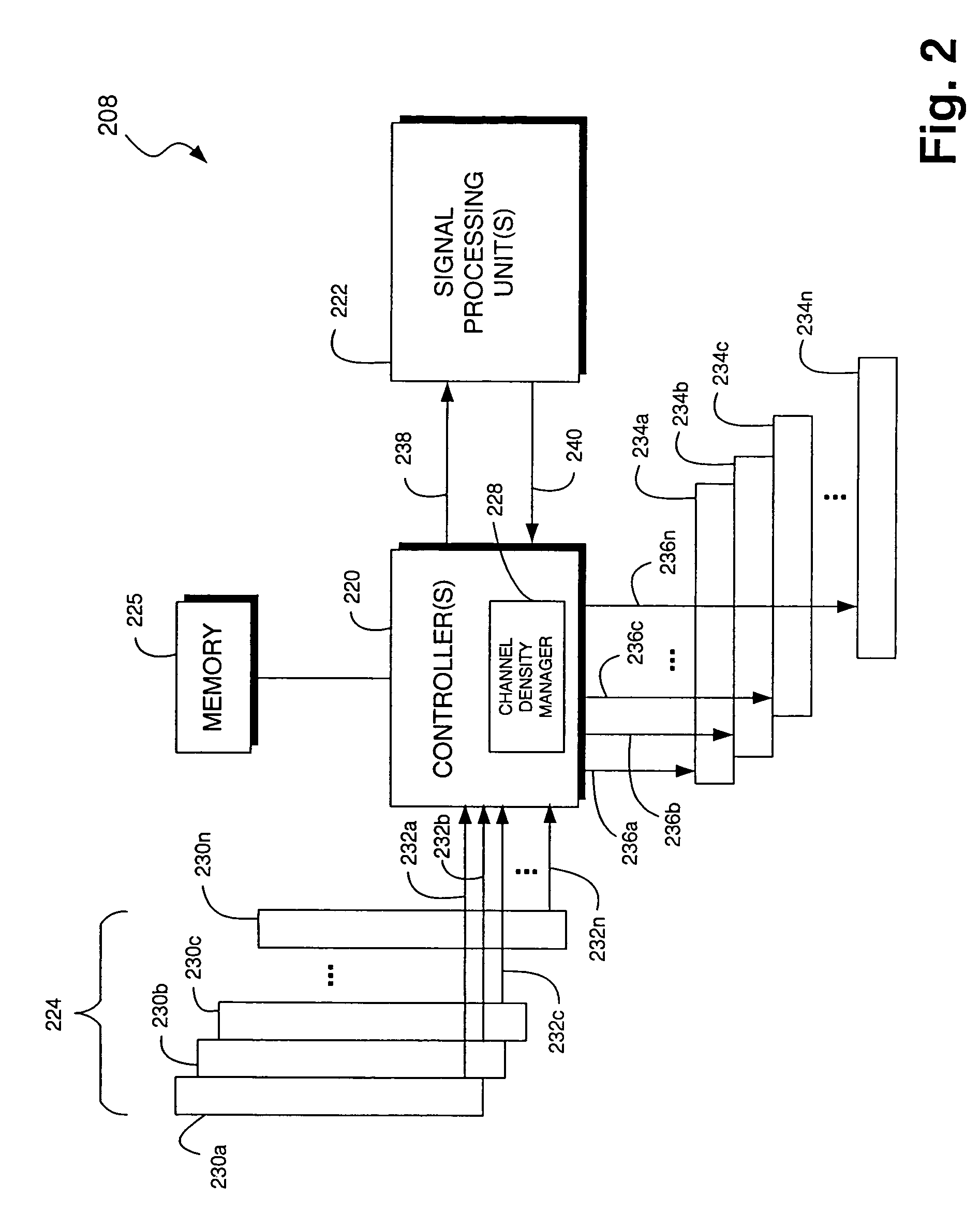

Method and system for supporting increased channel density

InactiveUS7076421B2Increase channel densityEffective distributionMultiplex communicationSpeech analysisChannel densitySpeech Processor

An exemplary multi-channel speech processor comprises a controller capable of interfacing with a plurality of channels, and at least one signal processing unit (SPU) coupled to the controller, where the multi-channel speech processor has a maximum execution time for processing all frames, one channel at a time, by processing a single frame from each of the plurality of channels. The signal processing unit encodes each of the single frames from each of the plurality of channels, one channel at a time, to generate encoded frames until the maximum execution time elapses or is about to elapse. The controller also transmits a predetermined frame for each of the plurality of channels not processed during the encoding step, due to the maximum execution time elapsing or being about to elapse, such that the predetermined frame causes a decoder which receives the predetermined frame to generate a frame erase frame.

Owner:MACOM TECH SOLUTIONS HLDG INC