Rectifier and manufacturing method thereof

A manufacturing method and rectifier technology, which are applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve the problems of reducing the forward voltage drop of the device, limiting the channel density, limiting the cost of the device, etc., so as to reduce the positive voltage. Effects of conduction voltage drop, low manufacturing cost, and increased channel density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

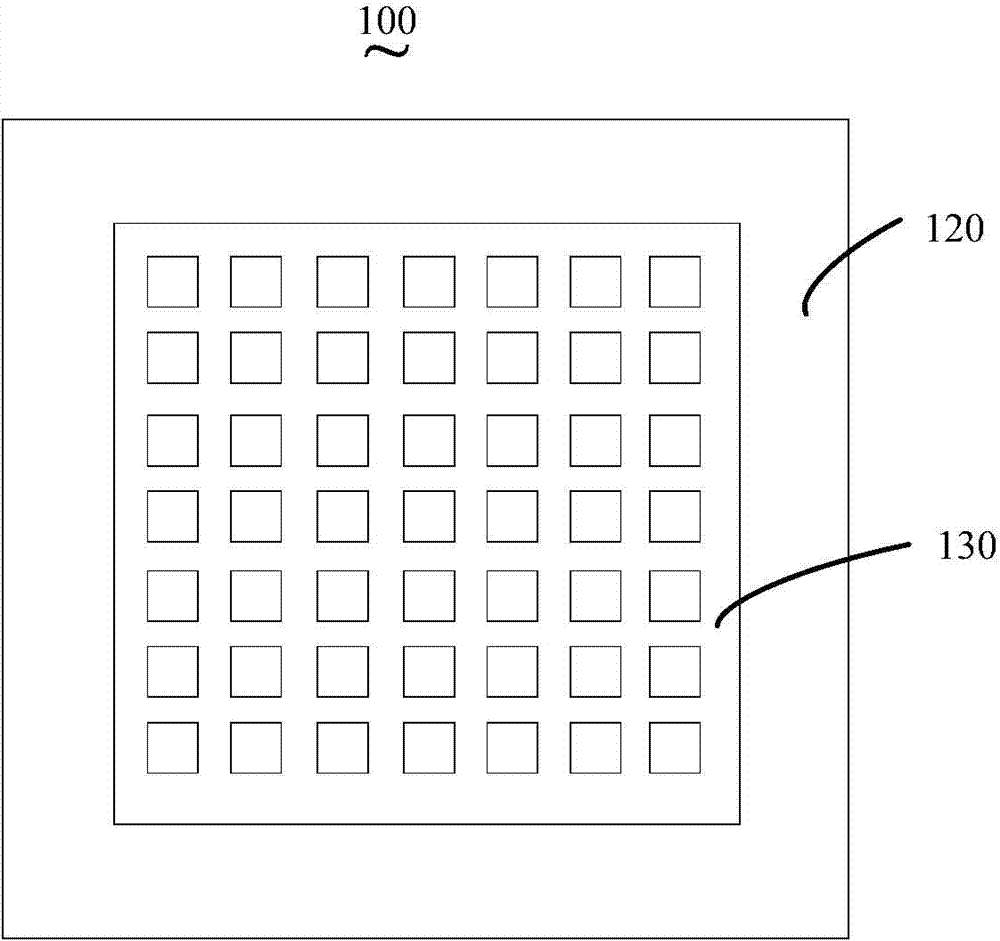

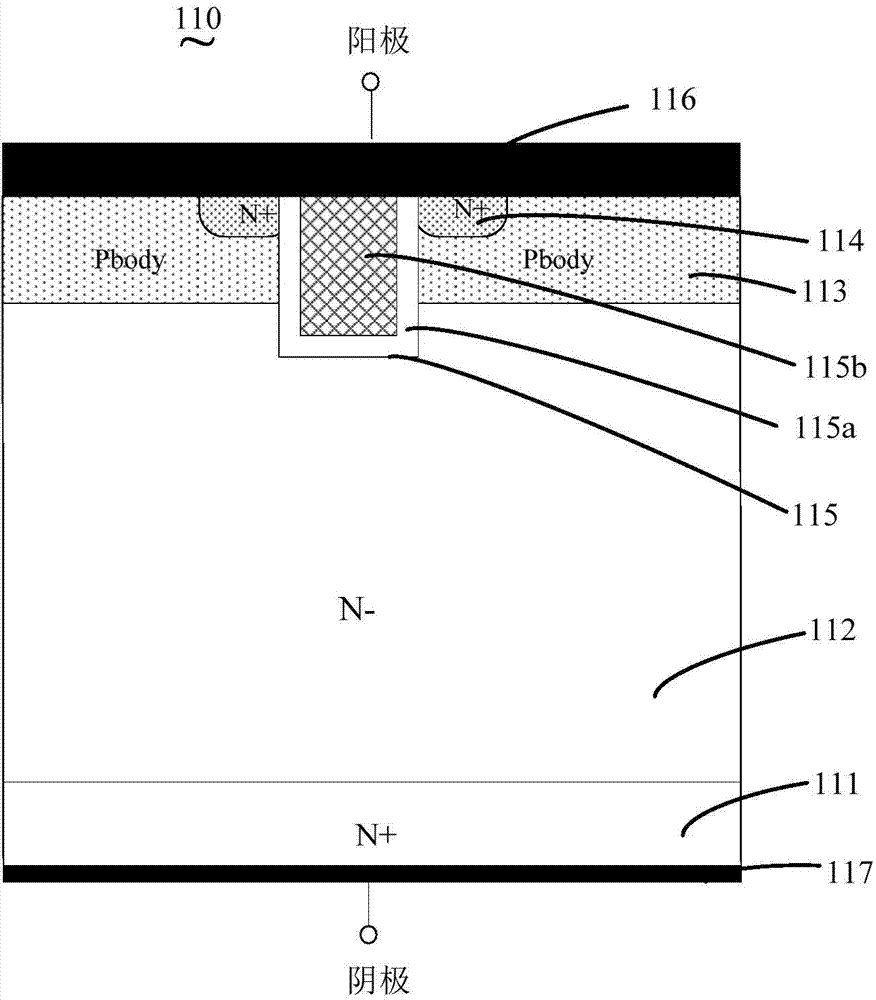

[0024] Please refer to figure 1 and figure 2 , an embodiment provides a rectifier 100 . The rectifier 100 includes a cell region 130 and a guard ring region 120 around the cell region 130 . The cell region 130 includes a plurality of rectifier diodes 110 . The guard ring area 120 includes a plurality of guard rings, and the guard rings can function to improve the withstand voltage of the rectifier 100 . Among them, refer to figure 2 , the rectifier diode 110 includes a substrate 111, an epitaxial layer 112 located on the substrate 111, a P-type region 113 located on the epitaxial layer 112, a trench 115 penetrating through the P-type region 113, and a trench disposed in the trench 115. polysilicon 115b, an oxide layer 115a between the trench wall of the trench 115 and the polysilicon 115b, an N+ region 114 located in the P-type region 113 and on both sides of the trench 115, a P-type region 113, and an N+ region 114 and the front metal layer 116 on the channel polysilic...

Embodiment 2

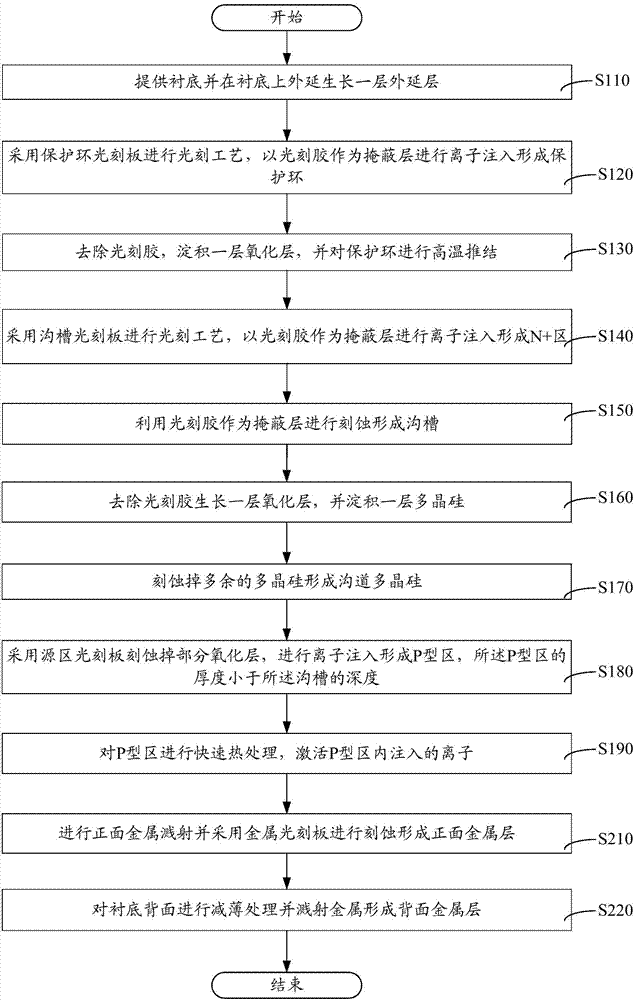

[0027] Please refer to image 3 , another embodiment provides a method for manufacturing a rectifier 100 . The manufacturing method of the rectifier 100 includes the following steps.

[0028] Step S110 , providing a substrate 111 and epitaxially growing an epitaxial layer 112 on the substrate 111 . Please refer to Figure 4, the substrate 111 used in the rectifier 100 is an N-type substrate 111 , the crystal orientation is , and the epitaxial layer 112 is an N-type epitaxial layer 112 . The thickness of the epitaxial layer 112 is 2-20 microns, and the resistivity of the epitaxial layer 112 is 0.5-5 Ω·cm. Here, the thickness and resistivity of the epitaxial layer 112 are designed according to the actual withstand voltage requirement. In addition, there is an oxide layer 115a above the epitaxial layer 112, and the oxide layer 115a can prevent loss of the epitaxial layer 112 during ion implantation.

[0029] In step S120 , a photolithography process is performed using a guar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com