Trench gate power MOSFET (Metal Oxide Semiconductor Field Effect Transistor) and manufacturing method thereof

A manufacturing method and trench gate technology are applied in the manufacture of trench gate power MOSFETs and in the field of trench gate power MOSFETs, which can solve the problems of increasing channel density, reducing on-resistance, poor channel turn-on voltage uniformity, etc. The effect of reducing pitch and increasing channel density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

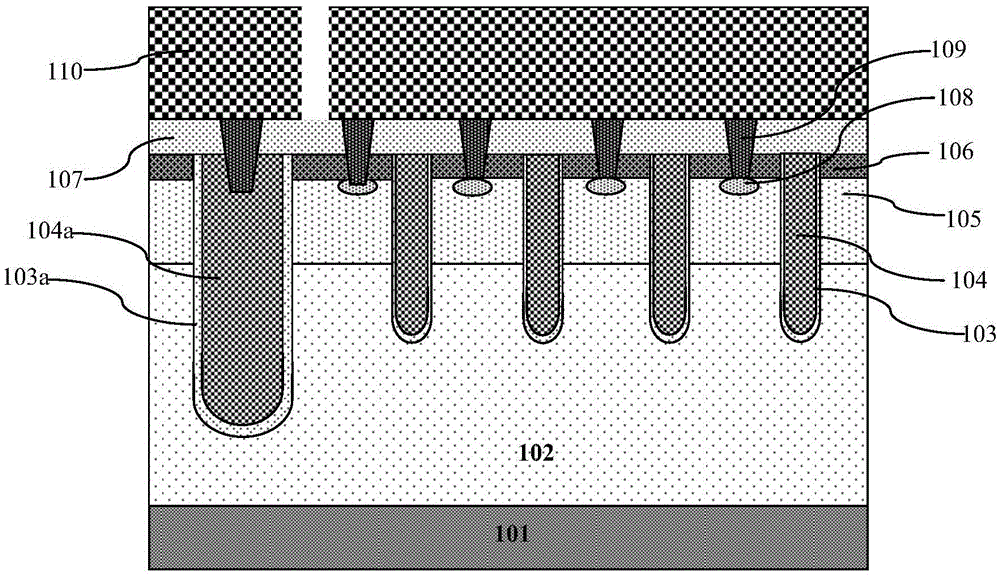

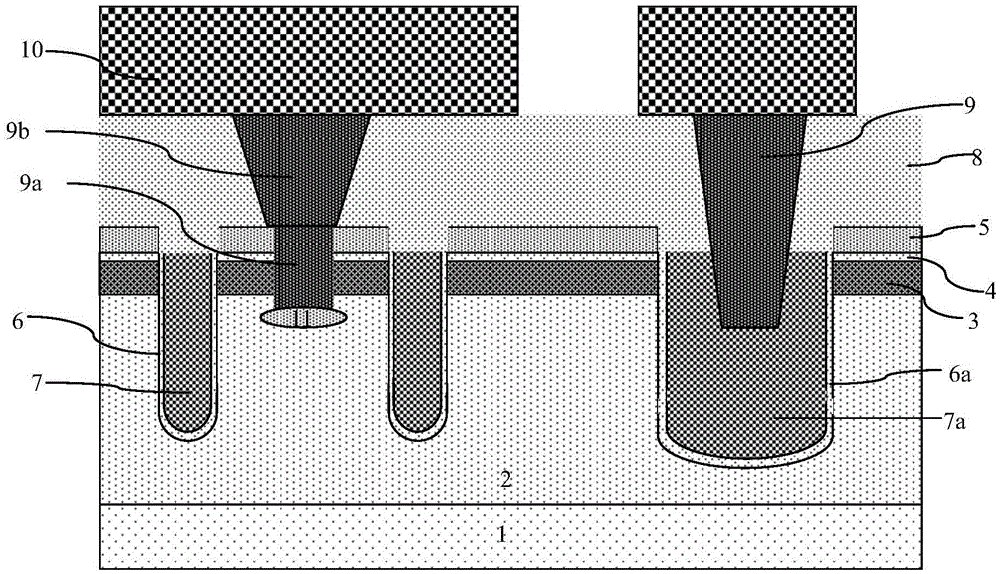

[0054] Such as figure 2 As shown, it is a schematic structural diagram of a trench gate power MOSFET according to an embodiment of the present invention; the trench gate power MOSFET according to an embodiment of the present invention includes:

[0055] A semiconductor epitaxial layer 1, the semiconductor epitaxial layer 1 is formed on the surface of a semiconductor substrate. Preferably, the semiconductor substrate is a silicon substrate, and the semiconductor epitaxial layer 1 is a silicon epitaxial layer.

[0056] A hard mask layer formed by stacking the first silicon oxide layer 4 and the second silicon nitride layer 5 is formed on the surface of the semiconductor epitaxial layer 1, and a first trench is formed in the hard mask layer. The gate groove pattern and the source region contact hole pattern defined by the mask plate at the same time; the bottom region 9a with a plurality of gate trenches and a plurality of source region contact holes is formed in the semiconduc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More