Semiconductor structure and forming method thereof

A semiconductor and wet etching technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, transistors, etc., can solve the problems of device reliability decline, semiconductor structure performance reduction, fin damage, etc., to reduce consumption and improve Fin width uniformity and height uniformity, effect of improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The performance of the current semiconductor structure still needs to be improved. Now combined with a method of forming a semiconductor structure to analyze the reasons why its performance still needs to be improved.

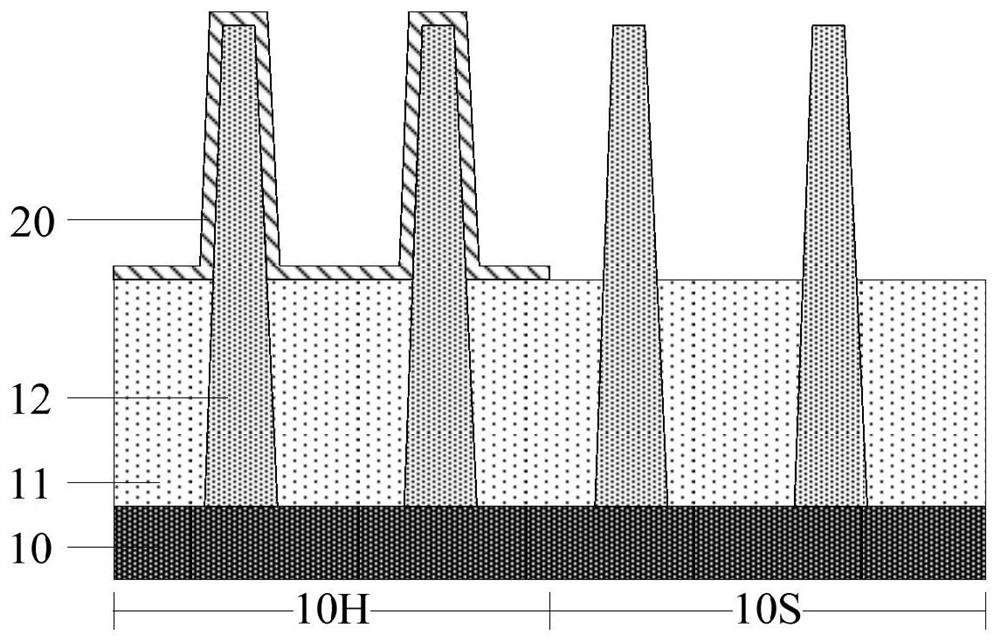

[0036] refer to Figure 1 to Figure 4 , a schematic diagram of the structure corresponding to each step in a method for forming a semiconductor structure is shown.

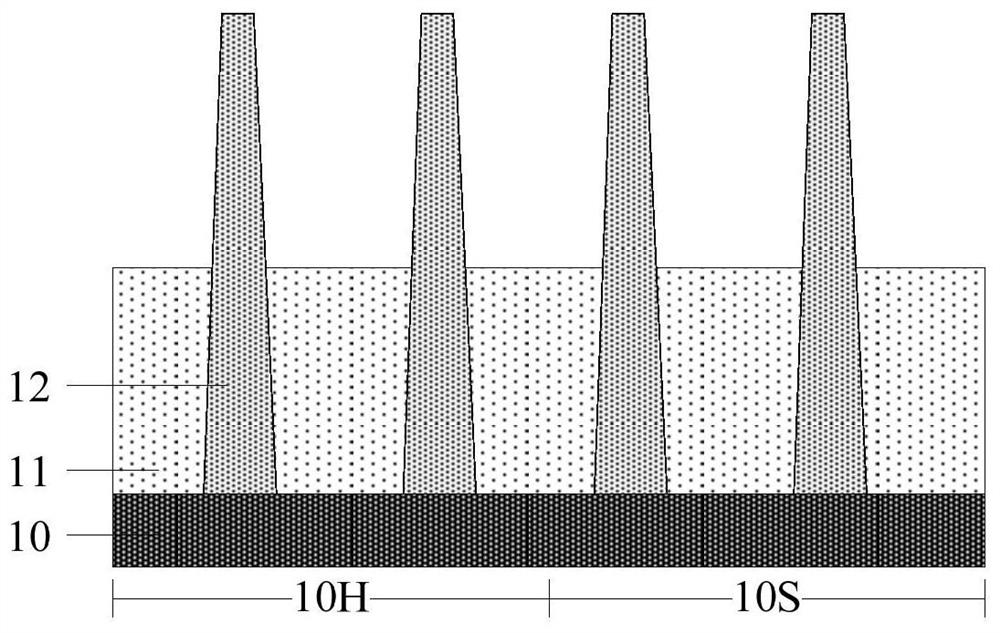

[0037] refer to figure 1 , providing a base, including a substrate 10 and a fin portion 12 protruding from the substrate 10 , an isolation layer 11 is formed on the substrate 10 exposed by the fin portion 12 , and the isolation layer 11 covers the fin portion 12 part of the sidewall, the substrate includes a first region 10H for forming a first device and a second region 10S for forming a second device, wherein the operating voltage of the first device is greater than that of the second device Operating Voltage.

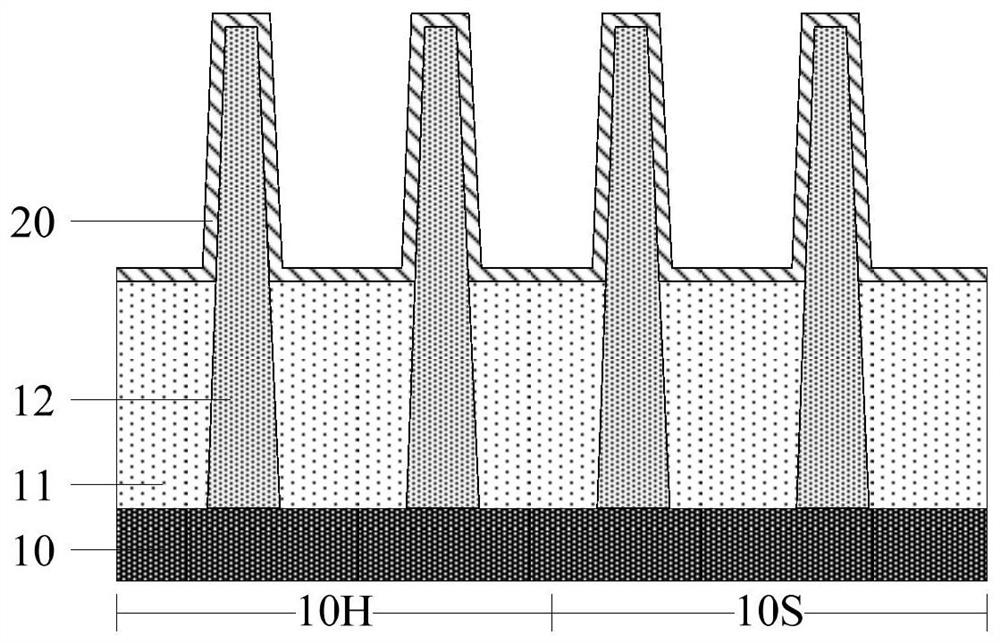

[0038] refer to figure 2 , forming a second gate oxide layer 20 conforma...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More