Planar salient point type technique for packaging intergrate circuit or discrete component

A planar bump-type, discrete component technology, used in electrical components, circuits, electrical solid devices, etc., can solve the problems of poor sole coplanarity, ability to affect solderability, poor contact, etc., and achieve electrical transmission rate. Fast, product quality assurance, the effect of improving heat dissipation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0052] The integrated circuit or discrete component planar bump type packaging process of the present invention consists of the following procedures:

[0053] 1) Substrate - see figure 1 , take a piece of metal substrate 1 with an appropriate thickness. The material of the metal substrate 1 can be changed according to the functions and characteristics of the chip, for example: nickel-iron alloy, pure copper or copper alloy.

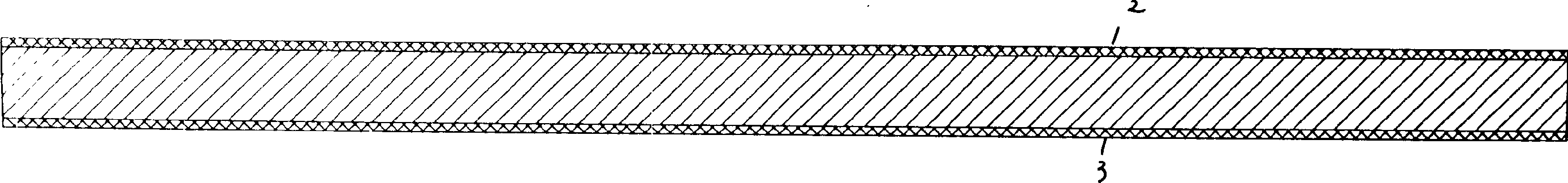

[0054]2) Applied dry film - see figure 2 , affix dry film layers 2 and 3 on both sides of the metal substrate to protect the subsequent etching process.

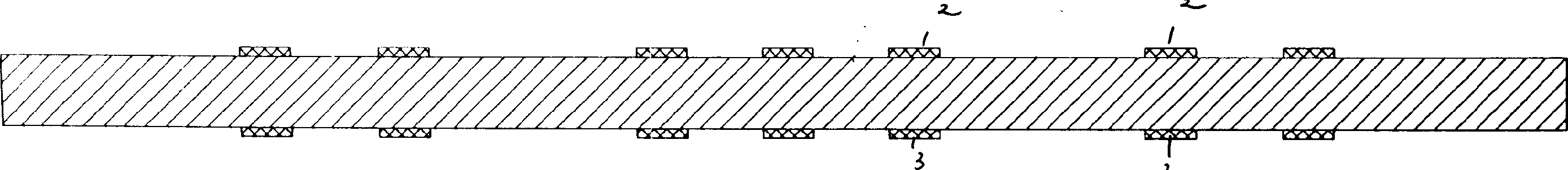

[0055] 3) Remove part of the dry film - see image 3 , correspondingly remove part of the dry film on both sides of the metal substrate 1, and prepare to form base islands and pins on the metal substrate 1, in order to expose the area on the upper layer of the substrate that needs to be metallized later.

[0056] 4) Metallized layer - see Figure 4 , plate the required metal layers 4.1, 4.2, 5.1,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More