Circuit board, method for manufacturing the same, semiconductor device, and method for manufacturing the same

A technology for circuit substrates and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., and can solve the problem of reduced semiconductor device yield and connection reliability, and the reduction of the gap between semiconductor chips and circuit substrates , reduced joint height, etc., to achieve high yield, easy contact, and increased clearance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

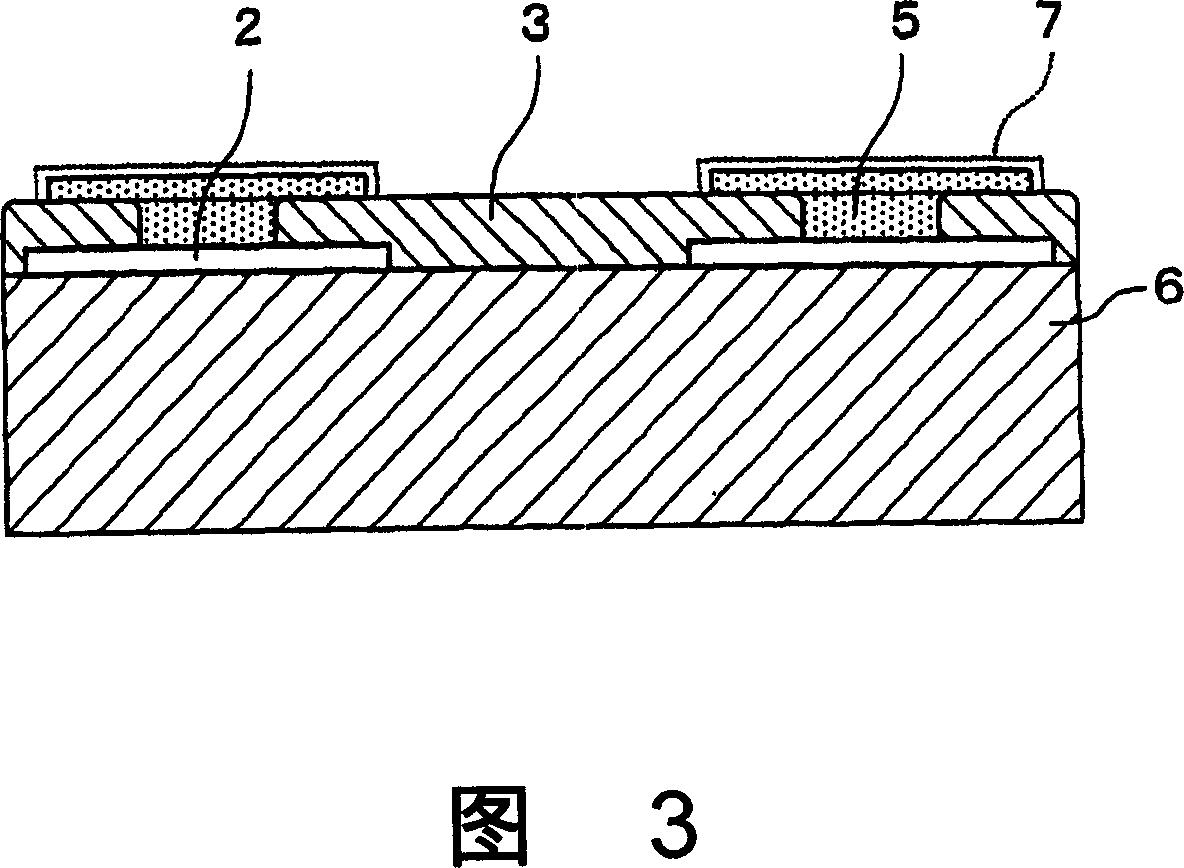

[0114] In Example 1, as the TEG (Test Element Group) for evaluation, a chip having a size of 10 mm x 10 mm, a thickness of 300 μm, electrodes formed with 900 pins, and a segmented array formed at 250 μm intervals was used. On the electrodes (pads) of the TEG for evaluation, Sn—Ag solder bumps with a radius of 55 μm were formed.

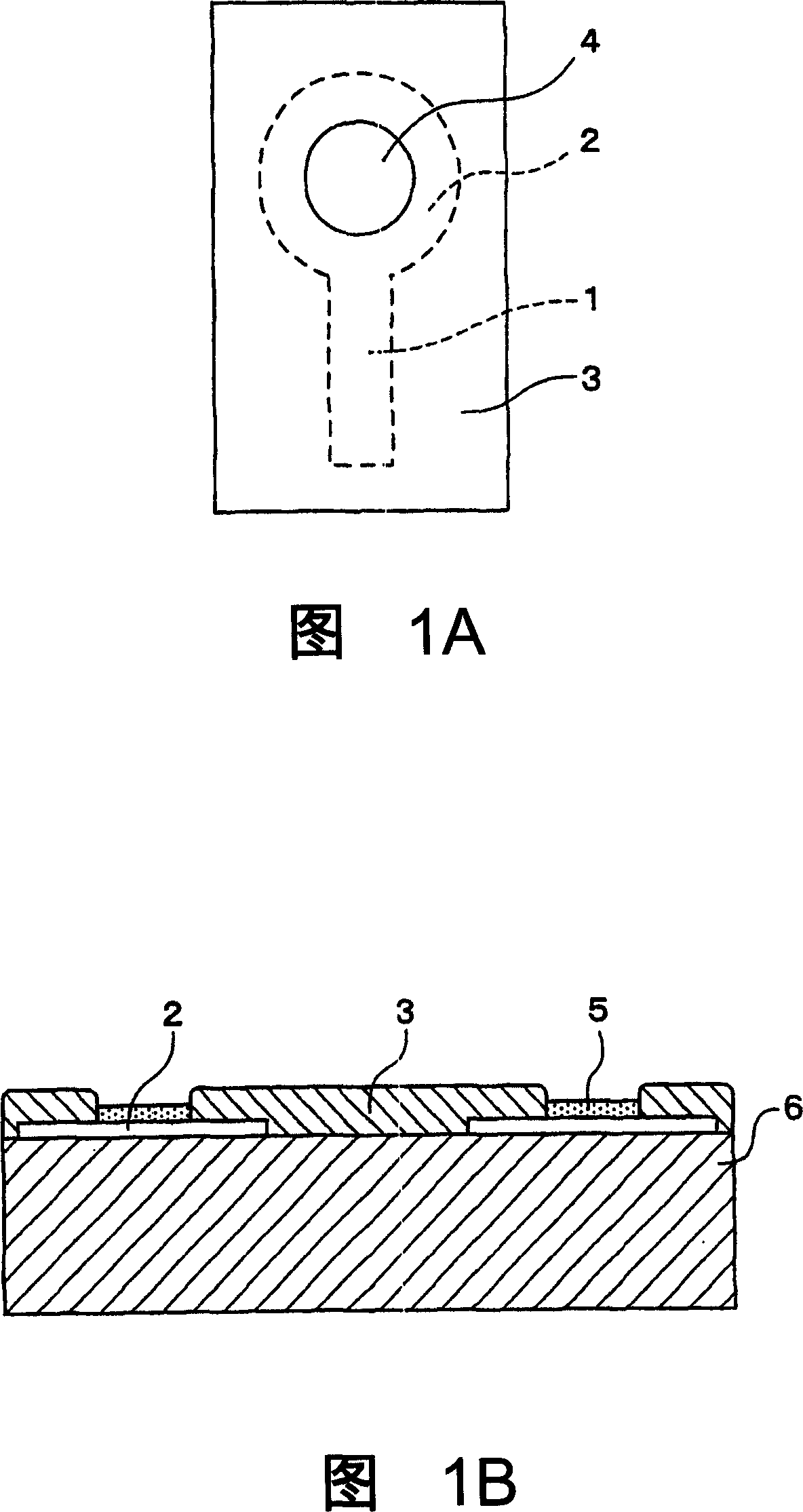

[0115] On the other hand, a general glass epoxy double-sided copper-clad board (manufactured by Hitachi Chemical Co., Ltd.: product name [MCL-E-67], thickness 1.6 mm) was prepared as a circuit board, and on the surface layer of the double-sided copper-clad board, use The pattern of wiring (wiring patterns and pattern wiring) and connection pads (main electrodes) is formed with a pitch of 250 μm and a diameter of 200 μm by photolithography. Here, in order to be able to evaluate bonding properties when semiconductors are mounted, the patterns of wiring and connection pads are configured so that electrodes on the TEG side for evaluation and electrodes on...

Embodiment 2

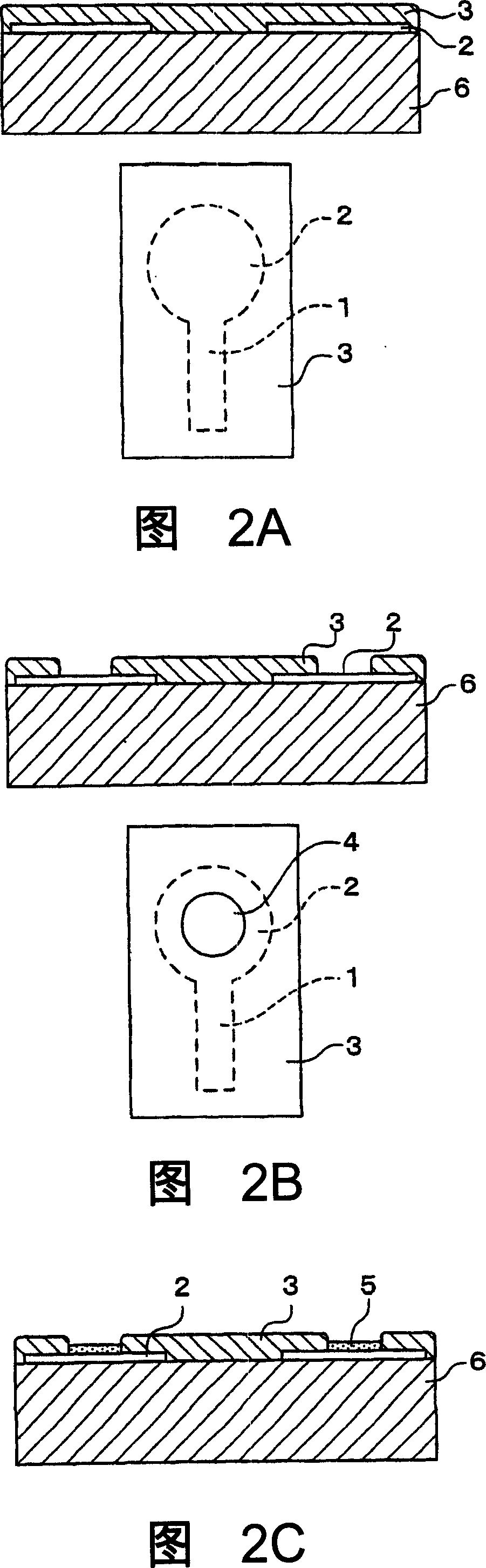

[0130] In this embodiment 2, as the semiconductor chip, the same chip as that in embodiment 1 is used. The same circuit board and solder resist as in Example 1 were also used. In addition, the same four conditions as in Example 1 of 40, 60, 80, and 100 μmφ were used for the diameter of the solder resist opening.

[0131] In Example 2, after the solder resist opening was formed, a printing mask having an opening with a diameter of 200 μmφ larger than the opening was placed on the solder resist, and the silver paste was filled by printing through the screen mask ( Manufactured by Vacuum Metallurgical Co., Ltd. (currently Albac Material Co., Ltd.: product name [nanope st]), and fired at 230° C. for 1 hour to produce a circuit board for flip-chip mounting. Next, a semiconductor chip (TEG for evaluation) was mounted in the same manner as in Example 1, and a flip-chip semiconductor device was obtained through a solvent cleaning step and a filler injection step.

[0132] As in Exam...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More