Semiconductor flip-chip package and method for the fabrication thereof

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

example 1

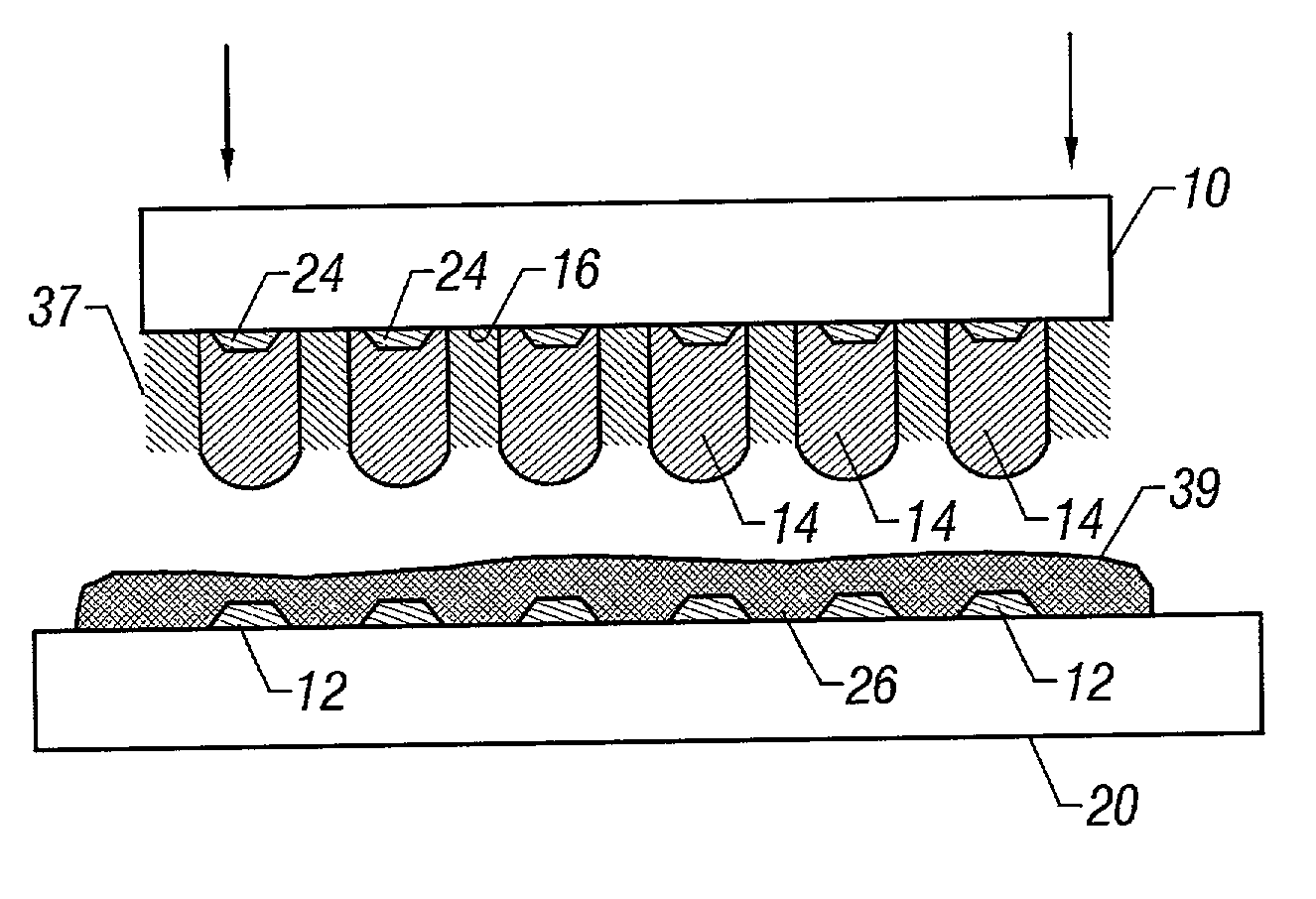

(Preparation of Encapsulant that is suitable for use as the Second Portion Encapsulant 39 in FIG. 16)

[0094] The entitled encapsulant, comprising a polymer flux, was prepared from a mixture that contained:

[0095] 1. 25 grams bisphenol A glycerolate di(2-octen-1-ylsuccinic) acid monoester;

[0096] 2. 12.5 grams of bisphenol A epoxy; and

[0097] 3. 4 grams of glycidyl 4-nonylphenyl ether.

[0098] This composition was mixed and cured for 4 hours at 165.degree. C. It produced a solid having a thermal coefficient of expansion of about 180 ppm / .degree. C.

example 2

(Preparation of Two-Portion Liquid Underfill Encapsulants Applied Before Assembly)

[0099] A set of ten flip chip assemblies was fabricated. Specifically, a bumped semiconductor chip, part FBT-250 available from Flip Chip Technologies, Phoenix, Ariz., was coated with a first portion liquid encapsulant 111 as shown FIG. 10. The first portion of the encapsulant consisted of a liquid layer, approximately 50 to 75 microns thick, that covered the underside of the chip and the solder bumps completely. It was formed from a mixture that contained:

[0100] 1. Bisphenol A epoxy 15 weight %;

[0101] 2. Glycidyl 4-nonylphenyl ether 6 weight %;

[0102] 3. Pentaeryethritol triacrylate 18 weight %

[0103] 4. Tert-butyl peroxide 0.06 weight %;

[0104] 5. Glass spheres 40 weight % (Aldrich catalog No. 44,034-5); and

[0105] 6. Bisphenol A glycerolate di(2-octen-1-ylsuccinic) acid monoester 20.94 weight %.

[0106] The composition was mixed and cured for 4 hours at 165.degree. C. It produced a solid having a thermal ...

example 3

(Preparation of Encapsulant that is Suitable for use as the first Portion Encapsulant 37 in FIG. 16)

[0110] 2-allyl phenyl glycidyl ether was synthesized by heating 2-allyl phenol (AP) and 10 times excess molar ratio epichlorohydrin (EPH) to 115.degree. C. under nitrogen in the presence of aqueous sodium hydroxide (NaOH). During the reaction, water which must be removed is formed by the reaction between 2-AP and EPH. Since water and EPH form an azeotrope, water was removed from the reaction by azeotropic distillation, which to drives the reaction forward. Collected EPH was returned as needed to the mixture to prevent undesirable side reactions. After 4 hours, the resultant salts were separated from the product. The product was then purified by extraction of the oil phase with toluene, followed by removing the excess EPH and aqueous phase with toluene, which was also used as an azeotropic agent. The product obtained was a thin, yellowish, transparent liquid. Yield was about 90%. Disti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More