N-channel metal oxide semiconductor (NMOS) driver circuit and method of making same

a driver circuit and metal oxide semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., can solve the problems of substantially worse short-channel effect, channel pfet, or nfet, and is generally more expensive than a single-work function-gate process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

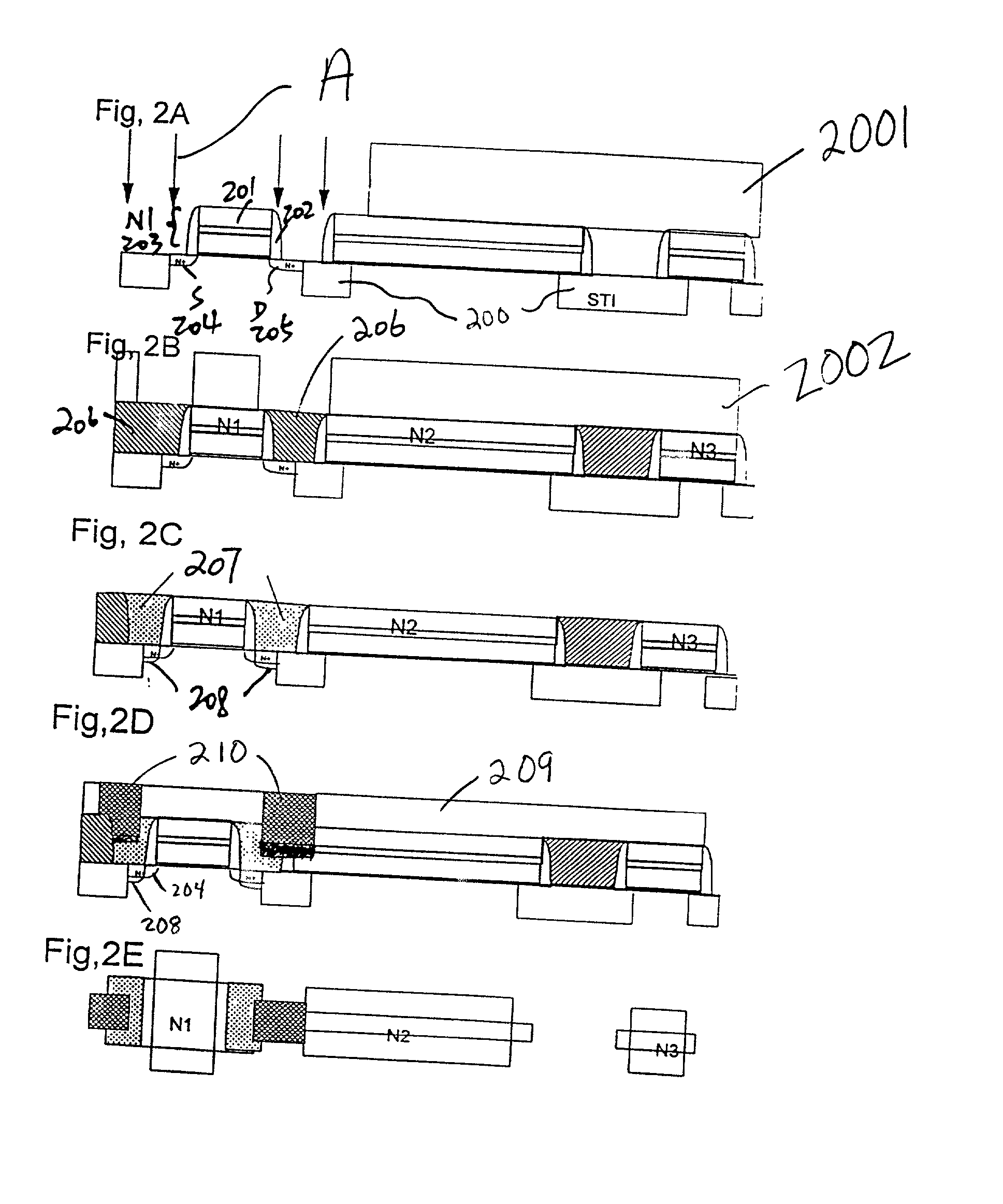

[0038] Referring now to the drawings, and more particularly to FIGS. 2A-5, an embodiment of the present invention will be described.

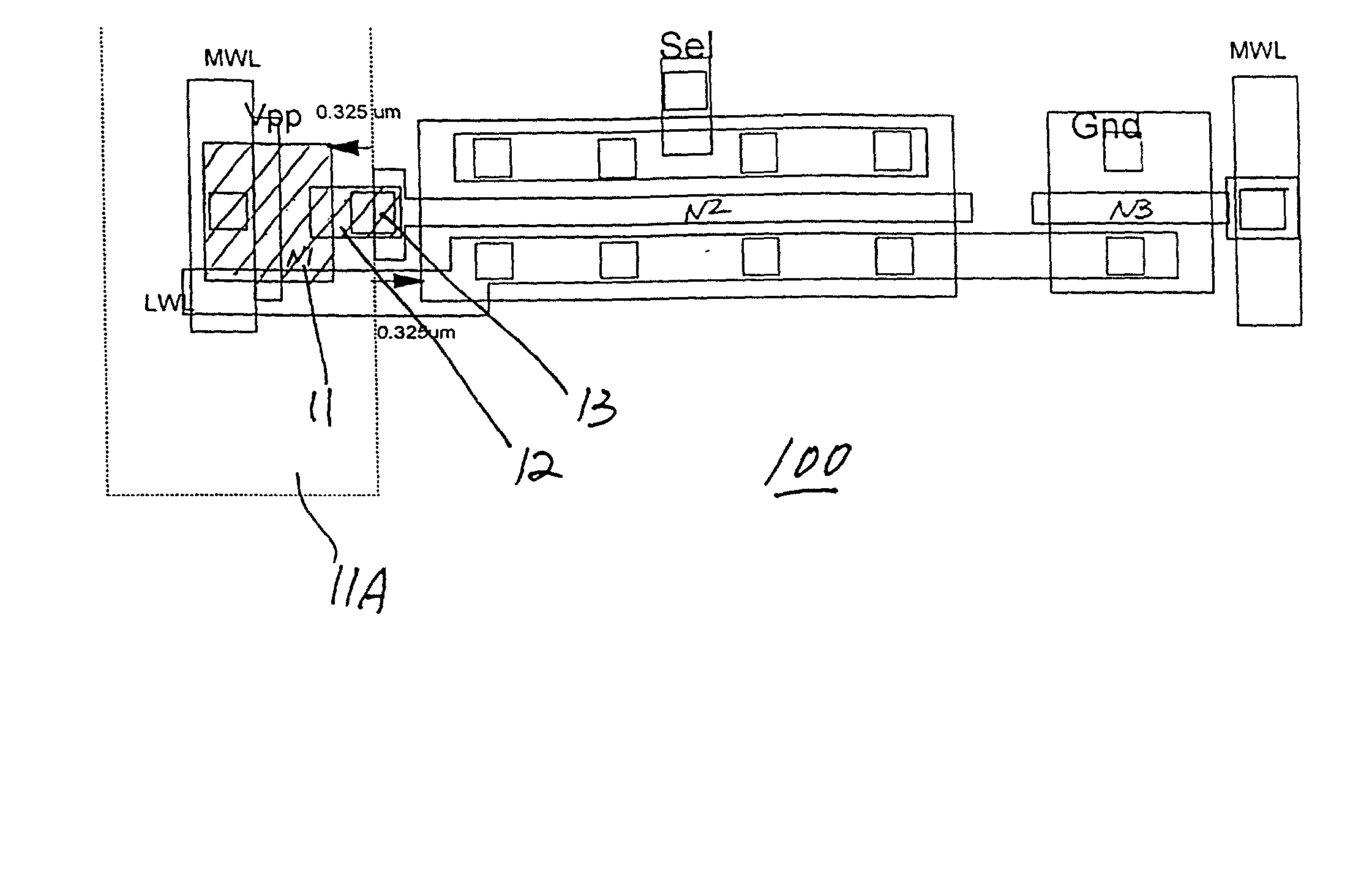

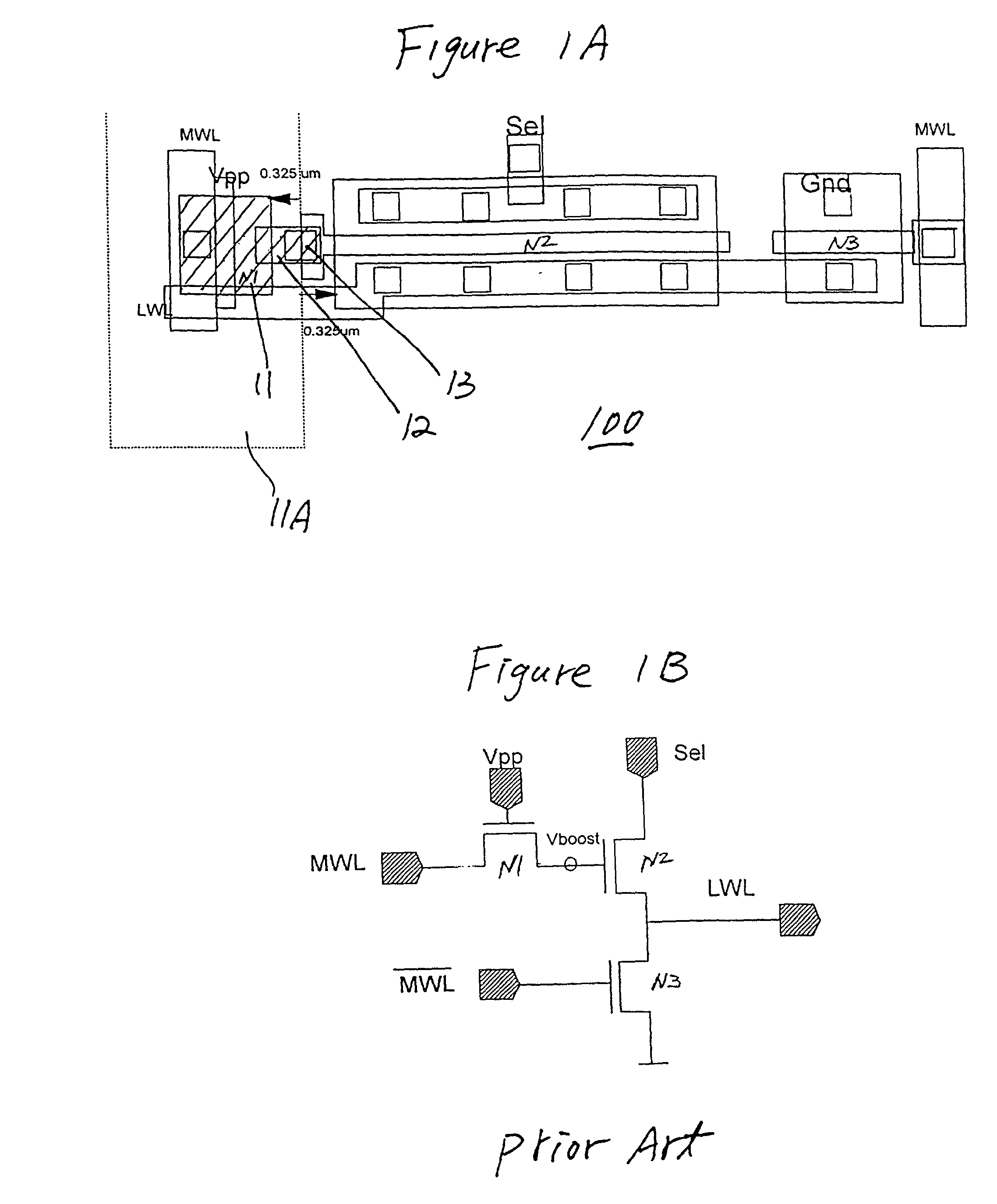

[0039] In FIG. 1A, a top view of an NMOS driver circuit 100 is shown. The shape of a contact bitline (CB) mask, or the cross-hatched area, for a boost device 11 (e.g., N1) is shown in FIG. 1A. The CB mask is for forming contacts and for driving in more dopant.

[0040] As a result, the boost device 11 will have XA implant, or a lower concentration N-type array implant, 11A and its serial resistance is reduced by the self-aligned CB diffusion. Arranging the device 11 close to the array allows it to be implanted by XA mask without increasing the support area, and thereby increases the density.

[0041] Through a CB extension 12, the CB contact 12 is formed in a self-aligned manner which abuts the gate of the pull-up NMOS device N2, as shown in FIG. 1A. The connection (e.g., joint) of the boost node to the gate is performed by a contact support (CS) 13, as shown...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More