Fabrication method of semiconductor integrated circuit device

a technology of integrated circuit devices and manufacturing methods, which is applied in the direction of individual semiconductor device testing, semiconductor/solid-state device testing/measurement, instruments, etc., can solve the problems of difficult to locate probes, not only breaking the natural oxide film formed over the surface of each test pad, but also forming a dent on the surface of the test pad, so as to reduce the damage of the test pad and shorten the electrical testing step

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

embodiment 1

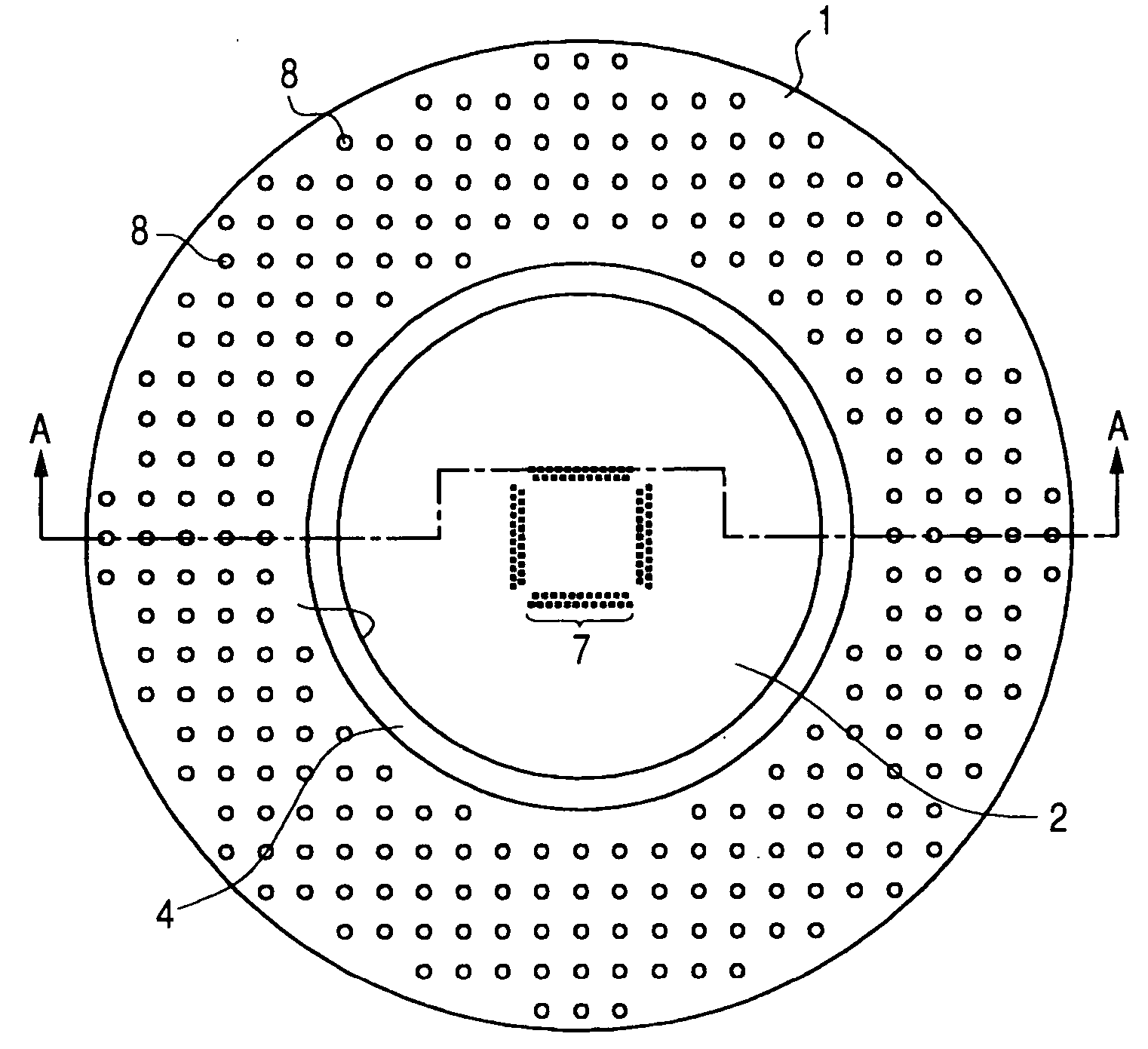

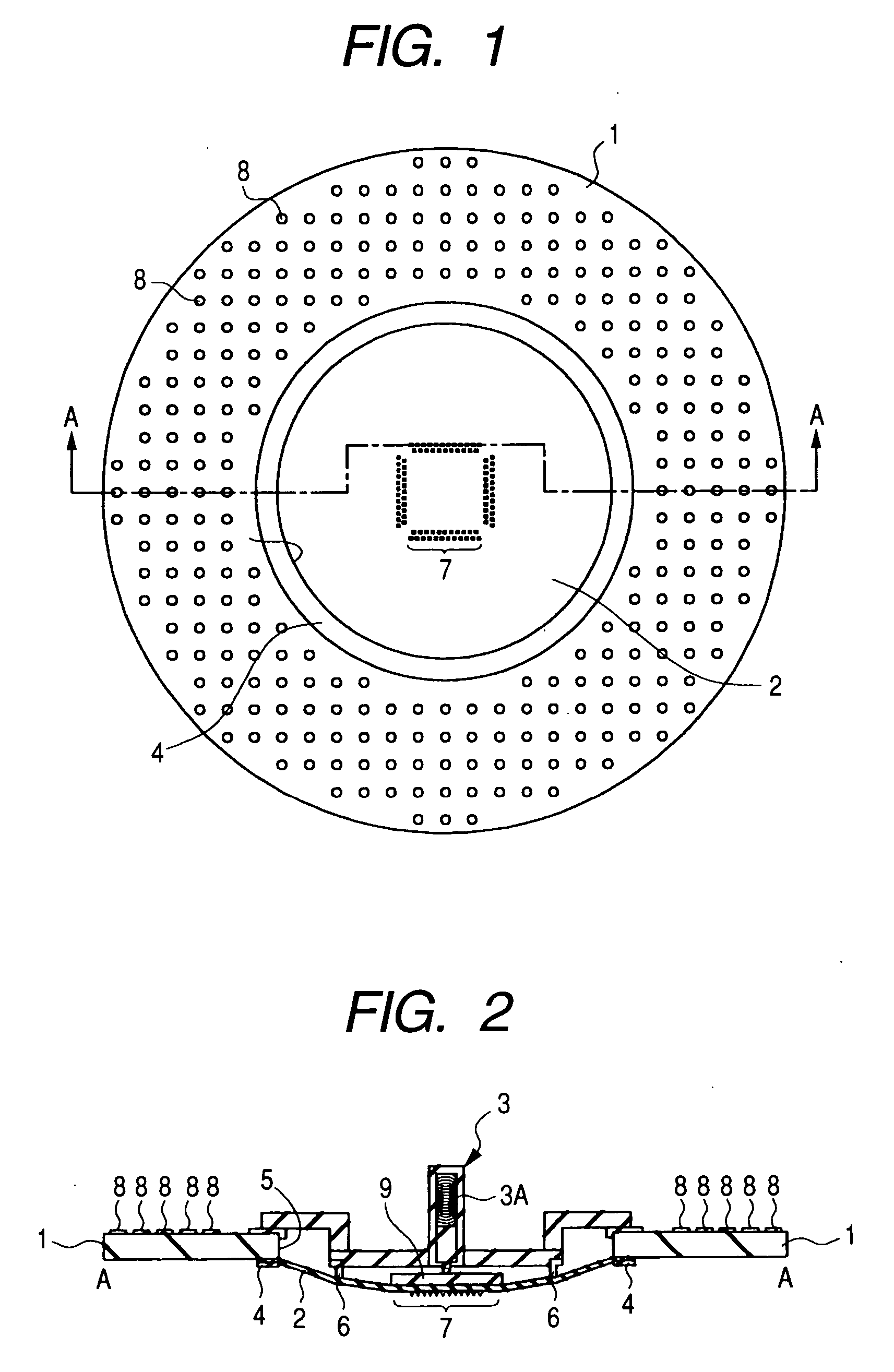

[0282]FIG. 1 is a fragmentary plan view of the lower surface of a probe card according to Embodiment 1, and FIG. 2 is a cross-sectional view taken along a line A-A of FIG. 1.

[0283] As illustrated in FIGS. 1 and 2, the probe card (first card) of Embodiment 1 is made of, for example, a multilayer wiring substrate 1, a thin film sheet (thin film probe (first sheet)) 2 and a plunger (pressing mechanism) 3. The thin film sheet 2 is fixed to the lower surface of the multilayer wiring substrate 1 by a presser ring 4, and the plunger 3 is attached to the upper surface of the multilayer wiring substrate 1. An opening portion 5 is located at the center of the multilayer wiring substrate 1, and, in this opening portion 5, the thin film sheet 2 and the plunger 3 are bonded via an adhesive ring 6.

[0284] Over the lower surface of the thin film sheet 2, a plurality of probes (contact terminals) 7, for example, having a pyramid form or trapezoidal pyramid form are provided. In the thin film sheet...

embodiment 2

[0315] A description will next be made of Embodiment 2.

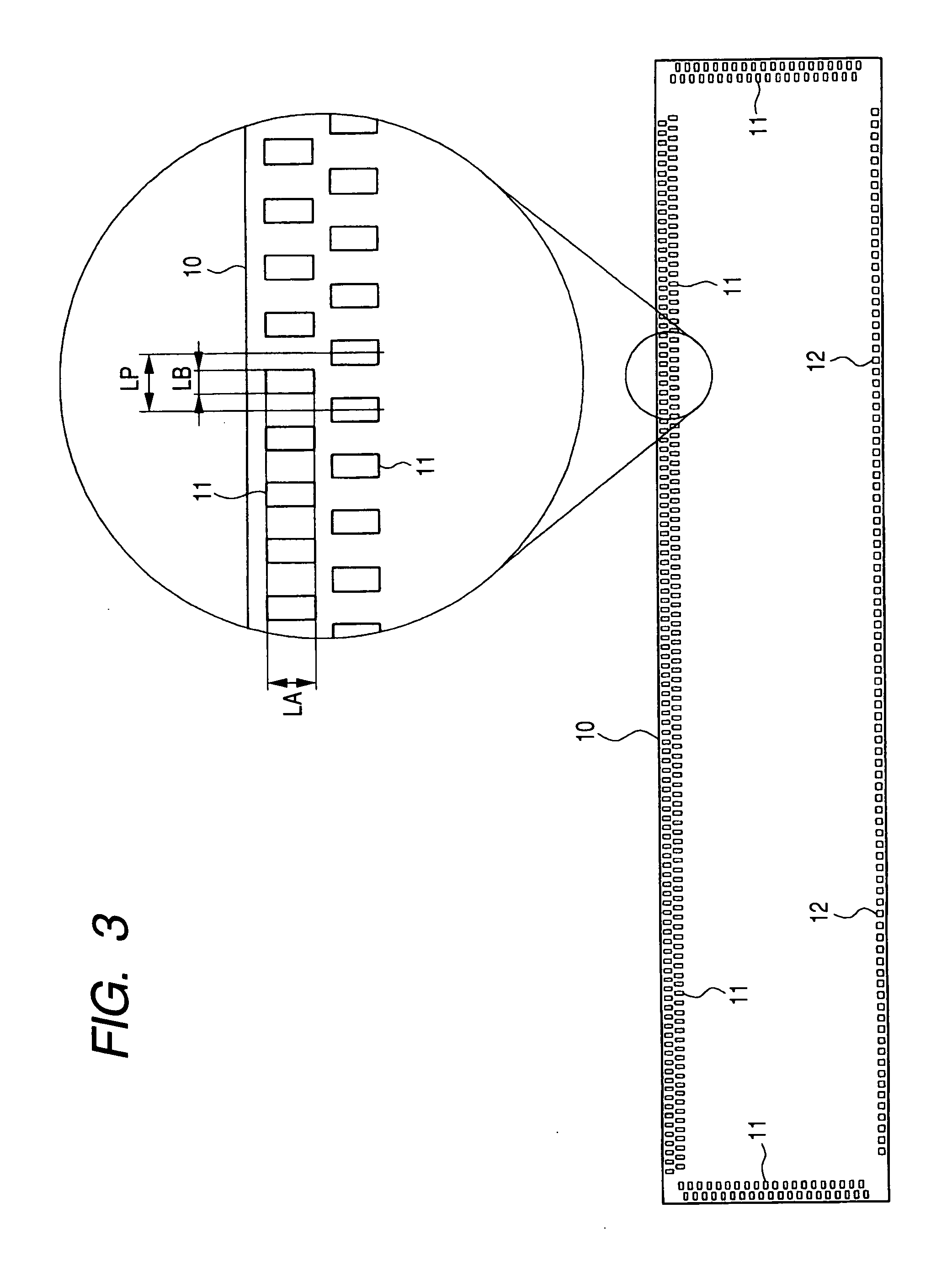

[0316] A relatively high current flows in some of the pads 11 and 12, which were described with reference to FIG. 3 in conjunction with Embodiment 1. When all of the probes 7A or 7B have the same size, an electrical load applied to the probe 7A or 7B to be brought into contact with the pad 11 or 12 through which a relatively high current flows increases. With an increase in the electrical load, the probe 7A or 7B which becomes hot may inevitably be welded with the pad 11 or 12 or the probe 7A or 7B may be broken. In Embodiment 2, as illustrated in FIG. 36, a plurality of probes (first contact terminals) 7B (or probes (first contact terminals) 7A) are disposed for the metal film 21B (or metal film 21A) which is opposite to the pad 11 or 12 through which a relatively high current flows, and the total contact area (first contact area) of the probes 7B (or probes 7A) and the pad 11 or 12 through which a relatively high current flow...

embodiment 3

[0319] A description will next be made of Embodiment 3.

[0320] When the probes 7A or 7B (refer to FIGS. 6 to 8) as described in conjunction with in Embodiments 1 and 2 are brought into contact with the pad 11 or 12 (refer to FIG. 3), a force is applied to a flat portion of the tip portion of the probe 7A or 7B. When a great force is applied to the probe 7A or 7B and the area of this flat portion is small, the metal film 21A or 21B including the probe 7A or 7B may be embedded inevitably into the polyimide films 22 and 25 (refer to FIGS. 6 to 8). Also, when the load applied to the probe 7A or 7B is excessively large, crushing or wearing of the probes 7A and 7B themselves may occur. In Embodiment 3, therefore, the area of the flat portion of the tip portion of the probe 7A or 7B is widened within an extent not causing such inconveniences. This makes it possible to prevent the breakage of the probes 7A and 7B.

[0321] In Embodiment 3, not only the area of the flat portion of the tip port...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More