Process for implementing oxygen into a silicon wafer having a region which is free of agglomerated intrinsic point defects

a technology of intrinsic point defects and oxygen, which is applied in the direction of crystal growth process, testing/measurement of semiconductor/solid-state devices, transportation and packaging, etc., can solve the problems of agglomeration of intrinsic point defects, affecting the yield potential of materials, and the number of defects in single crystal silicon form, etc., to achieve the effect of improving the gettering capability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

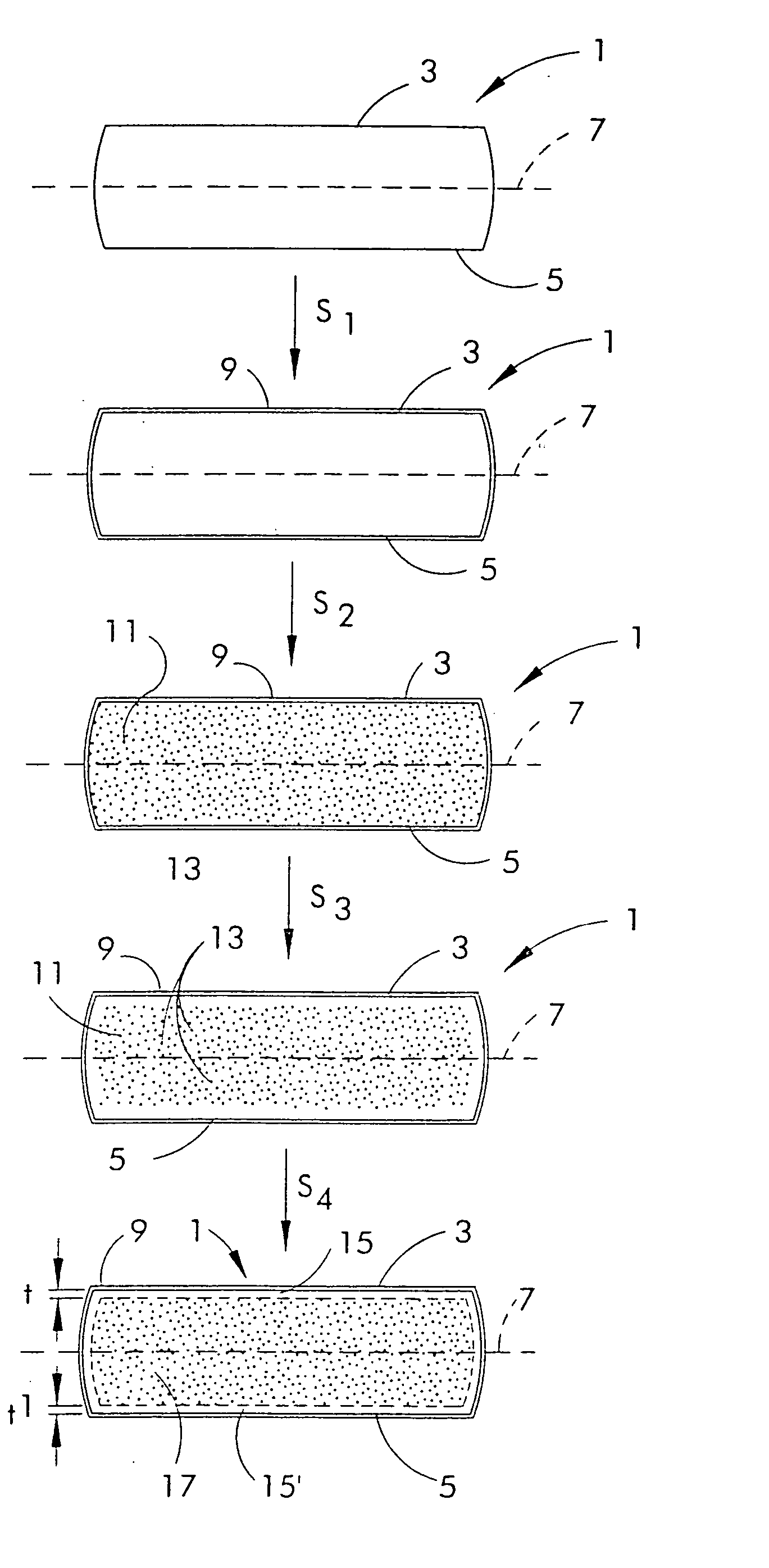

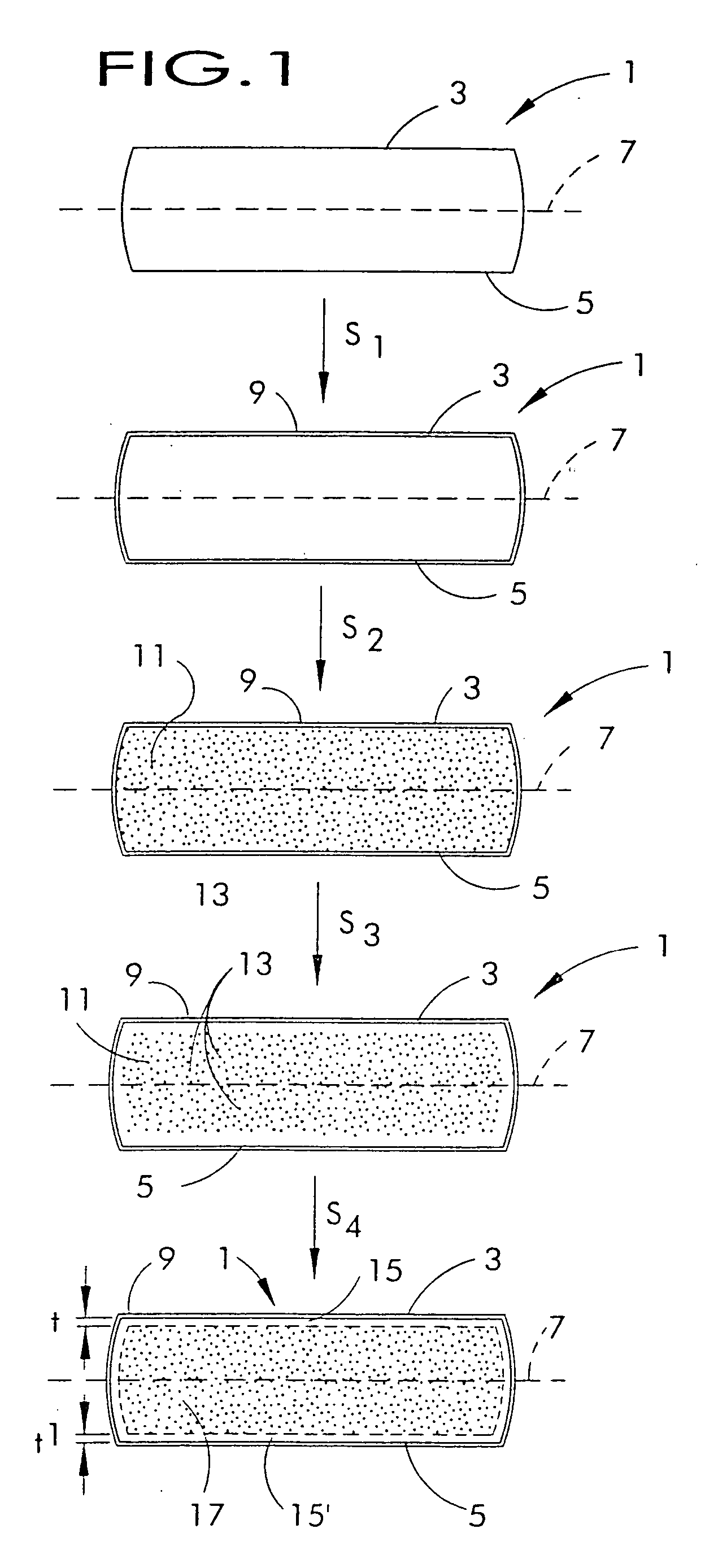

example 1

[0133] Silicon single crystals were pulled by the Czochralski method, sliced and polished to form silicon wafers. These wafers were then subjected to a surface oxidation step (S1), rapid thermal annealing step in nitrogen or argon (S2), rapidly cooled (S3), and subjected to an oxygen stabilization and growth step (S4) under the conditions set forth in Table I. The initial oxygen concentration of the wafers (Oi) before steps S1-S4, the oxygen precipitate density in the bulk of the wafers after step S4 (OPD), and the depth of the denuded zone after step S4 (DZ) are also reported in Table I.

TABLE ISample4-74-83-14S115 min at15 min atnone1,000° C.1,000° C.in N2 + ˜1%in N2 + ˜1%O2O2S235 seconds35 seconds35 secondsat 1250° C.at 1250° C.at 1250° C.in N2in Arin N2S3100° C. / sec100° C. / sec100° C. / secS44 hr at4 hr at4 hr at800° C. + 16 hr800° C. + 16 hr800° C. + 16 hratatat1,000° C.1,000° C.1,000° C.in N2in N2in N2Oi7 × 10176.67 × 1017 7.2 × 1017(atoms / cm3)OPD1 × 1010 4.4 × 1091.69 × 1010(at...

example 2

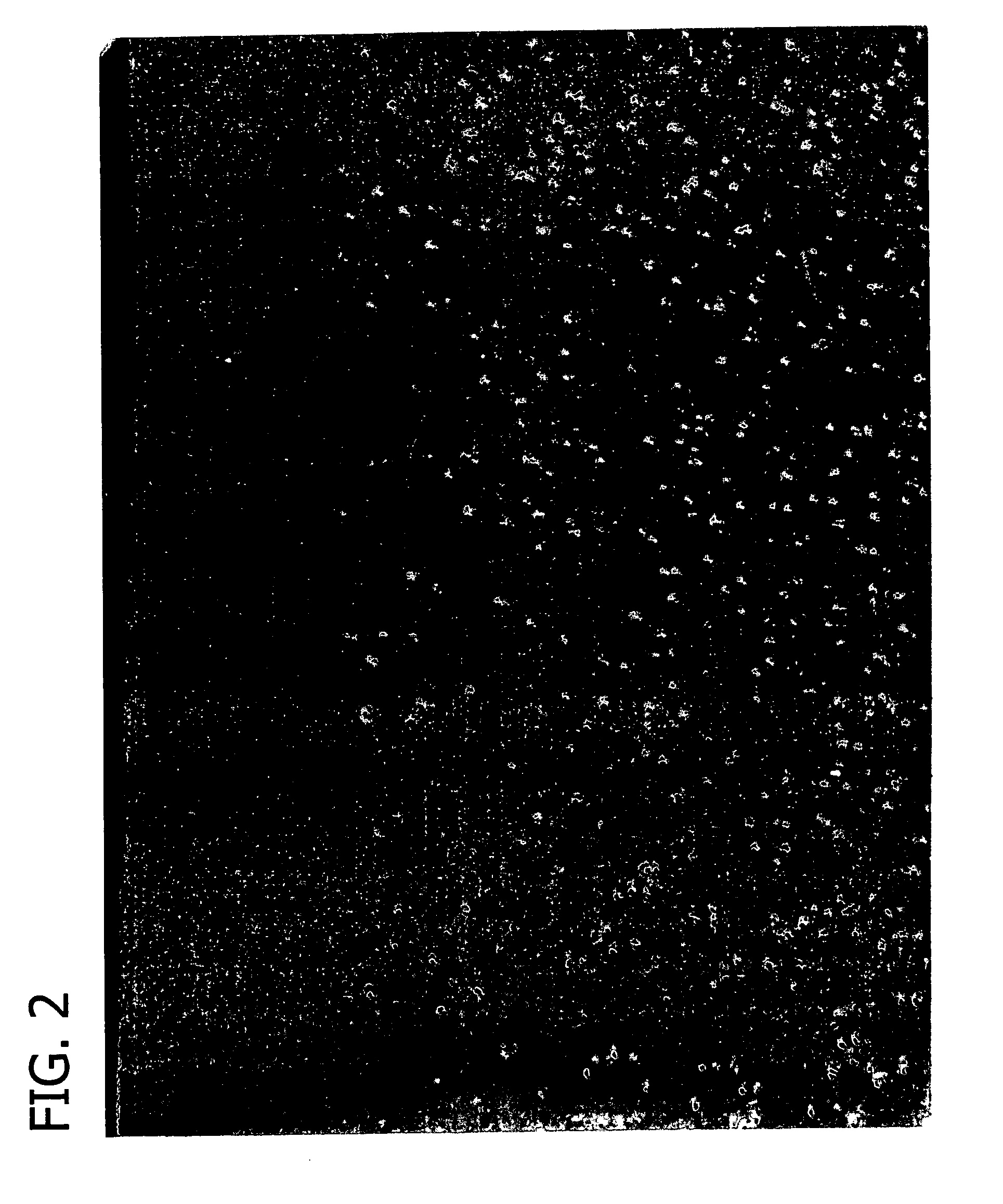

[0136] To demonstrate that the process of the present invention is relatively independent of oxygen concentration for Czochralski-grown silicon wafers, three wafers having different oxygen concentrations were subjected to the same series of steps described in Example 1. The conditions for each of these steps, the initial oxygen concentration of the wafers (Oi) before steps S1-S4, the oxygen precipitate density (OPD) in the bulk of the wafers after step S4, and the depth of the denuded zone (DZ) after step S4 as measured from the surface of the wafer are reported in Table II. FIGS. 6, 7, and 8 show cross-sections of the resulting wafers (these figures are enlargements of photographs taken at a magnification of 200×); sample 3-4 is shown in FIG. 6, sample 3-5 is shown in FIG. 7, and sample 3-6 is shown in FIG. 8.

TABLE IISample3-43-53-6S115 min at15 min at15 min at1,000° C.1,000° C.1,000° C.in N2 + ˜1%in N2 + ˜1%in N2 + ˜1%O2O2O2S235 seconds35 seconds35 secondsat 1250° C.at 1250° C.a...

example 3

[0137] To demonstrate that the process of the present invention was relatively independent of the conditions used for the oxygen precipitate stabilization and growth step (S4), a wafer (sample 1-8) having the same initial oxygen concentration was subjected to the same series of steps described in Example 2 for sample 3-4 except that a proprietary, commercial 16 Mb DRAM process was used as the oxygen precipitate stabilization and growth step (S4). FIG. 9 shows a cross-section of the resulting wafer (this figure is an enlargement of a photograph taken at a magnification of 200×). After step S4, samples 1-8 and 3-4 had comparable bulk oxygen precipitate densities (7×1010 / cm3 for sample 1-8 versus 4×1010 / cm3 for sample 3-4) and comparable denuded zone depths (approximately 40 micrometers).

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

| temperature | aaaaa | aaaaa |

| thick | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More