Method for making high performance semiconductor memory devices

a memory device and high-performance technology, applied in information storage, static storage, digital storage, etc., can solve the problems of inability to operate at optimum speed, inability to achieve optimum speed, and large performance gap, so as to improve the performance of semiconductor memory devices, reduce noise sensitivity of memory devices, and improve the effect of semiconductor memory devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

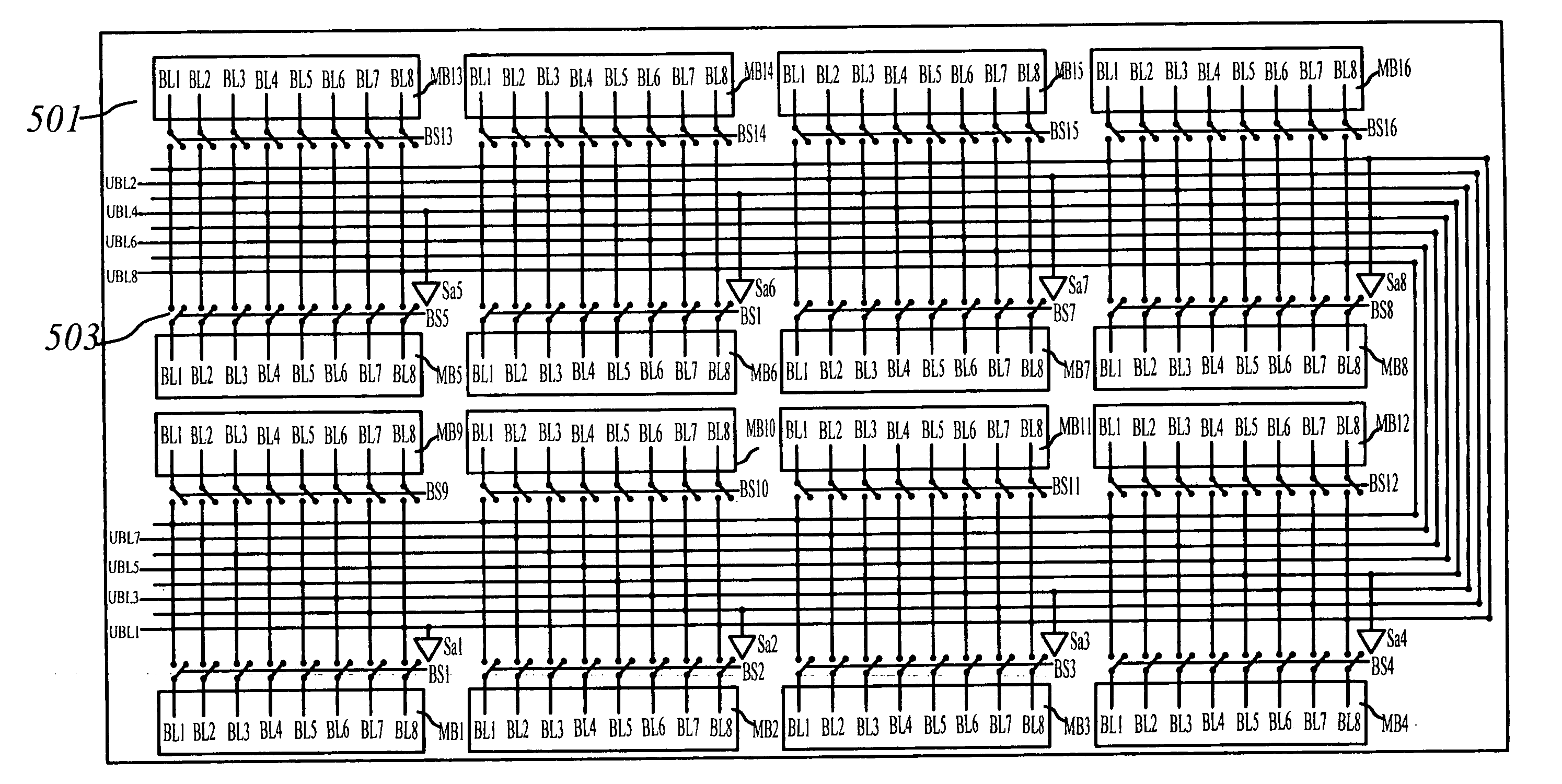

[0050] Referring to the simplified symbolic diagram shown in FIG. 4 for the basic concept of the present invention. A memory device is arranged in multiple levels. At the top-level (403), the memory device appears to be a small array with small number of top level cells (413) on each side. Each top-level cell (413) also appears to be a small second level array (402) with a small number of second level cells (412). We can have many levels. Eventually, we will reach the bottom level (401) that is actually a small memory array with a small number of real memory cells (411). For example, a 1 G (billion)-bit memory array is configured into three levels.

[0051] The top level is formed as a “virtual” 32×32 array, the second level is formed as another “virtual” 32×32 array, while the bottom level is a real 32×32 memory array.

[0052] To access a set of data in the memory, the memory address is separated into three sub-sets to the decoders in three levels and decoded simultaneously. One botto...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More