Method for mounting semiconductor device, as well as circuit board, electrooptic device, and electronic device

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

[0046] First Embodiment

[0047] The first embodiment of the present invention will now be described in detail referring to the accompanying drawings. In addition, in each of the drawings used in the following description, the scale of each layer, member, or the like is changed as a matter of convenience to show such layer, member, or the like in recognizable sizes.

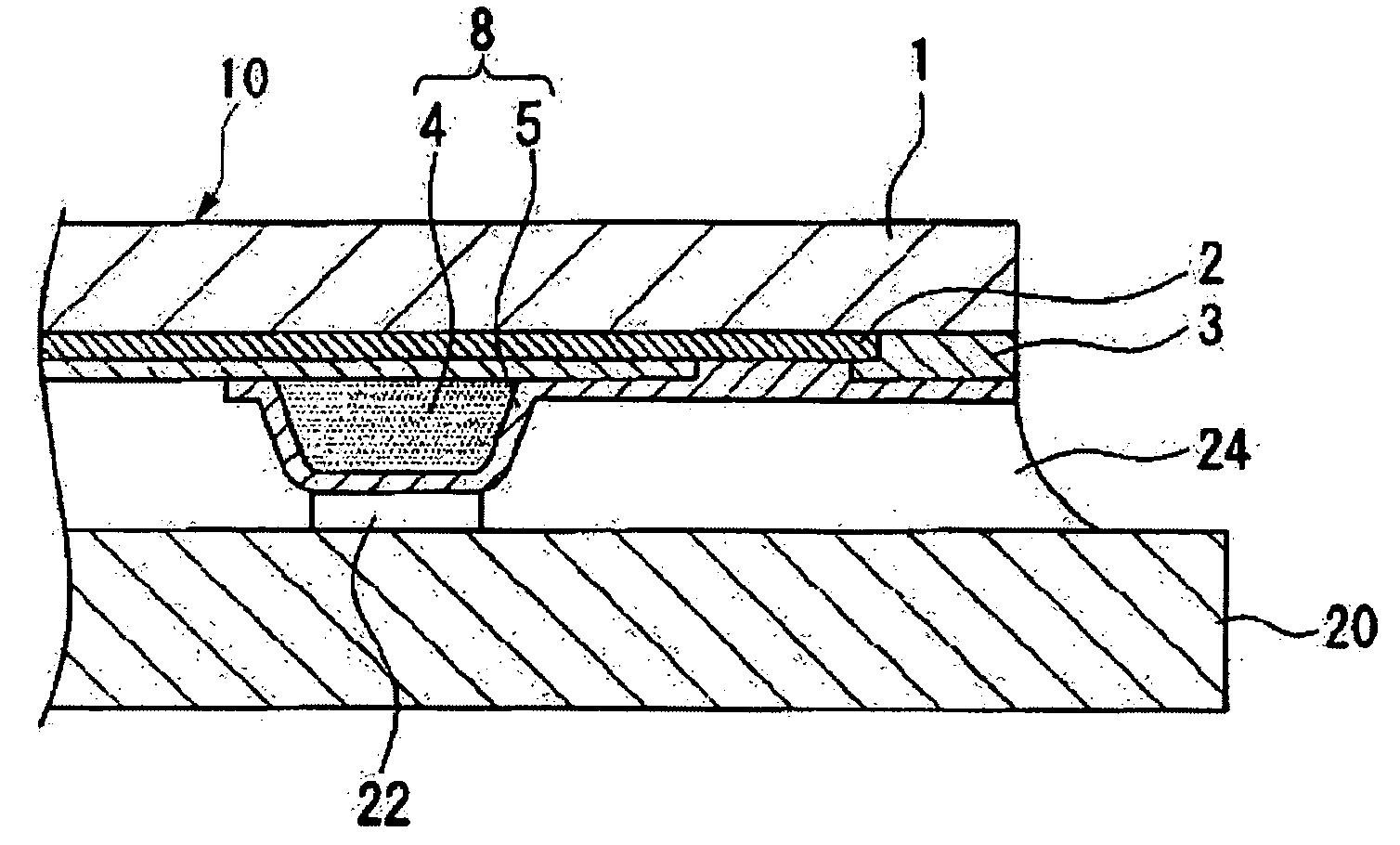

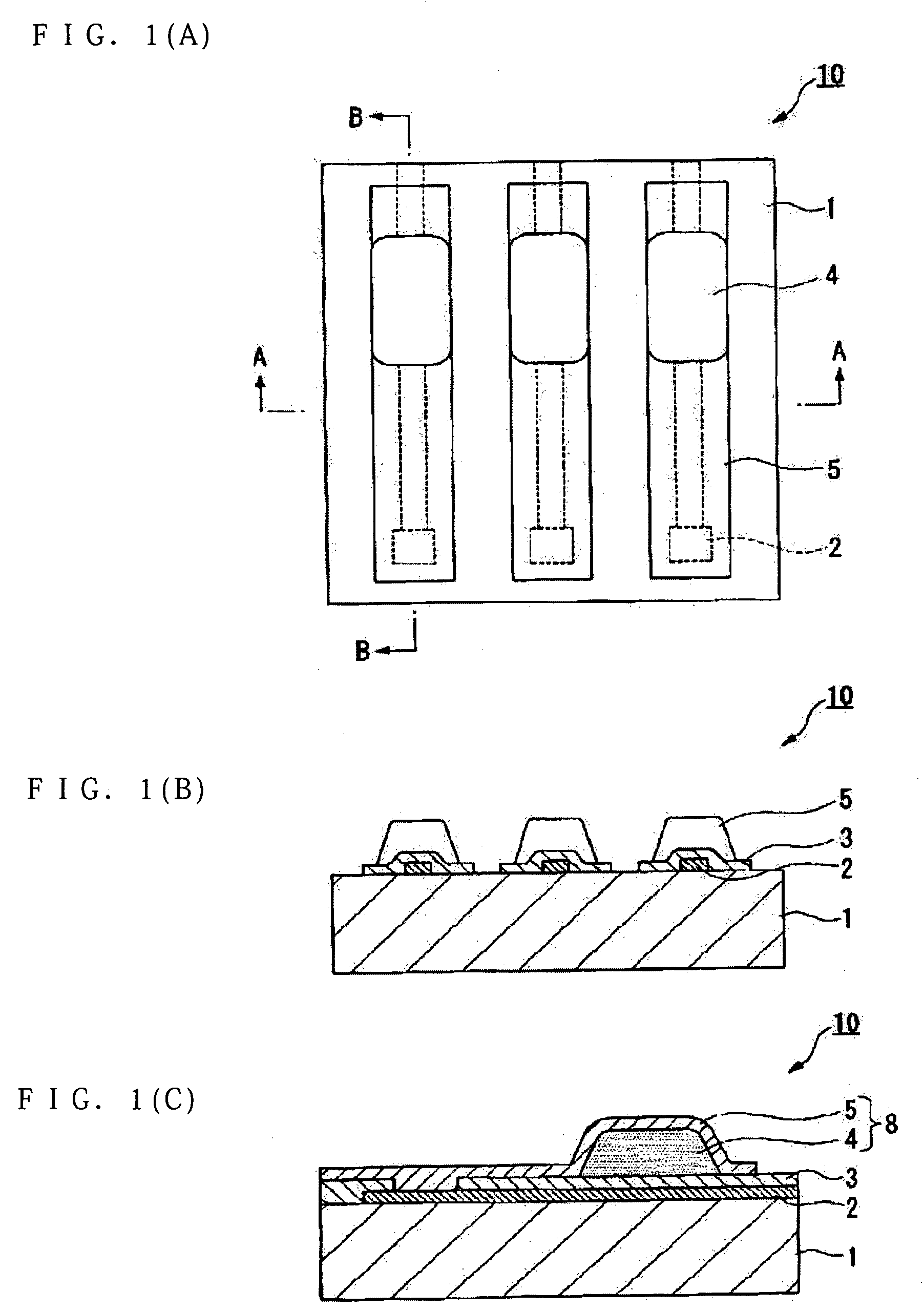

[0048] Semiconductor device

[0049]FIG. 1A is a partial enlarged top view of a substrate on which a semiconductor element is formed, showing a semiconductor device according to the present invention. FIG. 1B is a cross-sectional view along line A-A in FIG. 1A. FIG. 1C is another cross-sectional view along line B-B in FIG. 1A. In addition, the substrate in the present embodiment can be either a semiconductor substrate such as a silicon wafer on which a number of semiconductor chips are formed or an independent semiconductor chip. Further, in the case of a semiconductor chip, the shape of the chip is not limited to a general r...

second embodiment

[0066] Second Embodiment

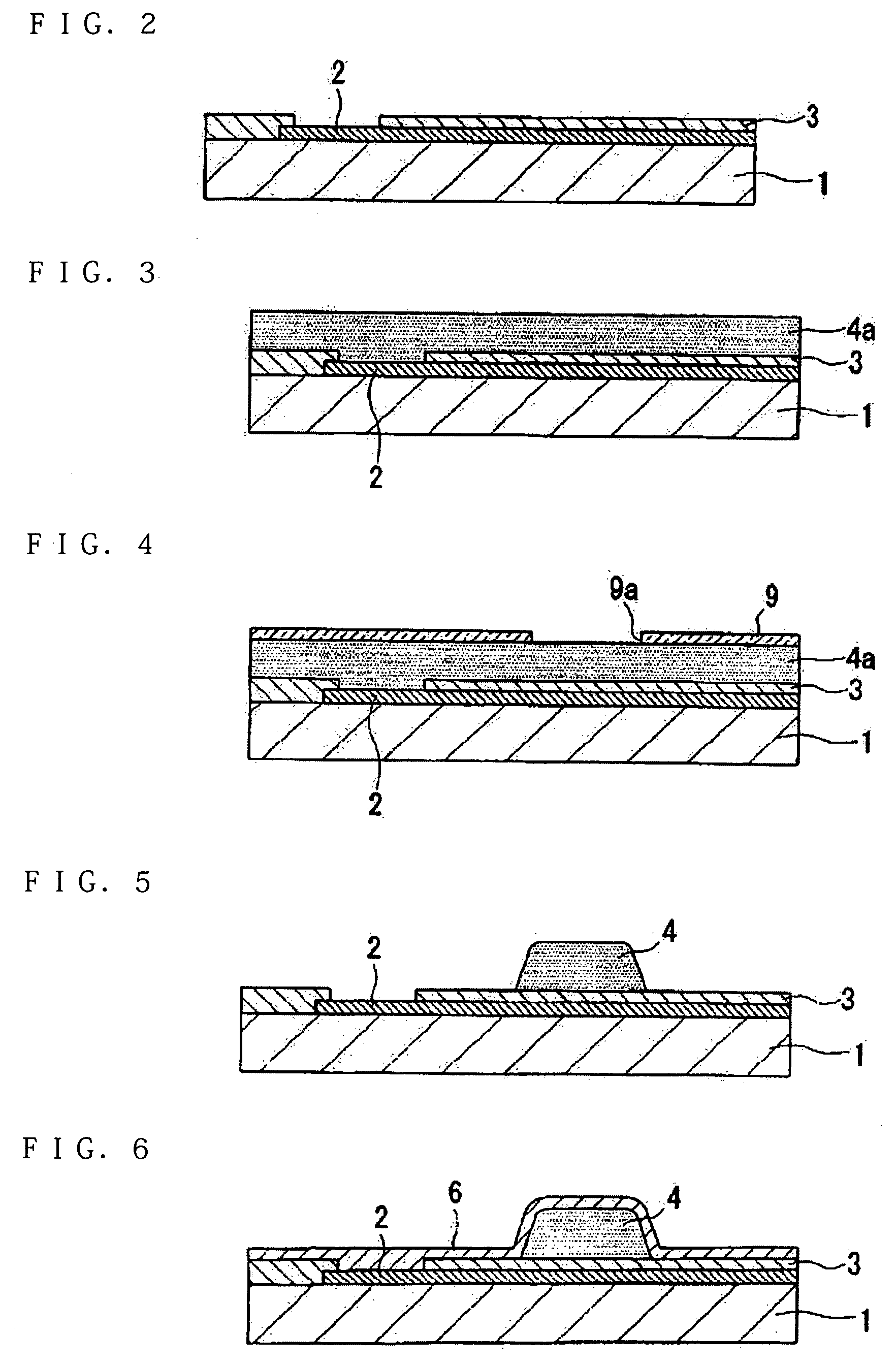

[0067] The second embodiment will now be described in detail referring to the accompanying drawings.

[0068] In the method for forming a semiconductor device according to the first embodiment, the conductive unit covering from the electrode 2 and spreading over the surface of the protrusion 4 is formed with a single layer of the first conductive layer 5. In contrast, the second embodiment provides a different method wherein the conductive unit covering from the electrode 2 and spreading over the surface of the protrusion 4 is formed with two layers including the first conductive layer 5 and the second conductive layer 7. In addition, the other details of the method for forming a semiconductor device are the same as those of the first embodiment. Therefore, the same reference numerals are used for the components common to both embodiments and detailed description is omitted.

[0069] First, employing the manufacturing steps shown in FIGS. 2 to 6 of the first embo...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Temperature | aaaaa | aaaaa |

| Temperature | aaaaa | aaaaa |

| Temperature | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More