Semiconductor device and method for fabricating the same

a technology of semiconductor devices and indium ions, applied in the direction of semiconductor devices, electrical equipment, transistors, etc., can solve the problems of abnormal diffusion of indium, low activation rate of indium ions, and inability to obtain sufficient activation concentration, so as to reduce the size of the device, suppress the transient enhanced diffusion of a dopant, and increase the activation rate of the introduced dopant

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

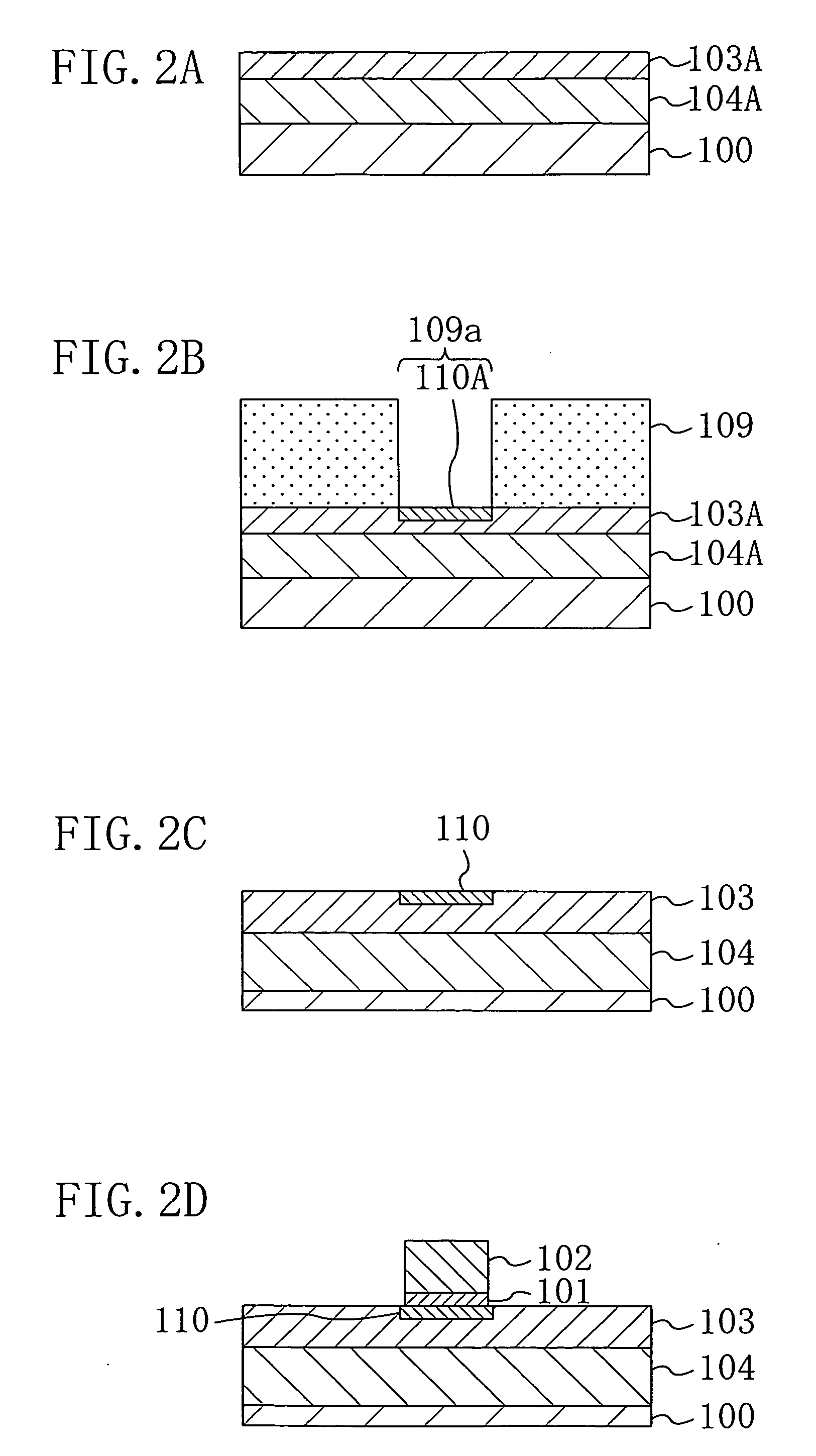

[0061] A first embodiment of the present invention will be described with reference to the accompanying drawings.

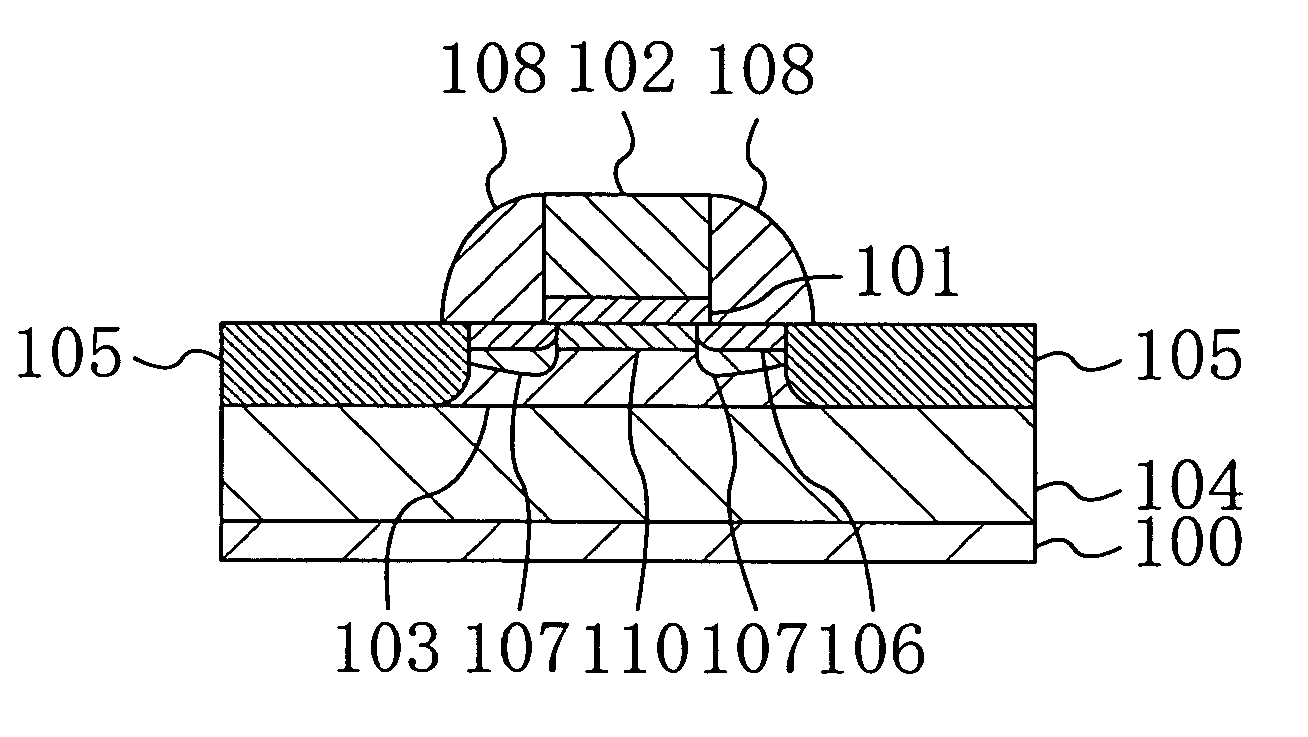

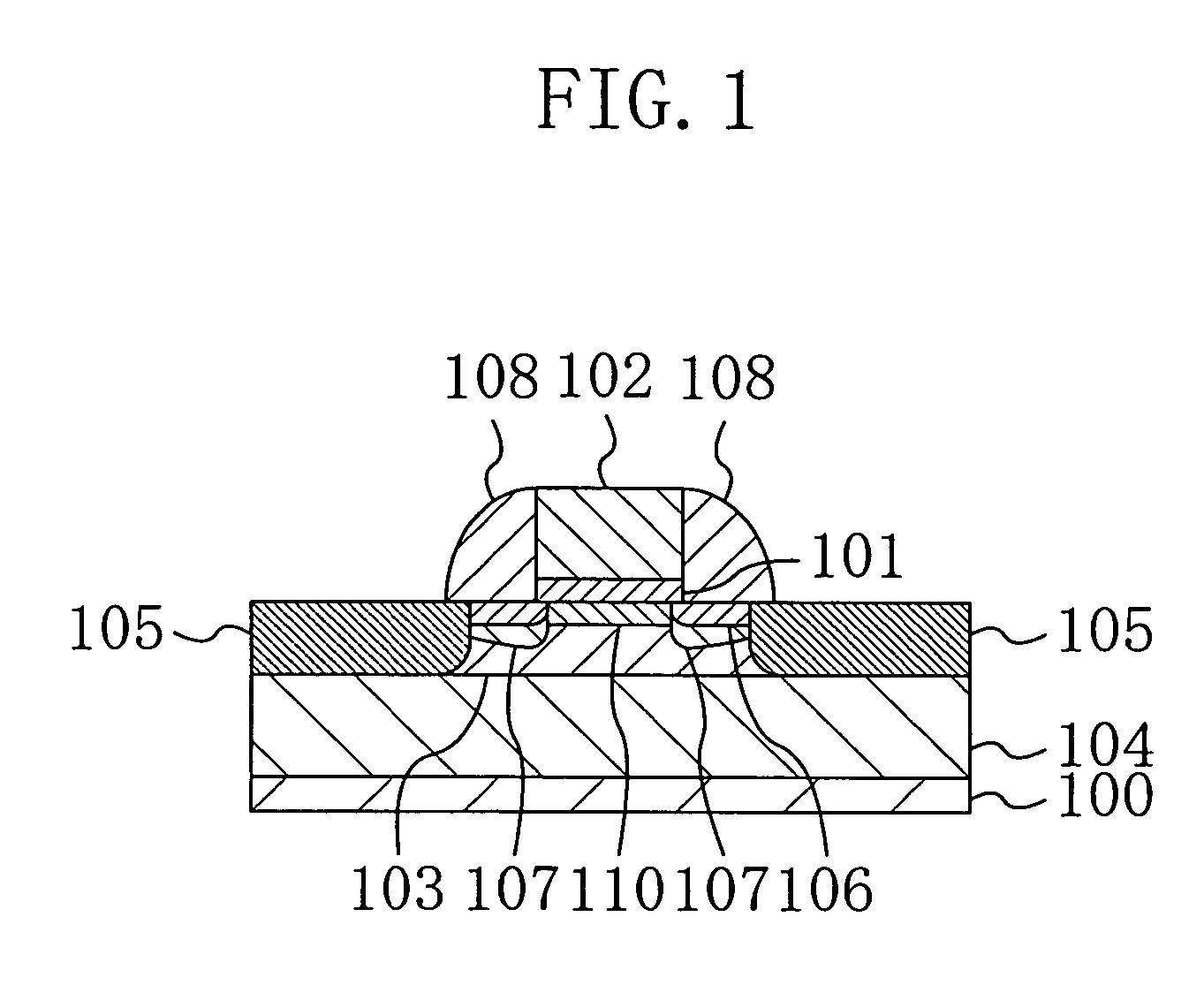

[0062]FIG. 1 illustrates a cross-sectional structure of a semiconductor device, a MIS transistor, according to the first embodiment of the present invention. As shown in FIG. 1, the MIS transistor of the first embodiment includes a gate insulating film 101 selectively formed on the principal surface of a semiconductor substrate 100 made of P-type silicon (Si), and a gate electrode 102 formed on the gate insulating film 101. The gate insulating film 101 is made of silicon dioxide (SiO2) and has a thickness of about 1.5 nm, while the gate electrode 102 is made of polysilicon or polymetal and has a thickness of about 150 nm.

[0063] Sidewalls 108 made of, e.g., silicon nitride (SiNx, for example, Si3N4) are formed on the semiconductor substrate 100 on both lateral faces of the gate insulating film 101 and gate electrode 102.

[0064] A P-type channel doped layer 103 is formed ...

second embodiment

[0080] Hereinafter, a second embodiment of the present invention will be described with reference to the accompanying figures.

[0081]FIG. 4 illustrates a cross sectional structure of a semiconductor device, a MIS transistor, according to the second embodiment of the present invention. In FIG. 4, the same members as those of FIG. 1 are identified by the same reference numerals and the description thereof will be omitted herein.

[0082] As shown in FIG. 4, in the MIS transistor of the second embodiment, a P-type channel doped layer 103, which is located in a semiconductor substrate 100 beneath a gate electrode 102, is formed spaced apart from the inner end portions of N-type heavily doped source / drain layers 105.

[0083] Hereinafter, with reference to the accompanying figures, it will be described how to fabricate a semiconductor device having the above structure.

[0084]FIGS. 5A through 5D and FIGS. 6A through 6D are cross-sectional views indicating process steps for fabricating a semic...

third embodiment

[0099] Hereinafter, a third embodiment of the present invention will be described with reference to the accompanying figures.

[0100]FIG. 7 illustrates a cross sectional structure of a semiconductor device, a MIS transistor, according to the third embodiment of the present invention. In FIG. 7, the same members as those of FIG. 1 are identified by the same reference numerals and the description thereof will be omitted herein.

[0101] As shown in FIG. 7, in the MIS transistor of the third embodiment, a gate electrode 115 is made of metal such as tungsten (W) or tantalum nitride (TaN) and a gate insulating film 114 is formed not only on the principal surface of a semiconductor substrate 100 but also between the gate electrode 115 and the inner lateral faces of sidewalls 108.

[0102] Hereinafter, with reference to the accompanying figures, it will be described how to fabricate a semiconductor device having the above structure.

[0103]FIGS. 8A through 8D and FIGS. 9A through 9E are cross-se...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More