Ion implantation of nitrogen into semiconductor substrate prior to oxidation for offset spacer formation

a technology of offset spacer and semiconductor substrate, which is applied in the direction of semiconductor devices, semiconductor/solid-state device details, electrical equipment, etc., to achieve the effect of suppressing the oxidation of the surfa

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

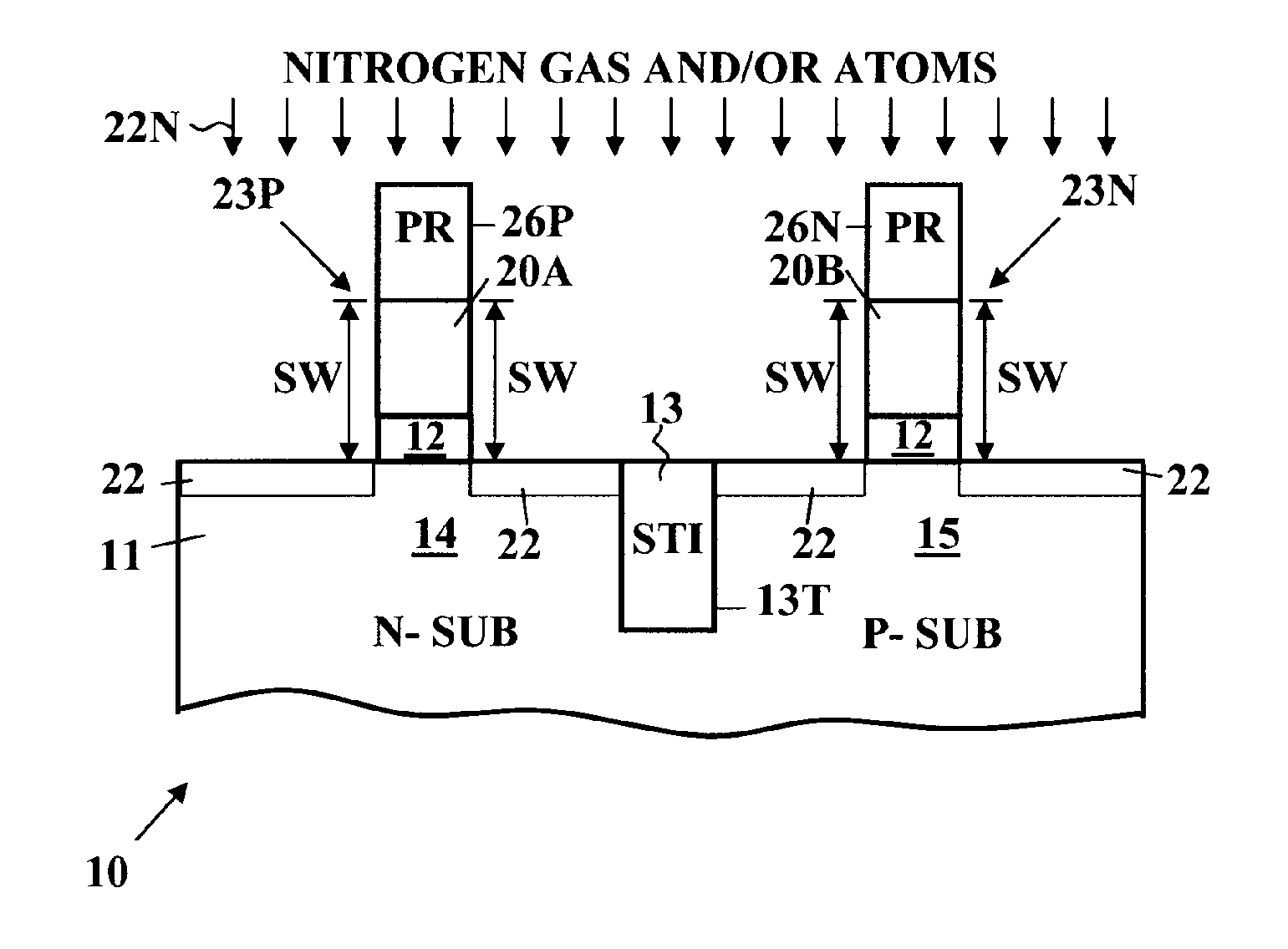

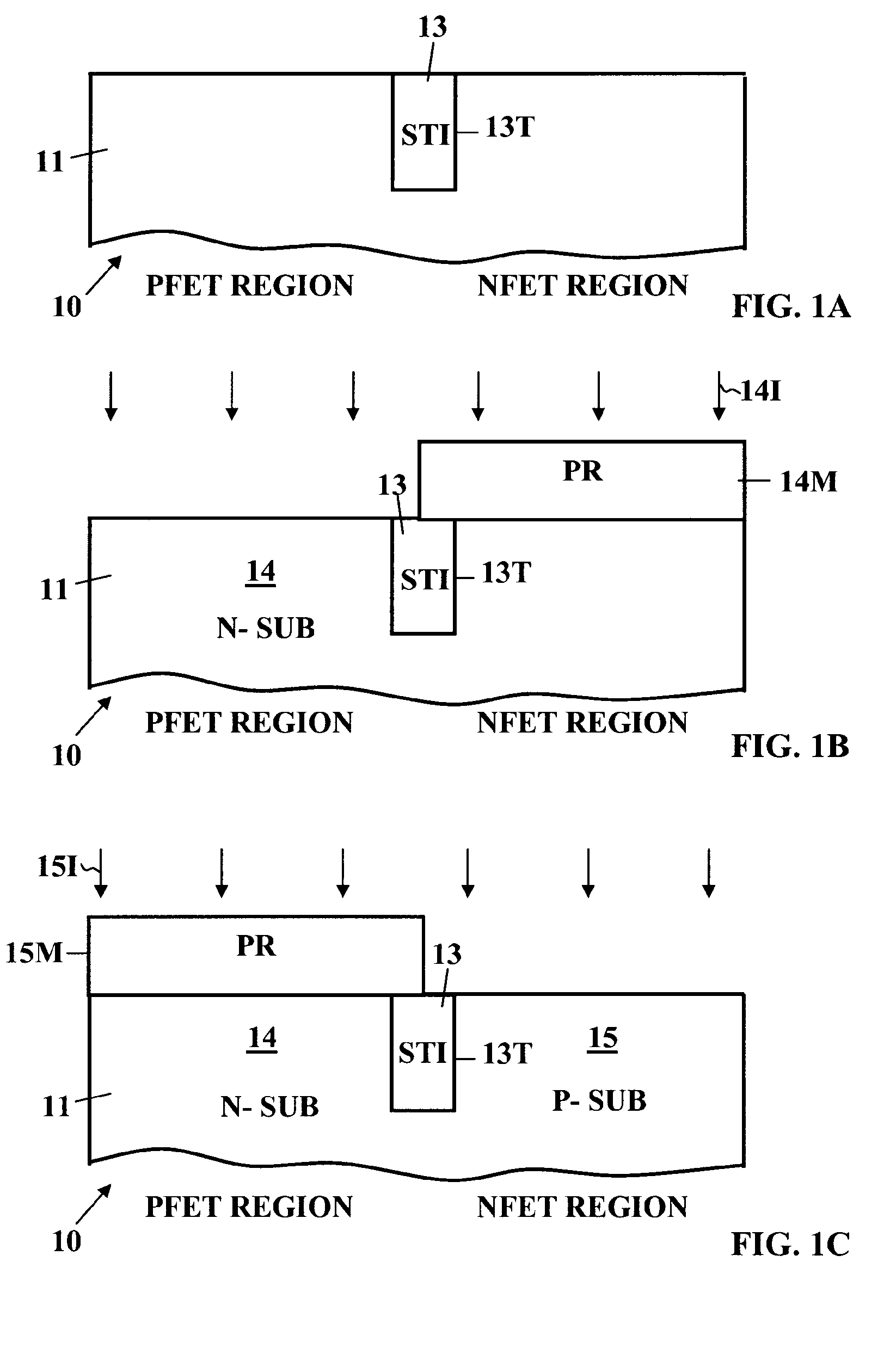

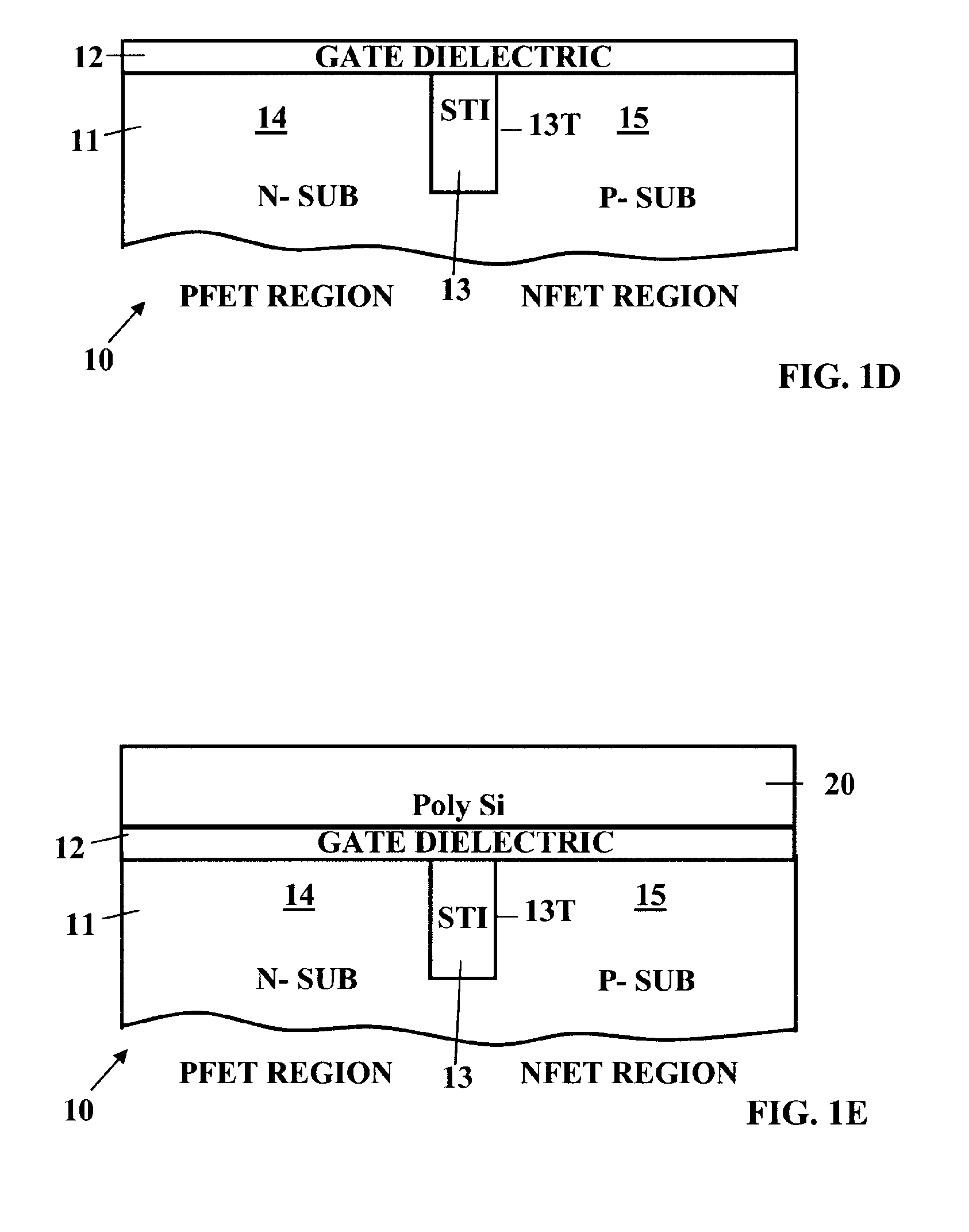

[0034]FIGS. 1A-1O show the process of forming a MOSFET device 10 in accordance with the method of this invention. FIG. 2 is a flow chart of the method of manufacture of the MOSFET device 10 in accordance with the method of this invention as illustrated by FIGS. 1A-1O.

[0035] A. Form STI Dielectric Region In An STI Trench Formed In Semiconductor Substrate

[0036]FIG. 1A is a schematic sectional view of a device 10 in an early stage of manufacture comprising a semiconductor substrate 11 with a top surface in which a shallow trench 13T has been formed. The shallow trench 13T has been filled with dielectric material forming a Shallow Trench Isolation (STI) dielectric region 13. The STI dielectric region 13 in the substrate 11 is formed in accordance with step A in FIG. 2. The STI dielectric region 13 separates the upper portion of the PFET region on the left side of the semiconductor substrate 11 from the upper portion of the NFET region on right side of semiconductor substrate 11, as wi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More