Error Detection/Correction Method

a technology of error detection and correction method, applied in the field of wafer-scale integrated circuit system, can solve the problems of failure of wafer-scale system, large part or the whole system is not functional, and its total area, and achieve high cache hit rate, high defect tolerance, and facilitate dynamic address mapping

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

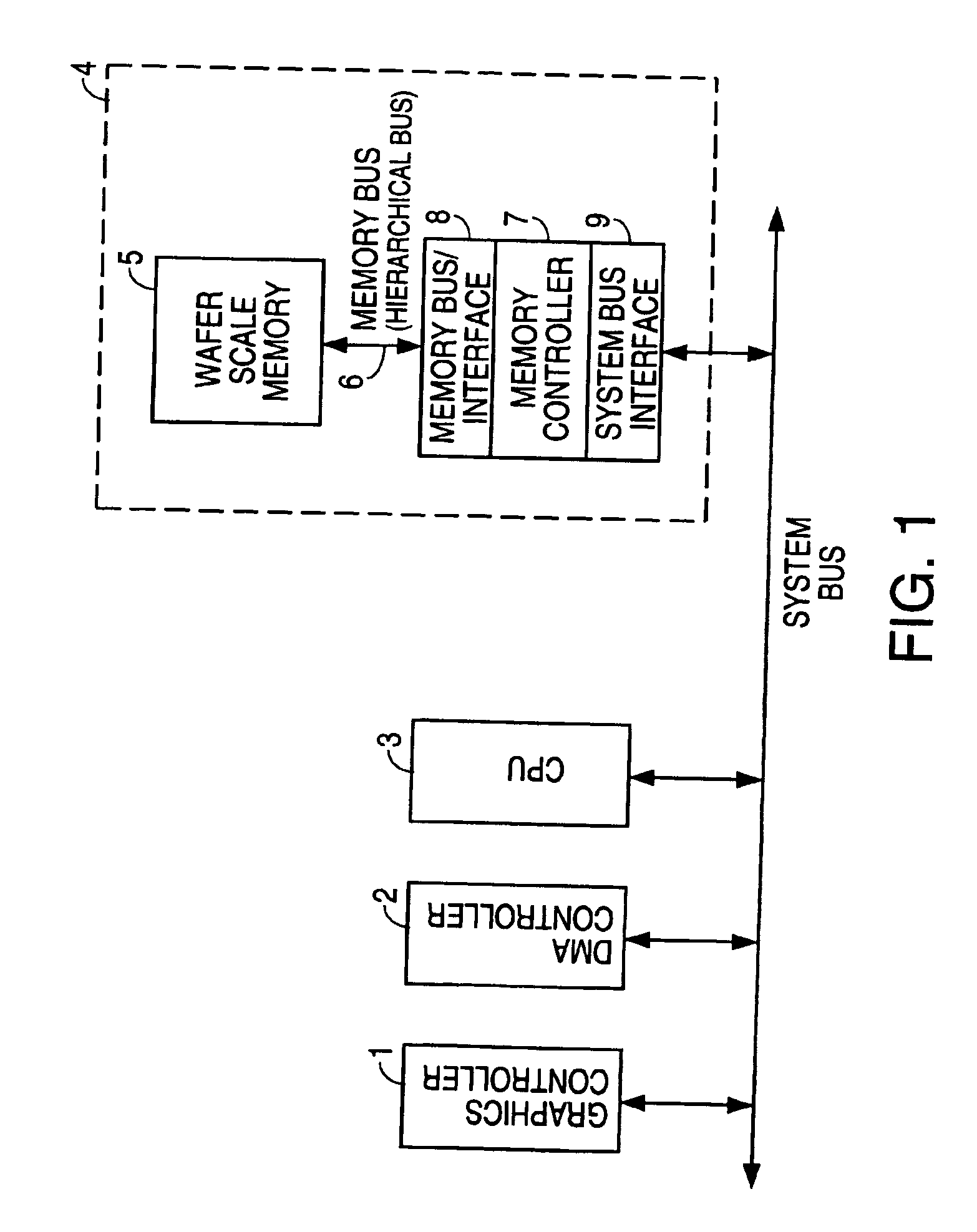

[0059]As illustrated in FIG. 1, a memory sub-system according to the present invention is used in a digital system, which consists of a wafer scale memory 5, hierarchical memory bus 6 and a memory controller 7. The memory controller 7 controls memory access and comprises a memory bus interface 8 for communicating to the hierarchical bus 6, and a system bus interface 9 for communicating to the system bus 10. The system bus 10 connects the memory subsystem to the memory request devices which are CPU 3, DMA controller 2 and graphics controller 1.

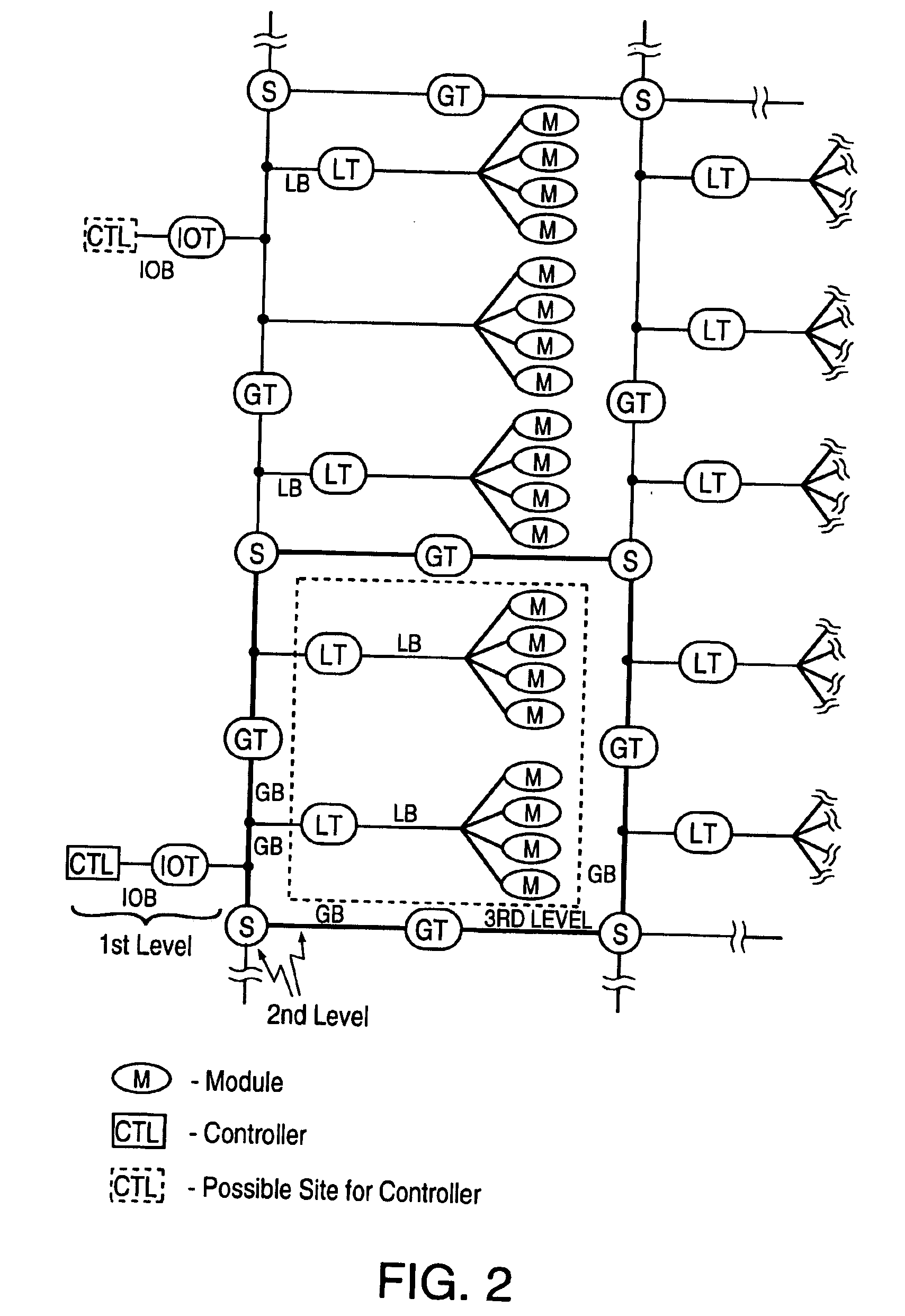

[0060]The bus has a hierarchical structure which can be distinguished into 3 levels. As illustrated in FIG. 2, the first level or the root level has a few branches (IOB) for connecting the memory controller to the second level. In most cases, only one branch is used for the connection, unless multiple controllers are used, the other branches are used for spares. The root branches (IOB) are connected to the second level through the input-output ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More