Fabrication of self-aligned gallium arsenide mosfets using damascene gate methods

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0010]In the following detailed description of the embodiments, reference is made to the accompanying drawings that form a part hereof, and in which are shown by way of illustration, and not by way of limitation, specific embodiments in which the invention may be practiced. It is to be understood that other embodiments may be utilized and that logical, mechanical and electrical changes may be made without departing from the spirit and scope of the present invention.

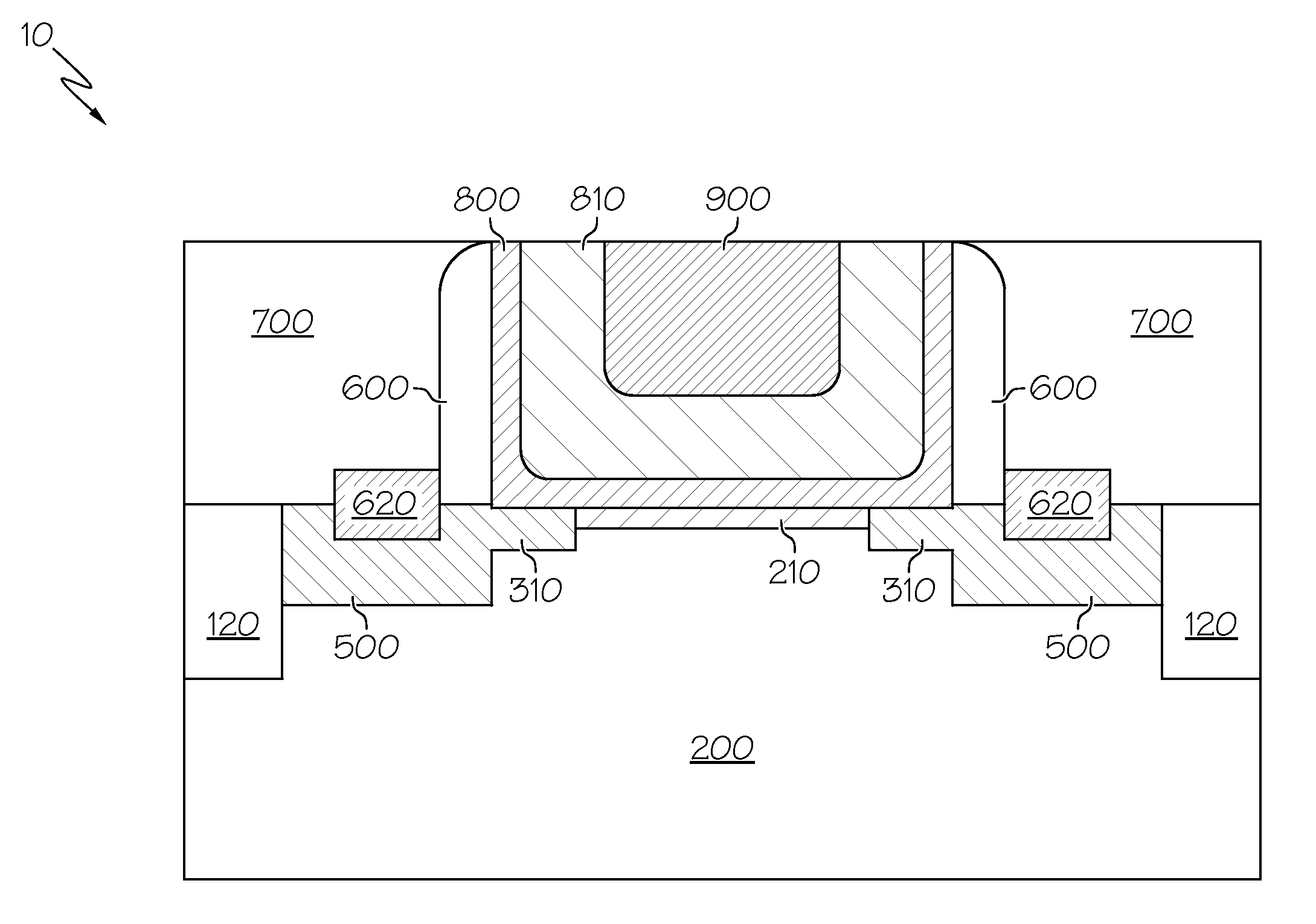

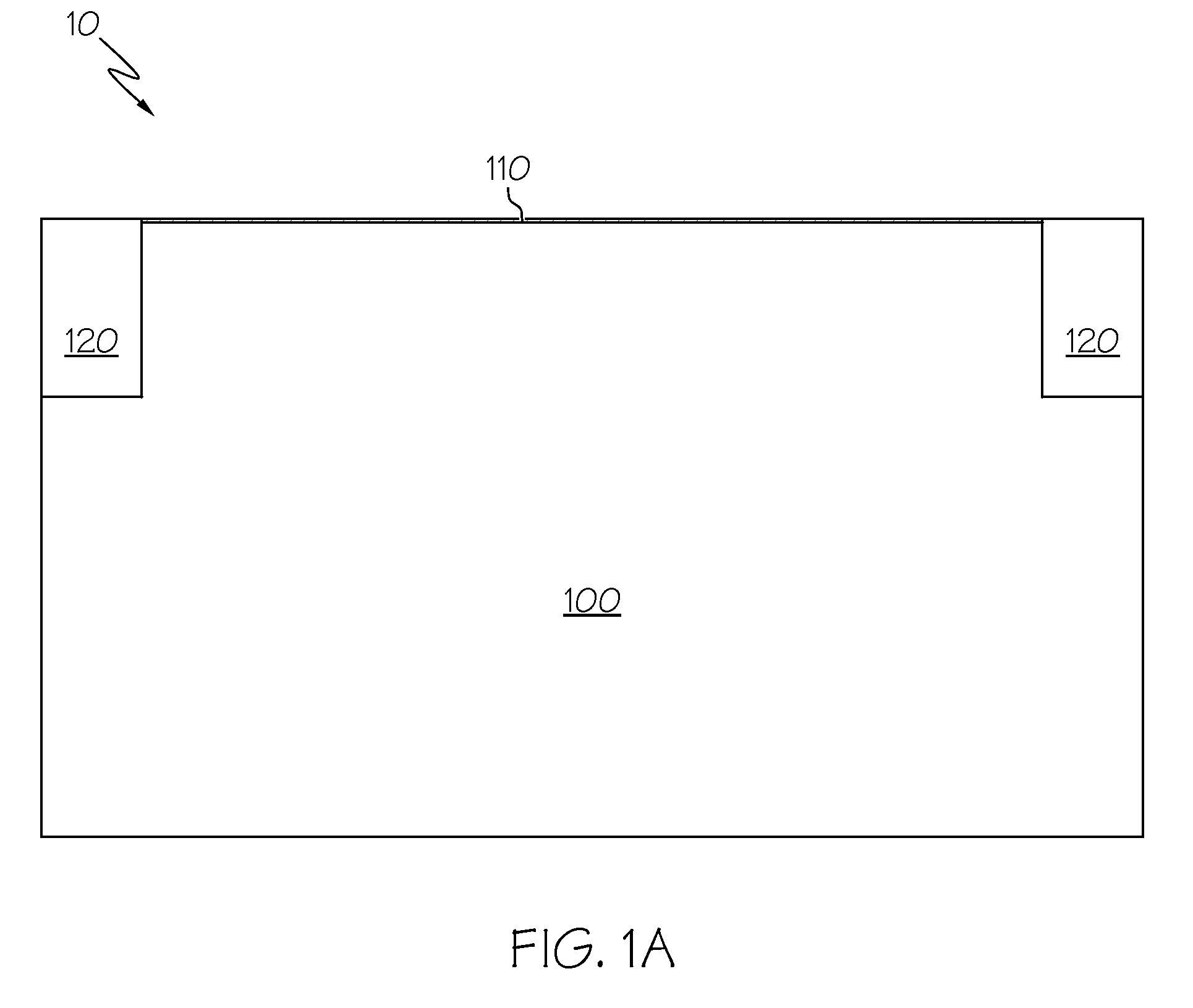

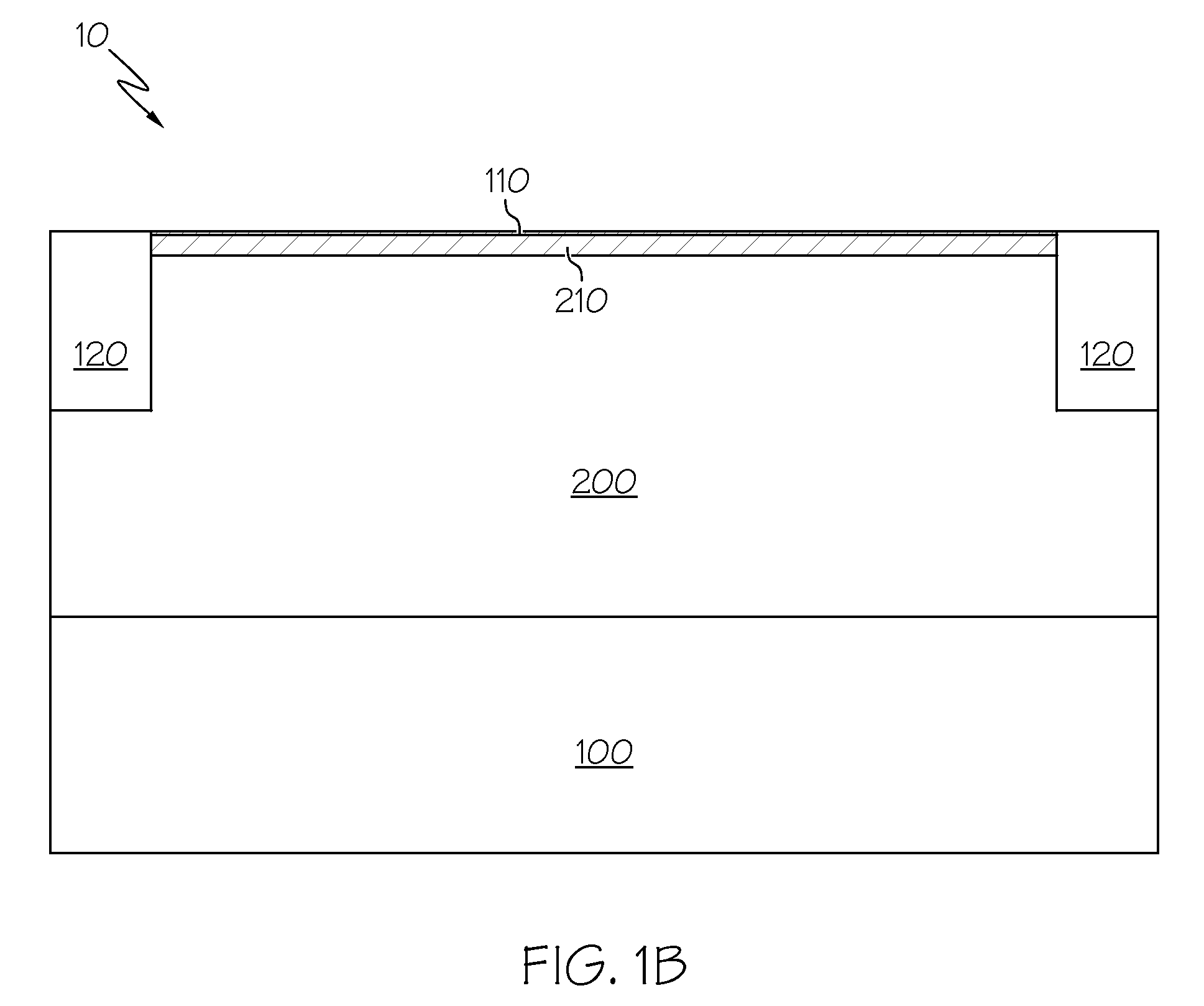

[0011]FIGS. 1a-1m illustrate the formation of a self-aligned GaAs MOSFET device 10 with high-k gate dielectrics using damascene gate methods in a stepwise fashion. Referring to FIG. 1a, a substrate 100 of bulk undoped orientated GaAs wafer is generally provided. A sacrificial oxide layer 110, comprising, for example, SiO2 or any other suitable sacrificial material, can be deposited over the substrate 100 using conventional deposition methods such as, for example, low pressure chemical vapor deposition (LPCVD). The thickn...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More