Method of forming semiconductor device and semiconductor device

a technology of semiconductor devices and semiconductor films, applied in the direction of semiconductor devices, basic electric elements, electrical apparatus, etc., can solve the problems of increasing the interface layer of high-dielectric-constant insulation films, increasing in-plane variations, and increasing undesirable effects of interface layer deterioration, so as to achieve excellent in-plane uniformity, high film density, and low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

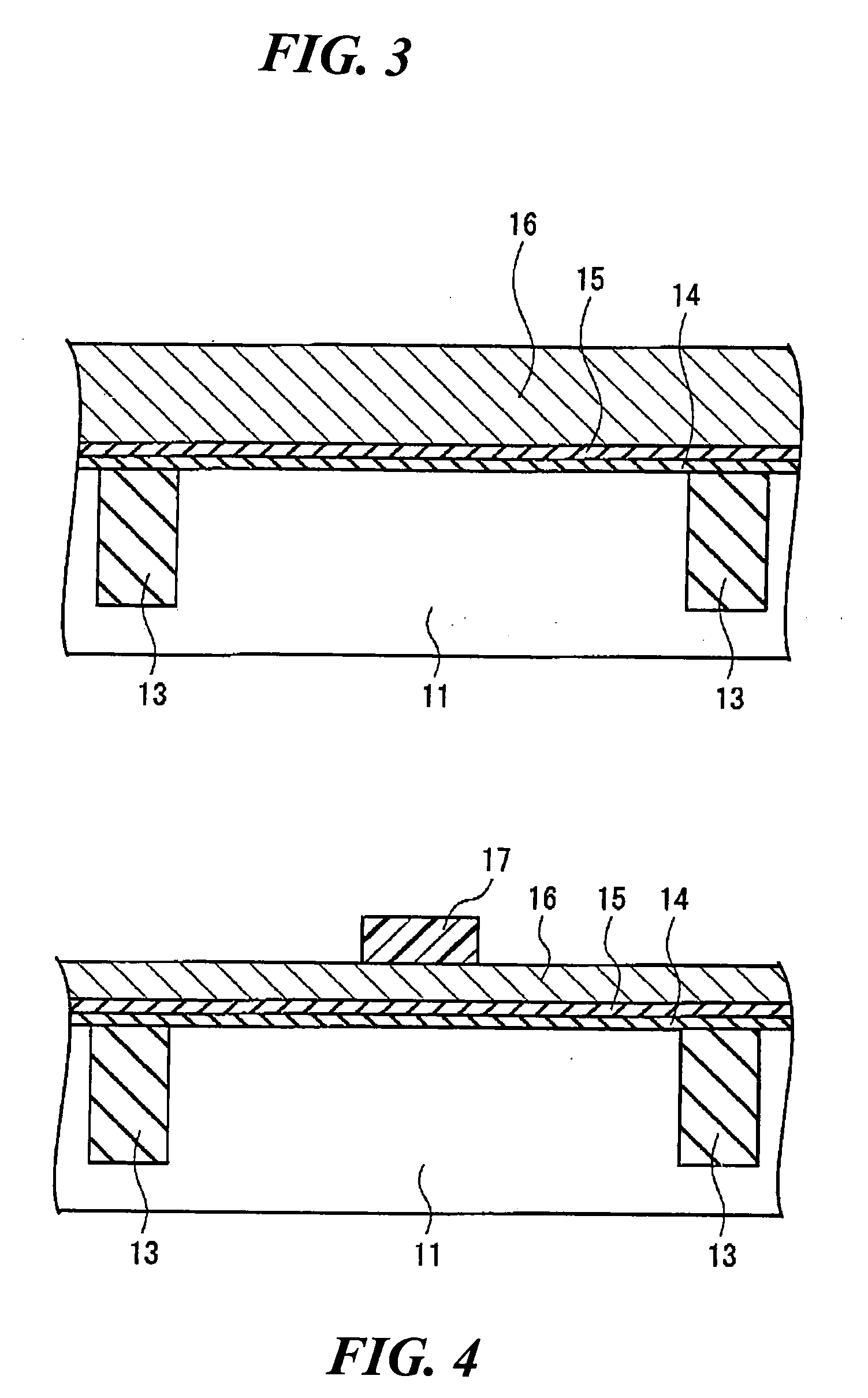

[0039]Referring now to the drawings, wherein like reference numerals designate identical or corresponding parts through out the several views, the present invention will be described.

[0040]Unless specifically defined, all technical and scientific terms used herein have the same meaning as commonly understood by a skilled artisan in microfabrication and semiconductor manufacturing.

[0041]All methods and materials similar or equivalent to those described herein can be used in the practice or testing of the present invention, with suitable methods and materials being described herein. All publications, patent applications, patents, and other references mentioned herein are incorporated by reference in their entirety. In case of conflict, the present specification, including definitions, will control. Further, the materials, methods, and examples are illustrative only and are not intended to be limiting, unless otherwise specified.

[0042]As a first embodiment of the present invention, a d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More