Integrated circuit apparatus

a circuit apparatus and integrated circuit technology, applied in the field of integrated circuit apparatuses, can solve the problems of increasing the number of latches, the problem of latches still remaining, and the inability to latch up, so as to avoid the effect of data loss, facilitate the recovery of lost data, and limit the range of data loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

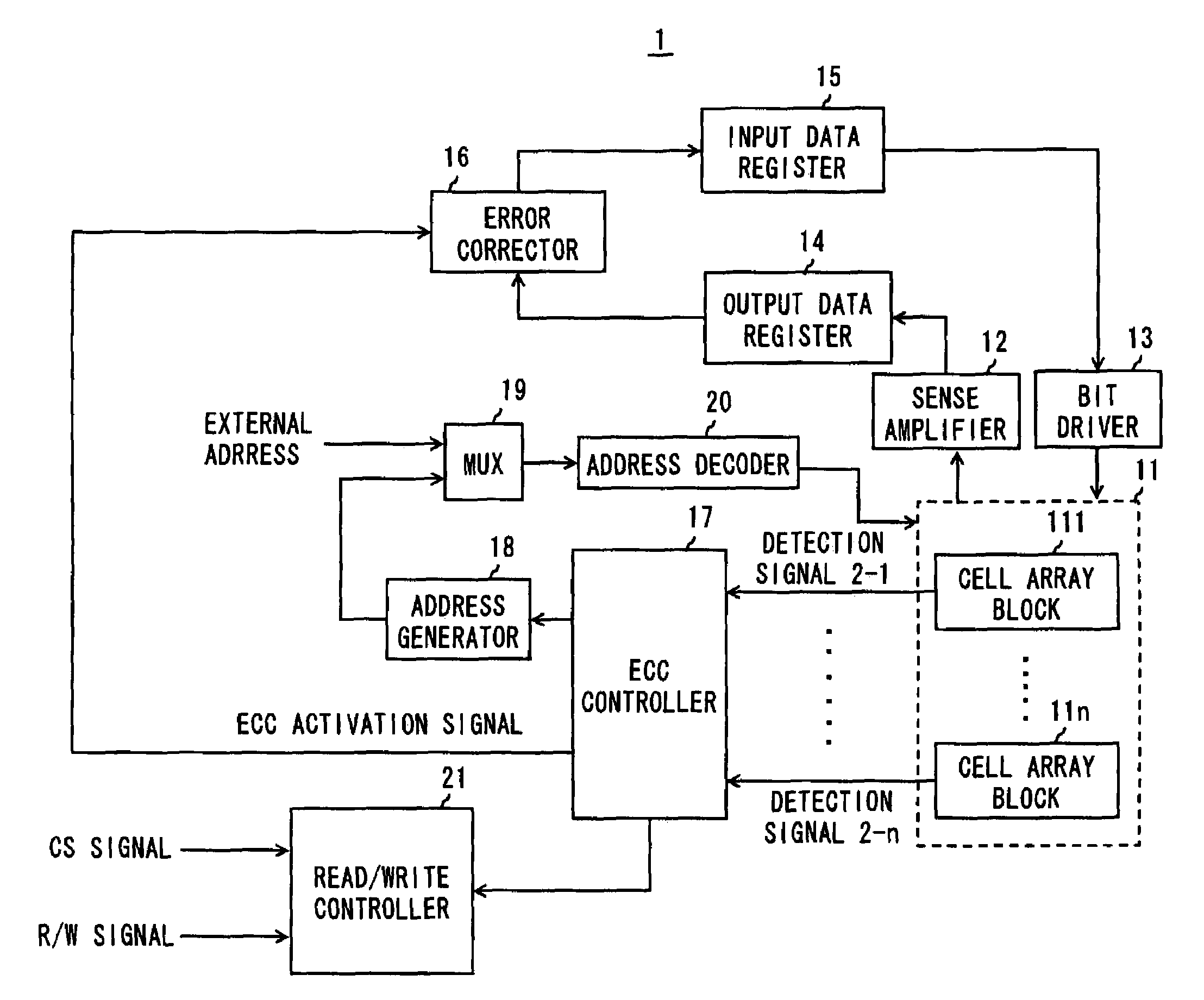

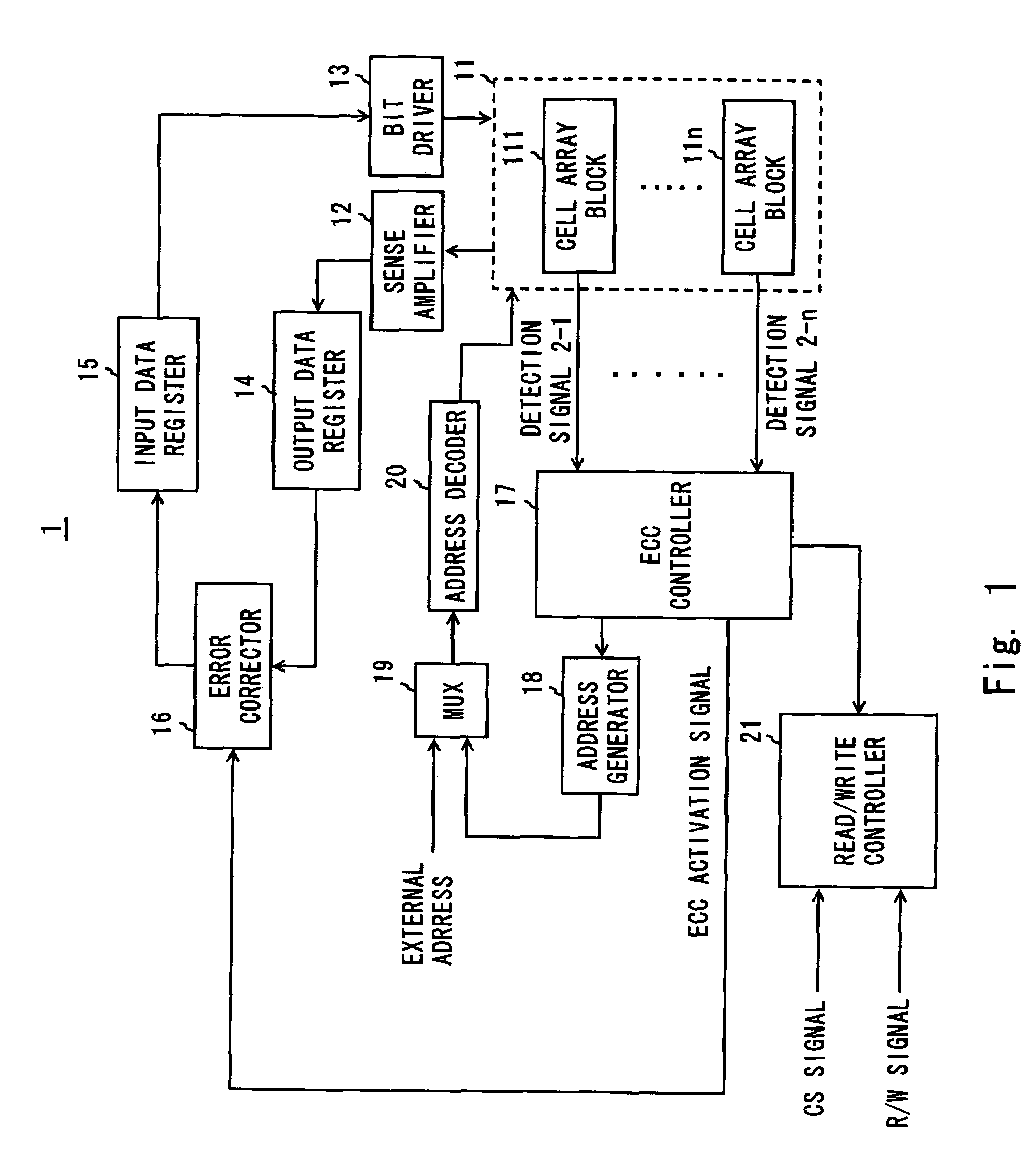

[0032]FIG. 1 shows the configuration of an integrated circuit apparatus 1 according to an embodiment of the present invention. A cell array 11 is an SRAM cell array where memory cells formed of CMOSFET are arranged lattice-like. The cell array 11 is divided into one or a plurality of cell array blocks 111 to 11n. Each of the cell array blocks has a configuration where memory cells are arranged lattice-like, and each memory cell is connected to a word line (row selection line) and a bit line (column selection line). The detailed configuration of the cell array block 111 of this embodiment is described later. A sense amplifier 12 and a bit driver 13 are connected to a bid line of the cell array 11. In data reading, the sense amplifier 12 detects and amplifies information of the memory cell and stores the read data into an output data register 14. In data writing, the bid driver 13 is driven according to information of input data register 15 and writes data to the memory cell.

[0033]The...

second embodiment

[0057]FIG. 7 shows the configuration of an integrated circuit apparatus 2 according to another embodiment of the present invention. The integrated circuit apparatus 2 is different from the integrated circuit apparatus 1 of the first embodiment in having a WAIT signal output circuit 22. The WAIT signal output circuit 22 supplies a WAIT signal to an external CPU or the like during error correction by ECC processing in order to notify the external CPU or the like that the error correction is currently being performed. The WAIT signal is a signal for indicating an external CPU or the like to wait without memory access.

[0058]The timing to output the WAIT signal may be set by indicating the output of the WAIT signal to the WAIT signal output circuit 22 in accordance with the timing when the ECC controller 17 outputs an ECC activation signal to indicate the data recovery to the error corrector 16. The functions of the other components of the integrated circuit apparatus 2 are the same as t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More