High, depth and width three-dimensional uprightness interconnect and realization method of three-dimensional integrate circuit

An integrated circuit and vertical interconnection technology, applied in circuits, electrical components, electrical solid devices, etc., can solve problems such as difficulty in ensuring the insulation effect of interconnecting lines, difficulty in insulating layer growth, and limiting interconnection line density, etc. High-density 3D vertical interconnects, eliminating dependencies, avoiding the effects of voids and gaps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

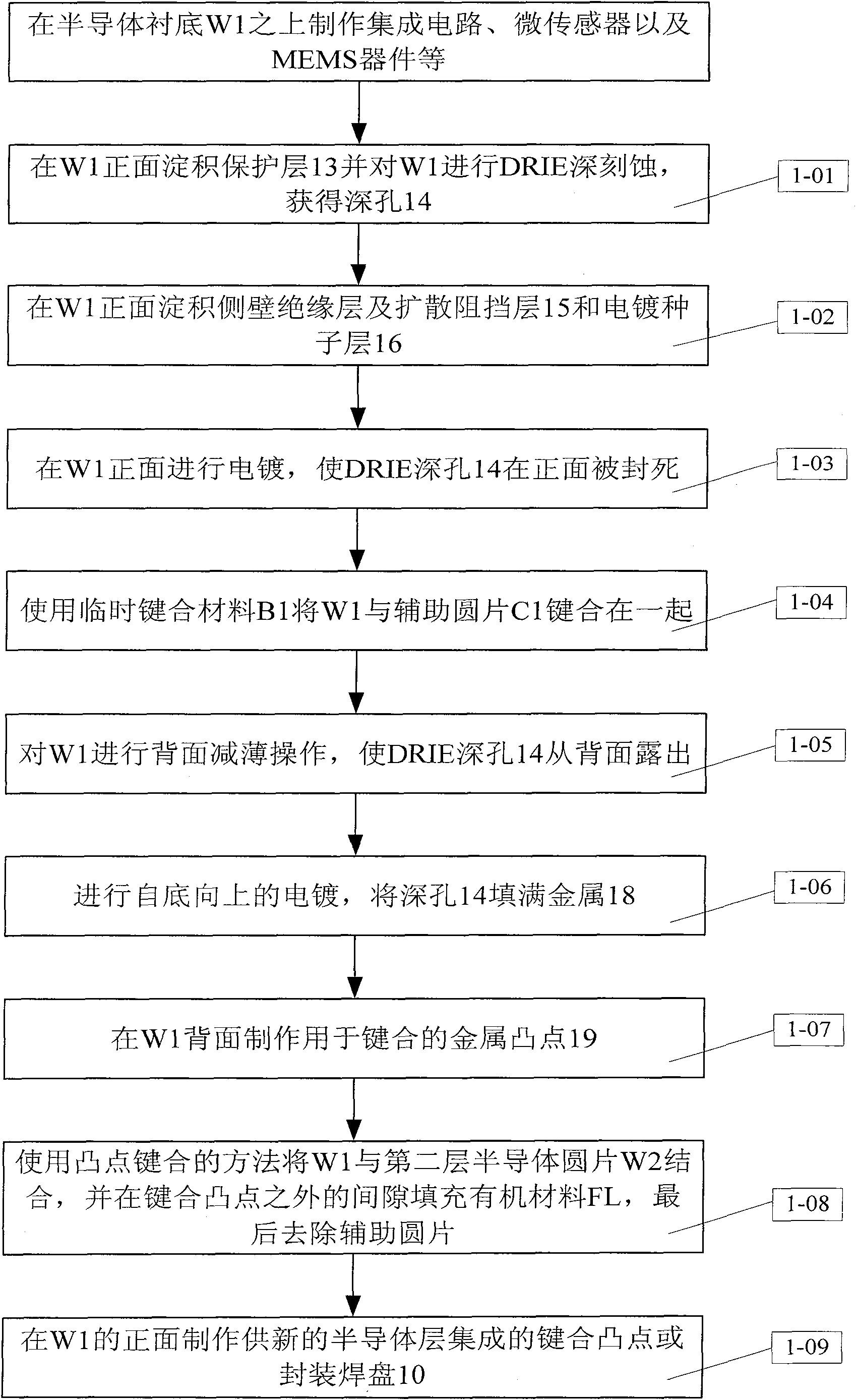

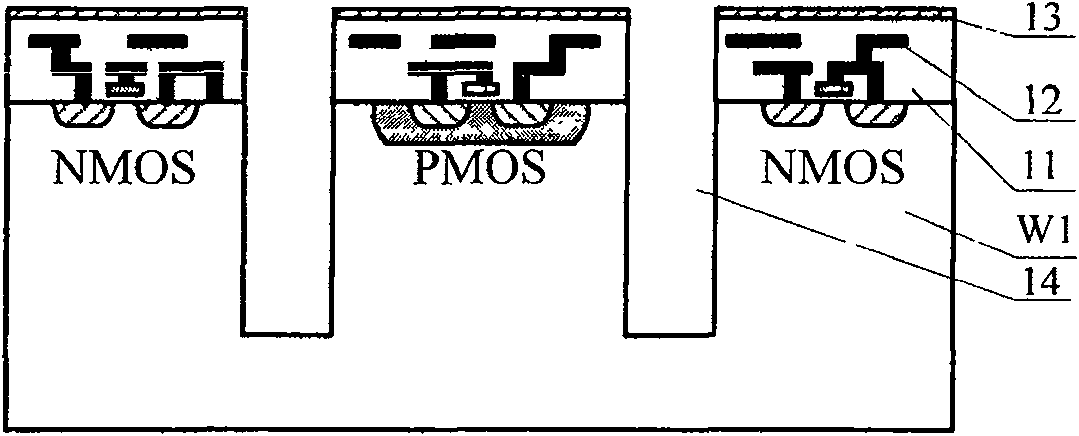

[0037] The present invention provides a method for realizing high aspect ratio three-dimensional vertical interconnection and three-dimensional integrated circuit. Consistent etching of through holes with different aspect ratios and avoiding lateral etching, using double-sided deposition of insulating layer, diffusion barrier layer and electroplating seed layer to solve the internal insulating layer, diffusion barrier layer and electroplating seed layer of high aspect ratio through holes The problem of difficult deposition, and the bottom-up electroplating process to fill the through-holes overcomes the problem that the single-sided Damascus electroplating high aspect ratio structure is prone to gaps.

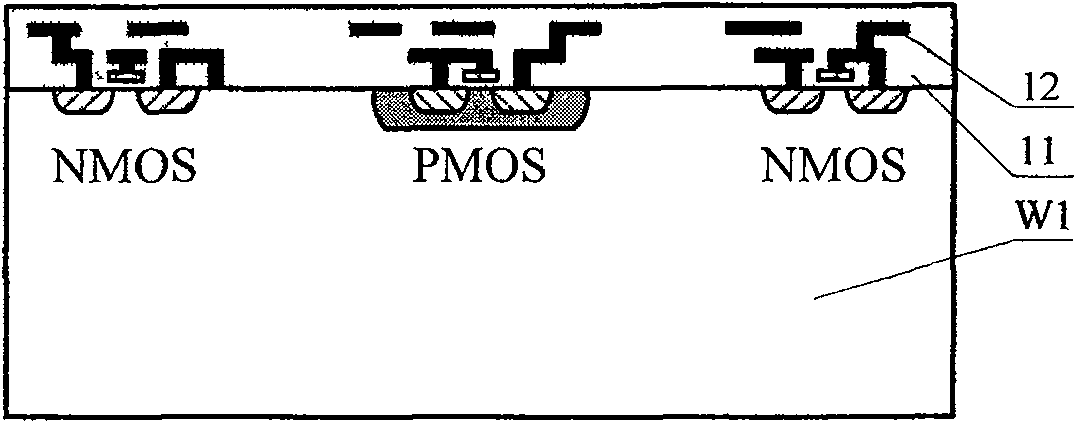

[0038] The embodiments of the present invention will be further described in detail below in conjunction with the accompanying drawings. Embodiments of the present invention provide a simple and feasible method for realizing a three-dimensional integrated circuit based on elect...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More