Process for preparing isolation of shallow channel

A manufacturing method and shallow trench technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as threshold voltage drop, leakage current increase, affecting device performance, etc., to prevent threshold voltage drop, The effect of reducing leakage current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0035] Figure 7 It is a flow chart of an embodiment of the manufacturing method of the shallow trench isolation of the present invention.

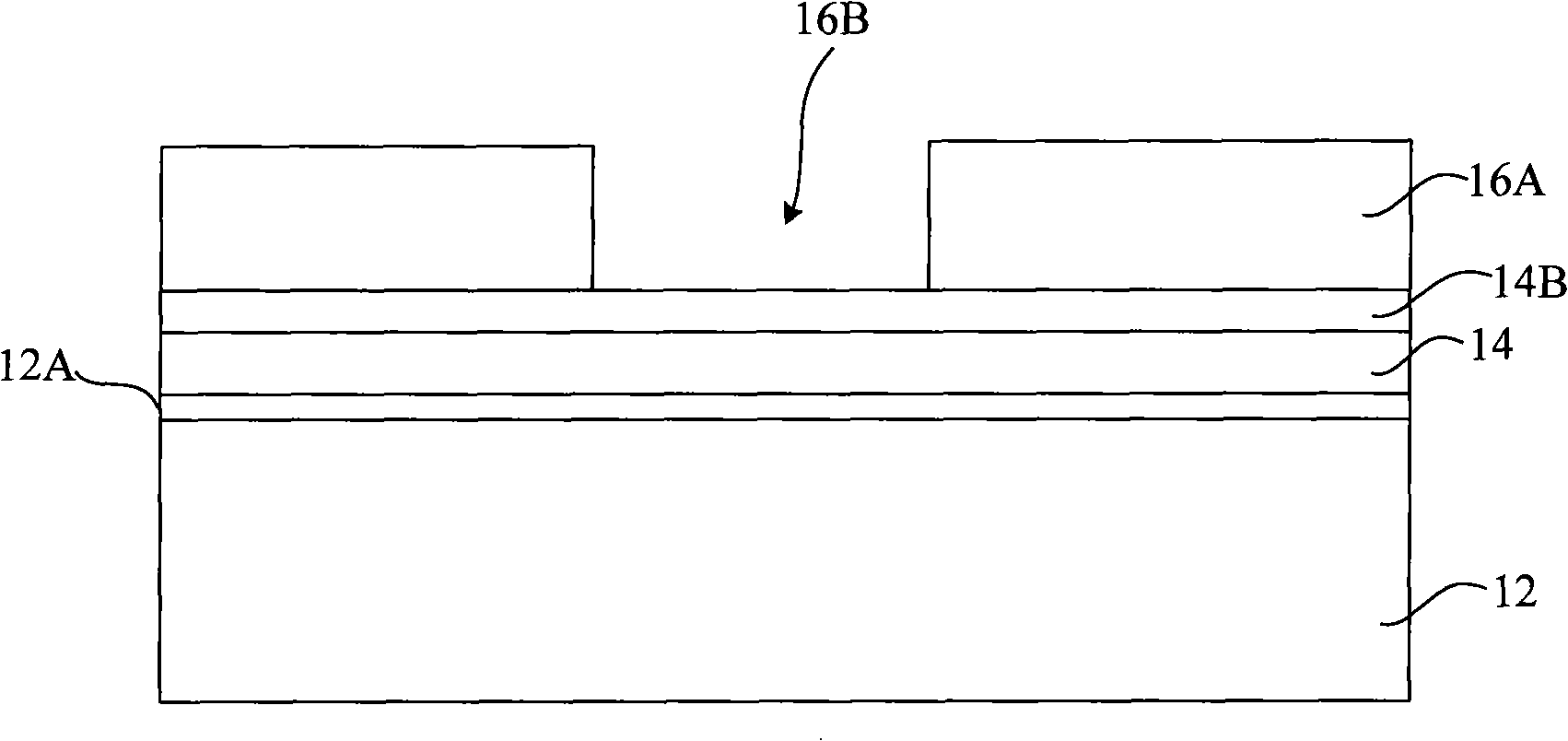

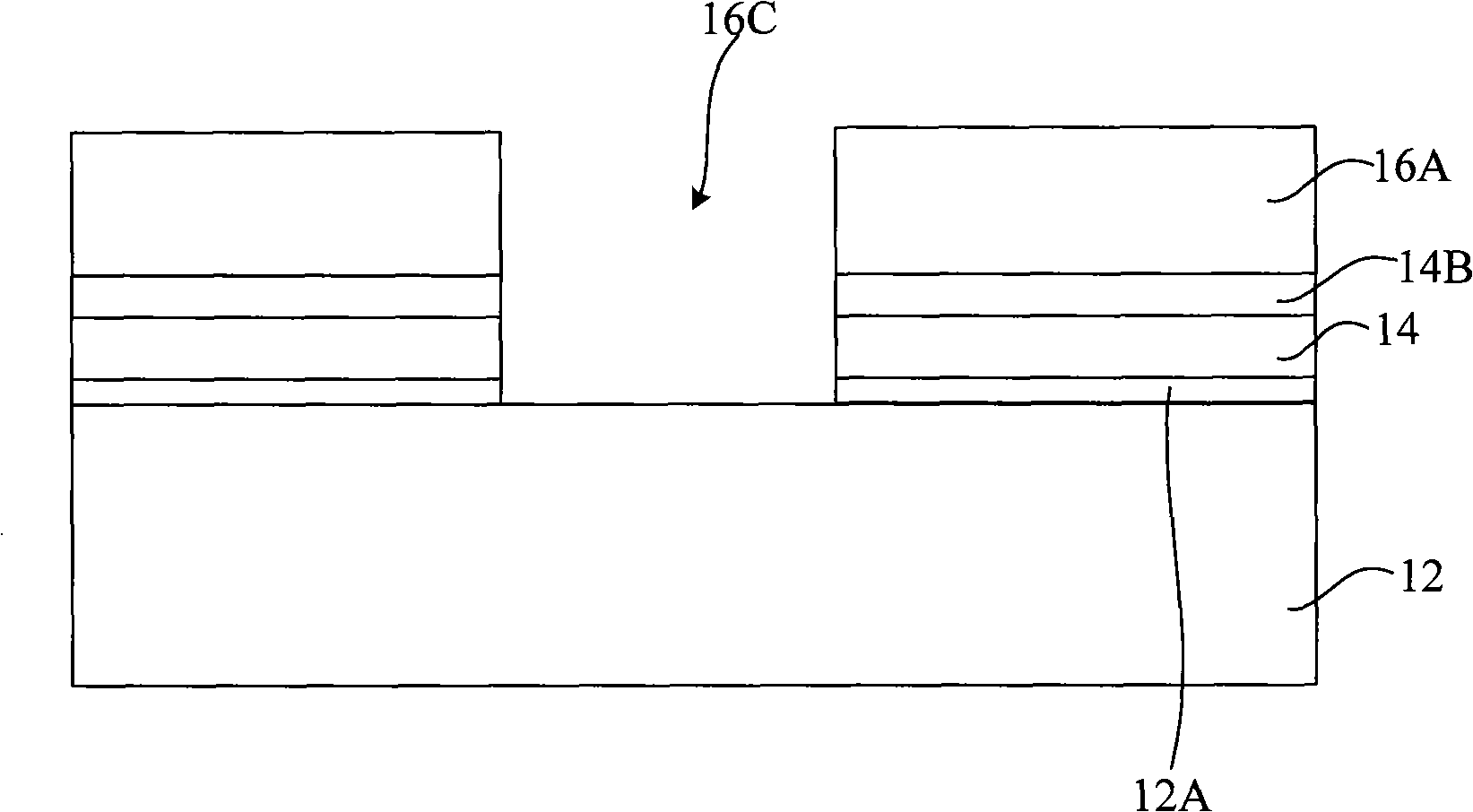

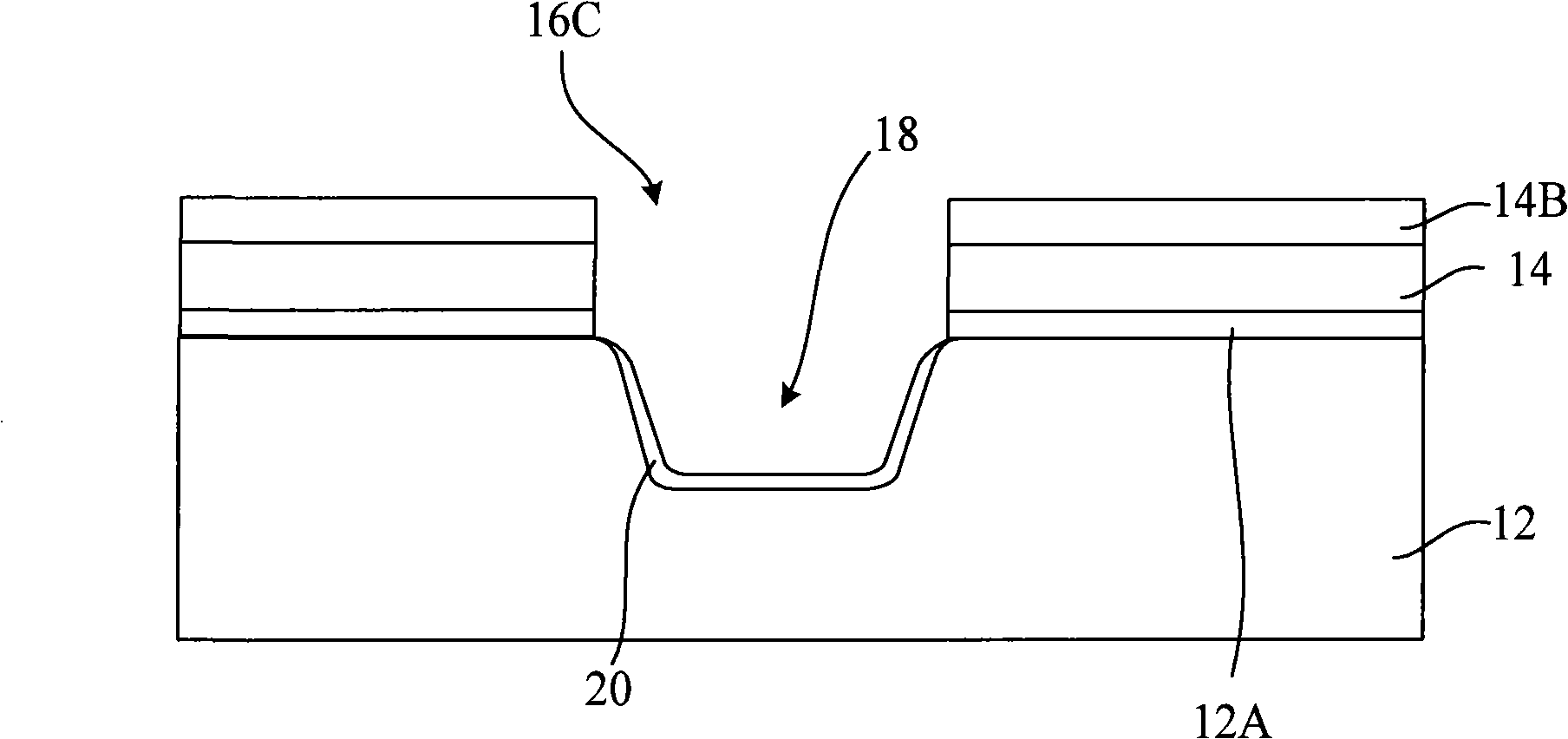

[0036] Such as Figure 7 As shown, in step 1, a semiconductor substrate is provided (S100); a pad oxide layer and a hard mask layer are sequentially formed on the semiconductor substrate, a groove is formed in the semiconductor substrate, and a pad is formed on the pad The oxide layer and the hard mask layer have openings at positions corresponding to the grooves.

[0037] Such as Figure 8 As shown in the cross-sectional schematic diagram, the semiconductor substrate 100 can be one of single crystal silicon, polycrystalline silicon, and amorphous silicon, and the semiconductor substrate 100 can also be one of silicon-germanium compounds and silicon-gallium compounds. The substrate 100 may include...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More