Integrated circuit setting and production method especially for structuration

A technology of integrated circuits and production methods, applied in the field of setting and production of structured application-specific integrated circuits, can solve problems such as large static leakage and power consumption, and achieve the effects of high utilization rate and large flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

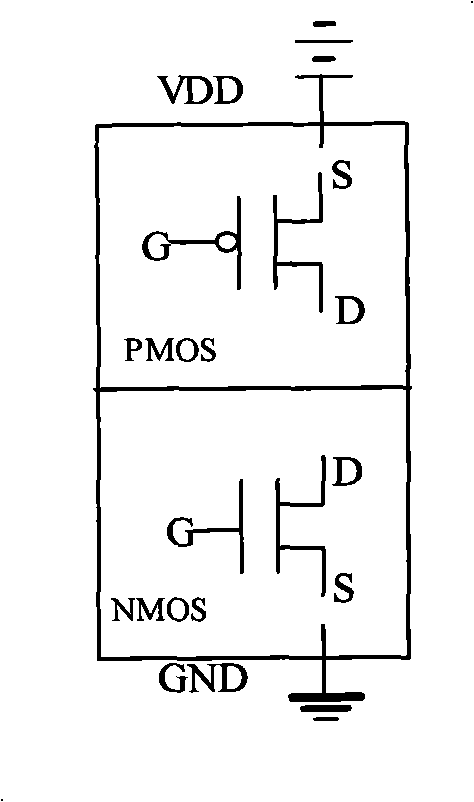

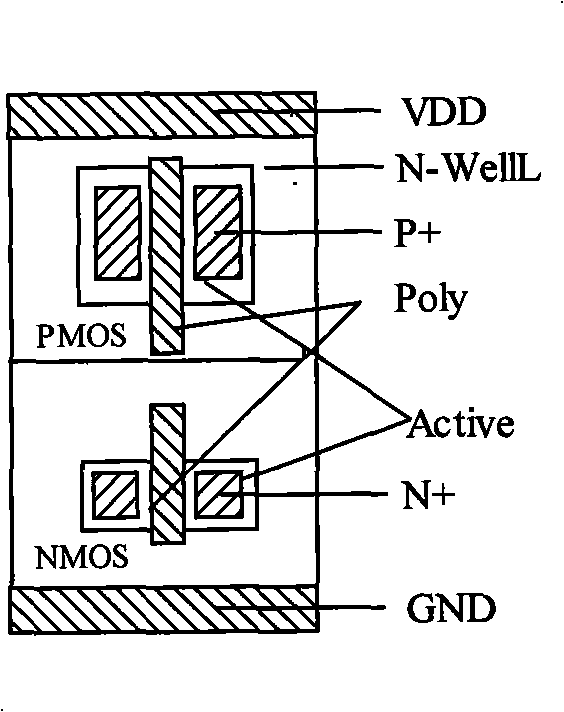

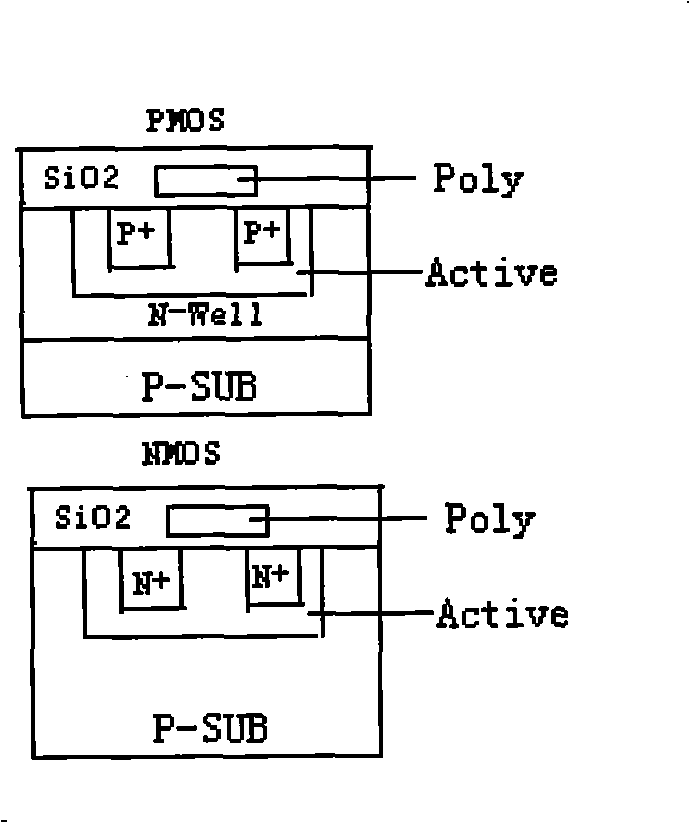

[0029] The present invention will be further described in detail below with reference to the drawings and embodiments. Such as Picture 1-1 , Figure 1-2 with Figure 1-3 As shown, in the method of the present invention, the small-granularity macro cell GCELL is set up to establish an N-channel metal-oxide-semiconductor field effect transistor NMOS on a P-type silicon substrate P-sub, and N-well in the N-well region The P-channel metal-oxide-semiconductor field effect transistor PMOS is established inside. The drain terminal D, source terminal S, and gate G of the NMOS tube and PMOS tube are all suspended, and the length and width of the CELL are grids (the minimum wiring pitch is the unit Grid). In the circuit structure, the PMOS tube and NMOS tube are connected to other circuit parts of the outside world through the drain D, source S, and gate G to realize a complete circuit; in terms of the physical structure, the polysilicon poly, high-concentration P-type ion doped area P + Z...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More