Field effect transistor device with graphene as electrode and method for producing the same

A technology of field-effect transistors and graphene, which is applied in the direction of electrical solid-state devices, semiconductor/solid-state device manufacturing, semiconductor devices, etc., to achieve the effects of size reduction, high response sensitivity, and high application value

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

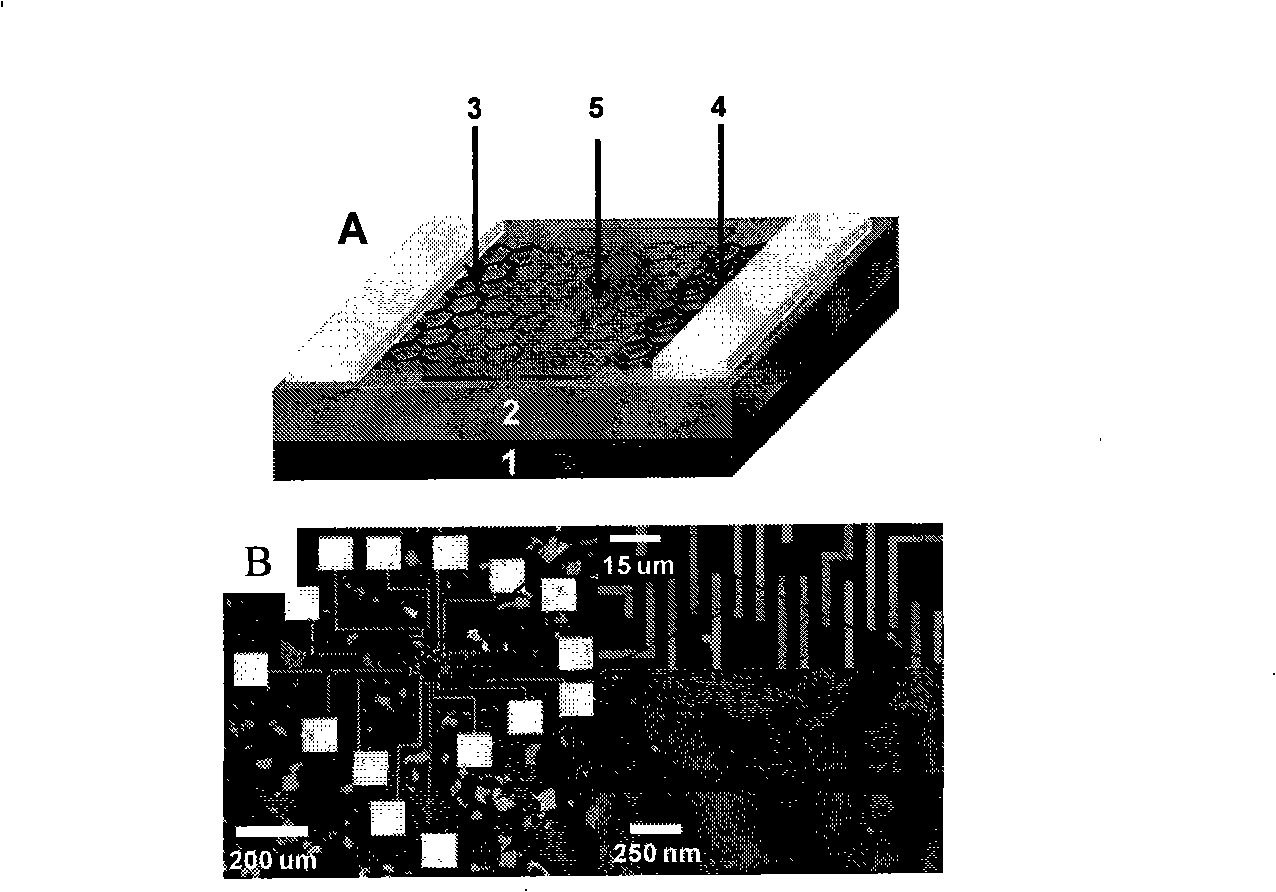

[0026] Embodiment 1, preparation nanoscale field effect transistor device

[0027] The preparation method of the nanoscale field effect transistor device comprises the following steps:

[0028] 1) On a heavily doped silicon substrate containing a layer of 300nm thick silicon dioxide, graphite without any processing is placed on the substrate and peeled off repeatedly to obtain graphene;

[0029] 2) Patterning graphene by electron beam etching method;

[0030] 3) cover the patterned graphene obtained in step 2) with a metal mask, and utilize thermal evaporation method to obtain Cr layer and Au layer (5 nanometers / 40 nanometers) successively on the silicon substrate surface, and Au / Cr is used as the metal source and drain regions.

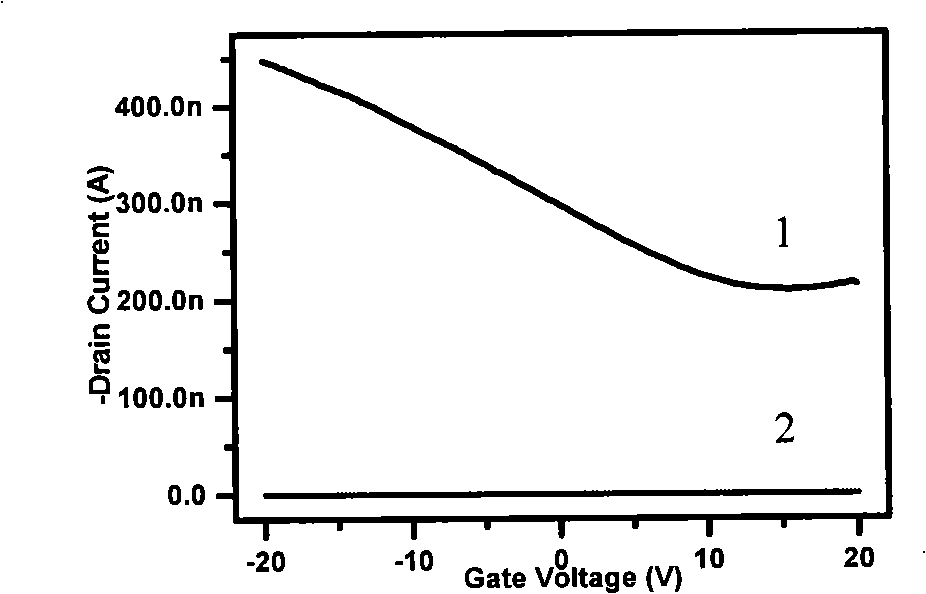

[0031] 4) A layer of PMMA (950, A2) was spin-coated on the surface of the above-mentioned transistor, the spin-coating rate was 4000PRM, the spin-coating time was 45s, and then dried at 170° C. for 2 minutes. Using an electron beam etching method,...

Embodiment 2

[0037] Embodiment 2, preparation nanoscale field effect transistor device

[0038] The preparation method of the nanoscale field effect transistor device comprises the following steps:

[0039] 1) On a heavily doped silicon substrate containing a layer of 300nm thick silicon dioxide, graphite without any processing is placed on the substrate and peeled off repeatedly to obtain graphene;

[0040] 2) Patterning graphene by electron beam etching method;

[0041] 3) cover the patterned graphene obtained in step 2) with a metal mask, and utilize thermal evaporation method to obtain Cr layer and Au layer (5 nanometers / 40 nanometers) successively on the silicon substrate surface, and Au / Cr is used as the metal source and drain regions.

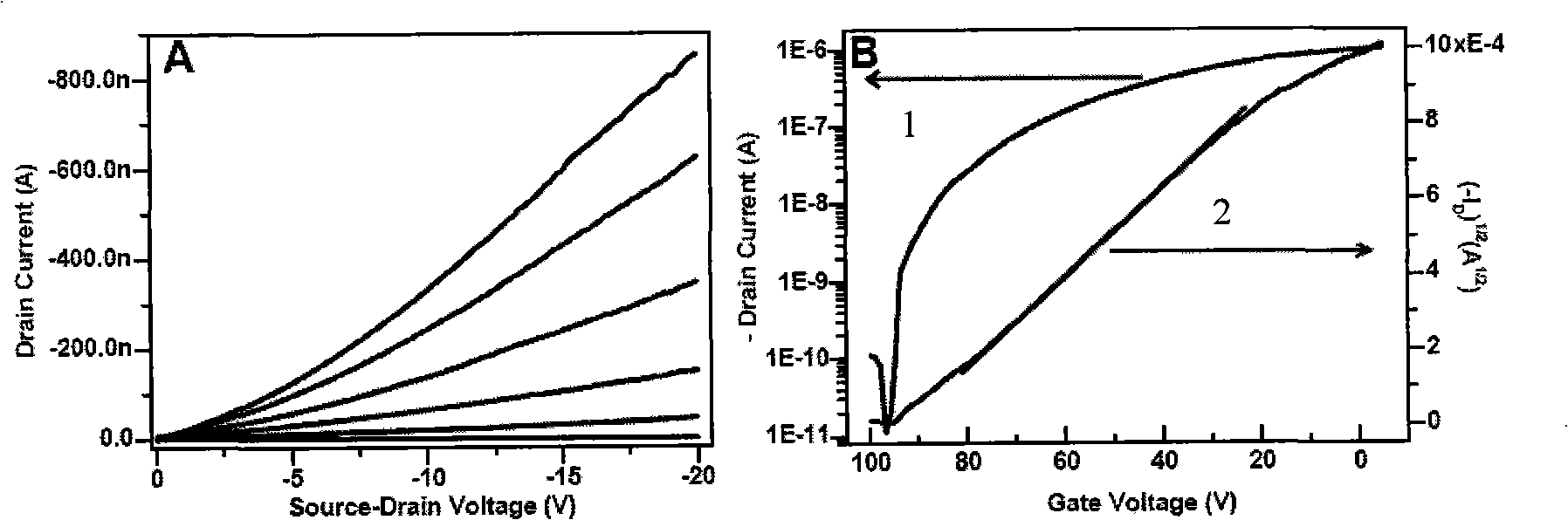

[0042] 4) After spin-coating (4000PRM, 45s) a layer of PMMA (950, A2) on the surface of the above-mentioned transistor, dry it at 170° C. for 2 minutes. Using an electron beam etching method, the DesignCAD file is run on a computer to etch the pat...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Concentration | aaaaa | aaaaa |

| Width | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More