High-capacity BCD technique for twice etching single/poly-silicon

A single-layer polysilicon, high-power technology, which is applied in the field of electronics, can solve the problem that the gate oxide is easily damaged, and achieve the effects of easy process implementation, avoiding the penetration of gate oxide into the channel region, and stable device performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0057] Specific examples of the present invention will be described below in conjunction with specific device structure diagrams.

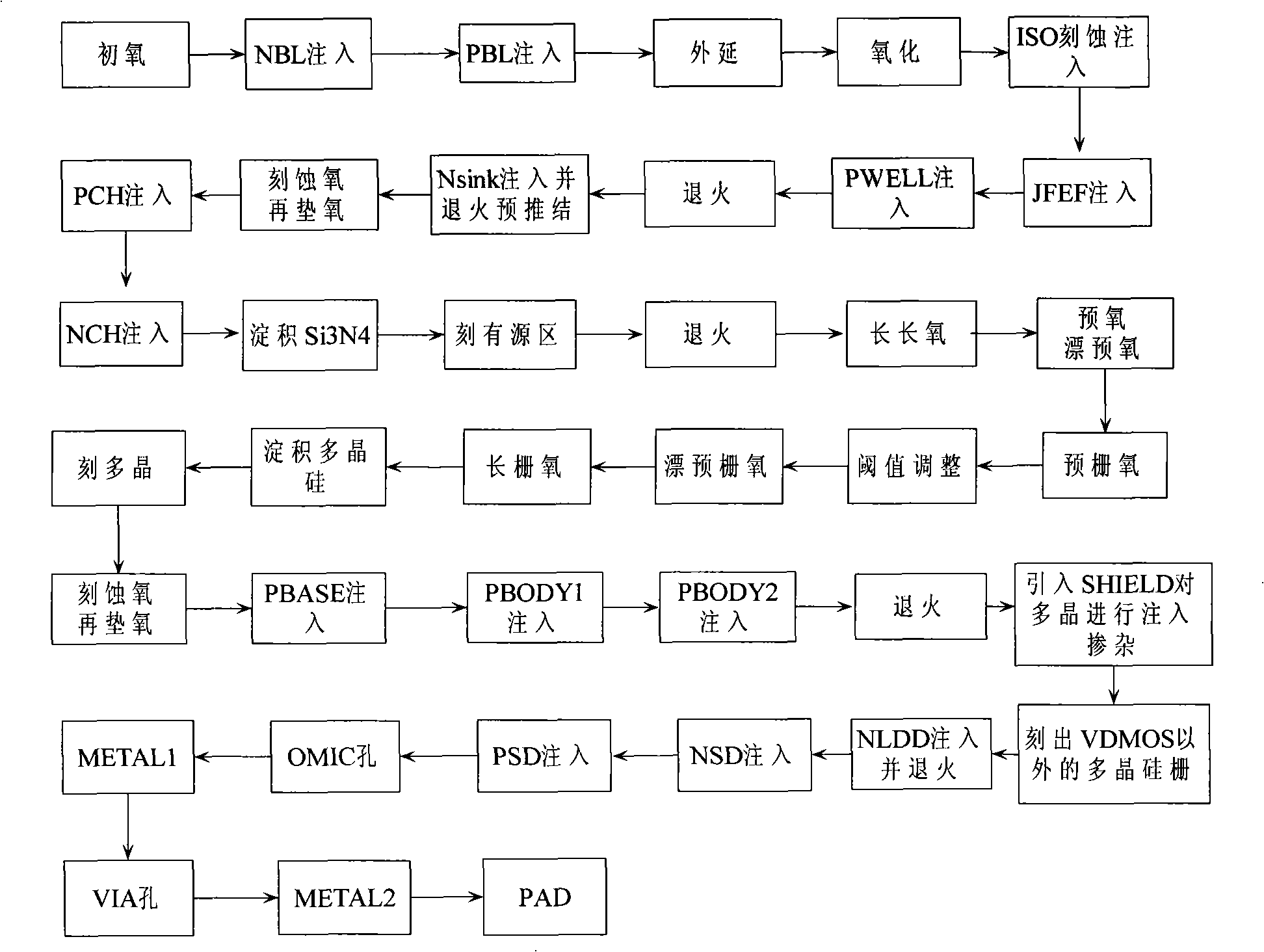

[0058] figure 1 It is a concrete process flow diagram of the present invention, with reference to Figure 14 , this process can integrate high-voltage VDMOS, high-voltage PMOS, high-voltage NPN, high-voltage PNP, low-voltage NPN, substrate PNP, lateral PNP, low-voltage NMOS, low-voltage PMOS, low-voltage diodes, high-voltage diodes, Zener diodes, and various capacitors and resistors Various devices. refer to figure 1 , the specific process examples of the present invention include the following specific process steps.

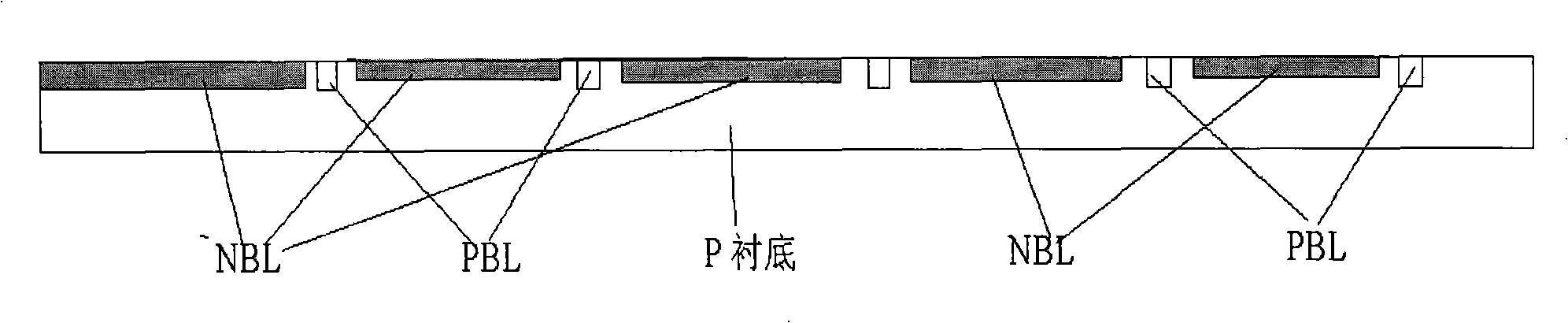

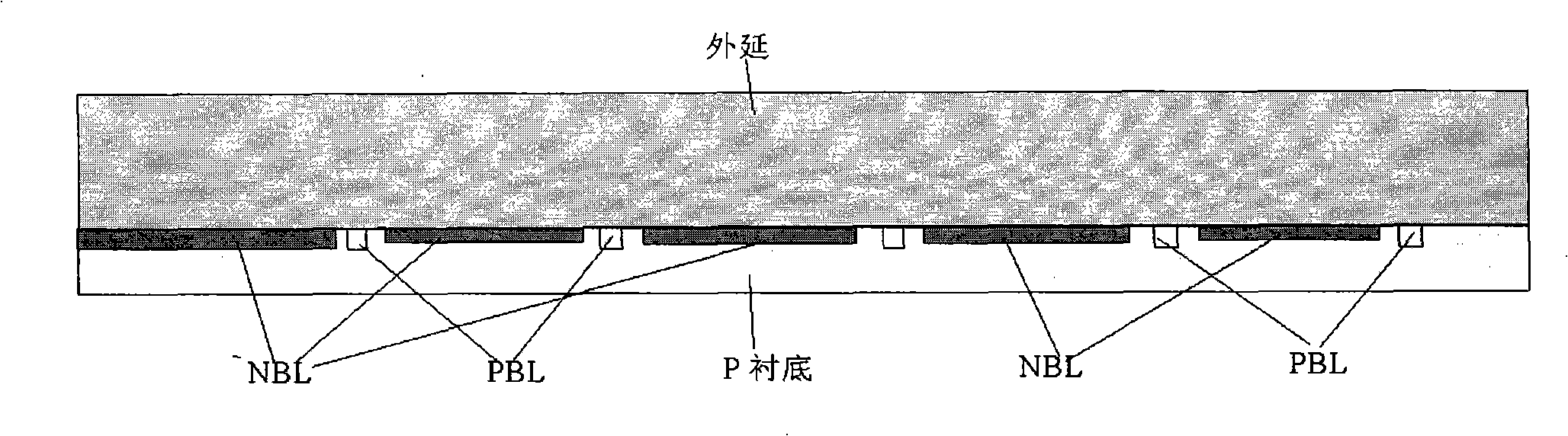

[0059] 1. Select the required substrate, here we choose the substrate with P-type crystal plane, and make alignment marks. The specific process steps include: initial oxygen formation of an oxide layer of about 1 μm; use photoresist to locate the buried layer region NBL, and then etch the oxide layer; grow a layer of particle-...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More