Silicon device on insulator and preparation method thereof

A technology of silicon-on-insulator and devices, applied in the field of silicon-on-insulator devices and their preparation, can solve the problems of inability to effectively suppress the floating body effect, deterioration of device performance, reduction of channel width, etc., and to improve the resistance to single particle and transient The ability to irradiate, the effect of reducing power consumption, increasing speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

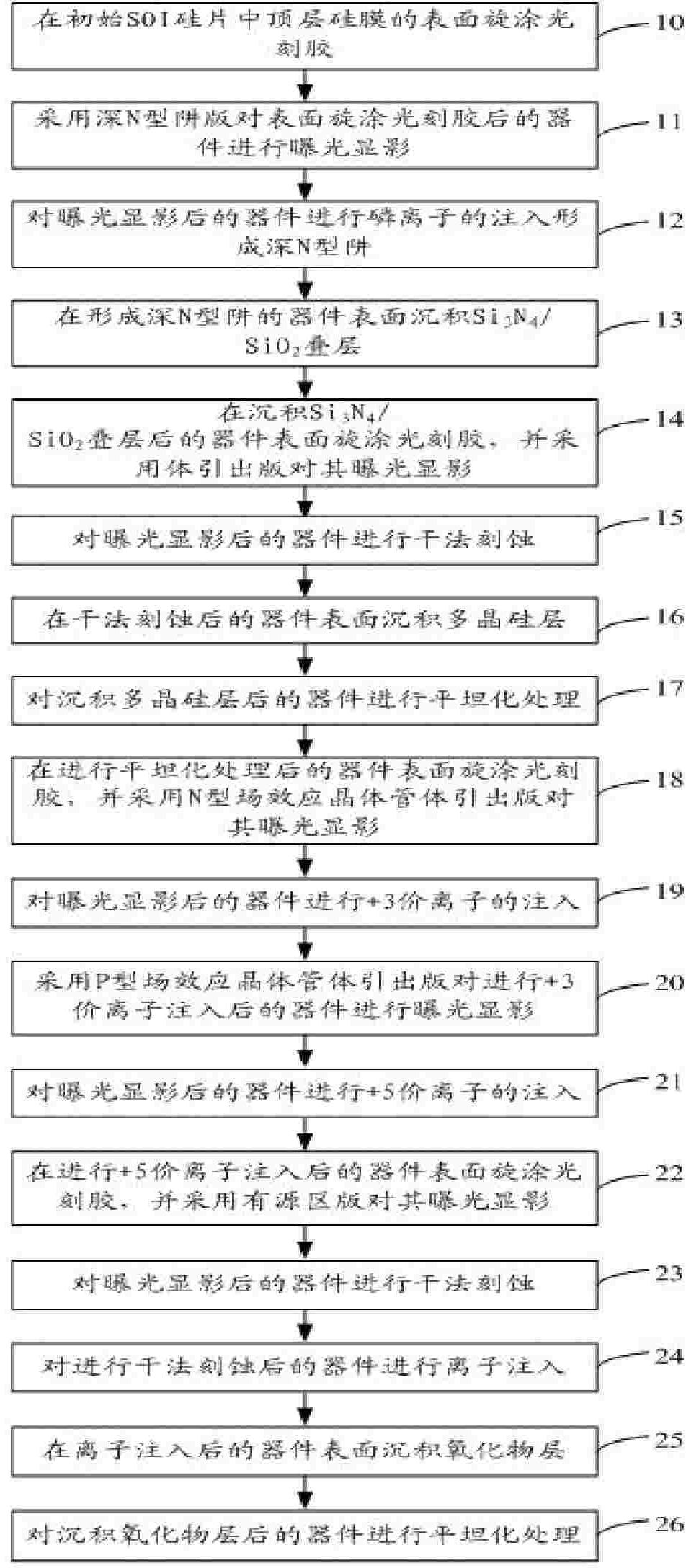

[0052] figure 1 It is a flow chart of a method for preparing a silicon-on-insulator device using shallow trench isolation technology in Embodiment 1 of the present invention. like figure 1 As shown, the silicon-on-insulator device is fabricated by shallow trench isolation (STI isolation technology). The STI isolation technology can provide electrical isolation for different CMOS devices. Although this embodiment adopts the STI isolation technology to form the silicon-on-insulator device, the formation of the silicon-on-insulator device does not depend on the STI isolation technology. According to this embodiment, local silicon oxidation isolation (LOCOS isolation) can also be used. The silicon-on-insulator device is prepared using the MESA isolation technology or mesa isolation technology. The method for preparing the silicon-on-insulator device by adopting shallow trench isolation technology includes the following steps:

[0053] Step 10: Spin-coat photoresist 100 on the ...

Embodiment 2

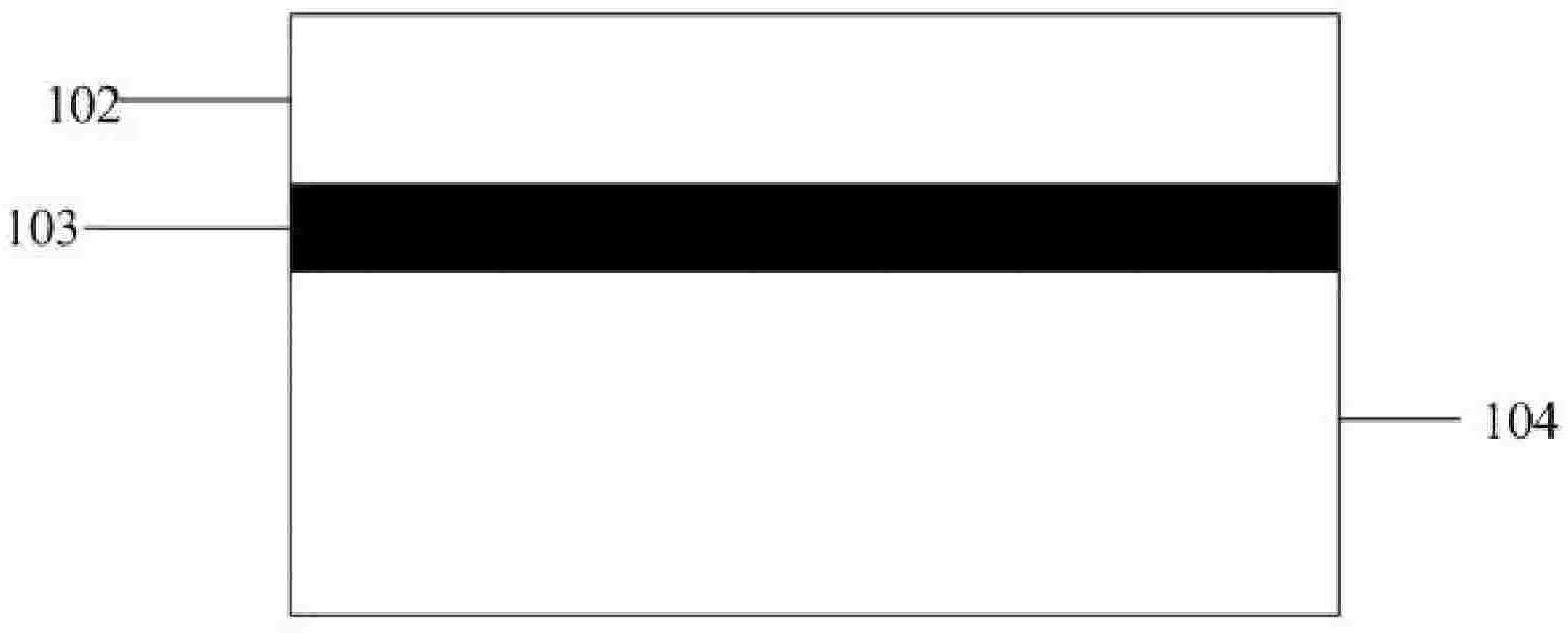

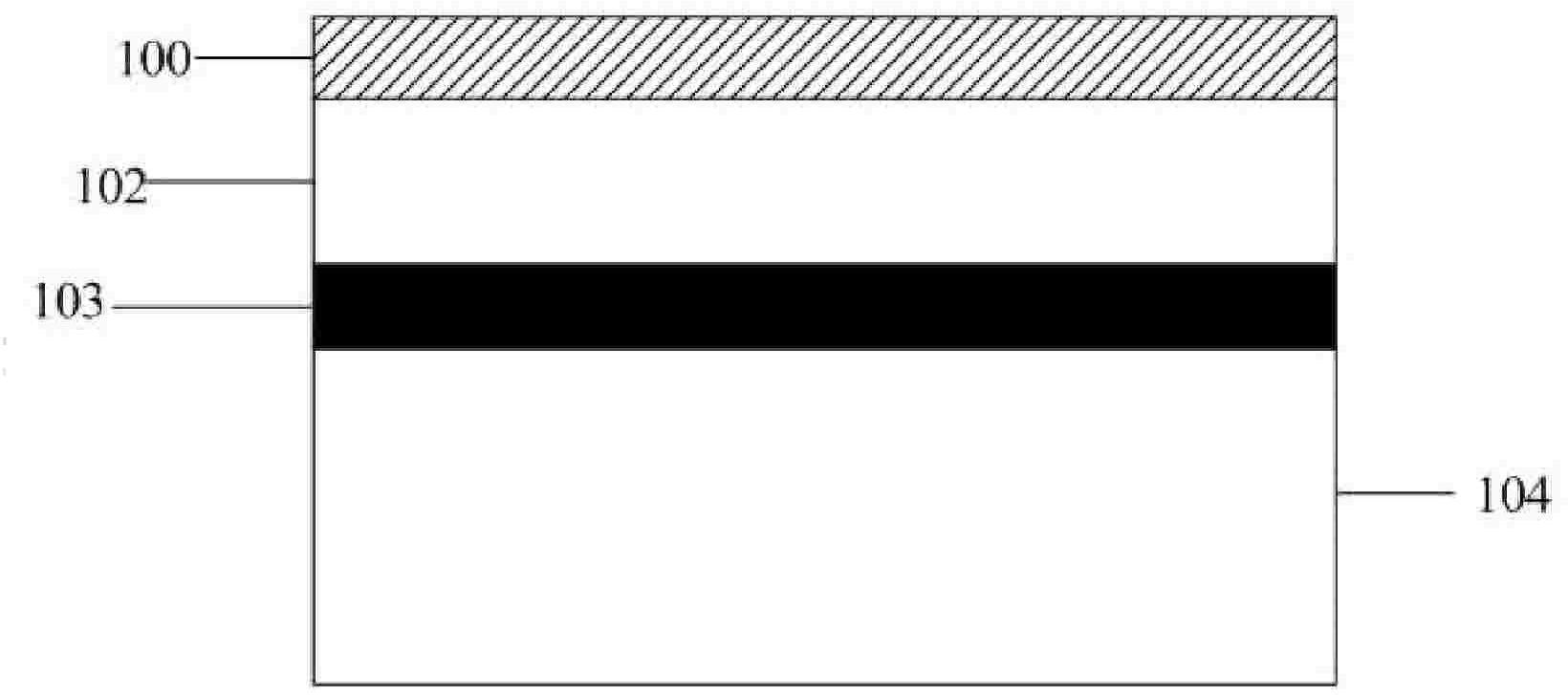

[0089] Figure 24 It is a schematic diagram of the basic structure of a silicon-on-insulator device fabricated by shallow trench isolation technology in Example 2 of the present invention. like Figure 24 As shown, the figure is also Figure 20 Schematic diagram of the structure along the X-X' direction. The SOI device includes a bottom silicon substrate 104 , a buried oxide layer 103 , and an N-type field effect transistor 66 and a P-type field effect transistor 68 formed in the top layer silicon film 102 . The N-type field effect transistor 66 is located in the body region 608 , which includes a drain 96 , a source 500 , a gate 92 and a body lead-out portion 56 , and the body lead-out portion 56 is polysilicon doped with boron ions. The P-type field effect transistor 68 is located in the body region 610 , which includes a drain 98 , a source 550 , a gate 92 and a body lead-out portion 58 , the body lead-out portion 58 is polysilicon doped with phosphorus ions. The body r...

Embodiment 3

[0091] Figure 25 It is a schematic diagram of the basic structure of a silicon-on-insulator device fabricated by shallow trench isolation technology in Example 3 of the present invention. like Figure 25 shown in Figure 24 Based on this, two N-type field effect transistors can share the body lead-out portion 56 of one N-type field effect transistor, thereby reducing the area of the chip.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More