Method for manufacturing silicon-on-insulator (SOI) complementary metal oxide semiconductor (CMOS) device with vertical gate structure

A fabrication method, vertical gate technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0042] 1. Use STI technology to perform oxide isolation on the PMOS region and the NMOS region.

[0043] 2. A window is etched between the PMOS area and the NMOS area, and other parts are protected with photoresist, and the sidewall is oxidized by thermal oxidation to form the gate oxide layer of PMOS and NMOS, and then polysilicon is deposited at the window, Fill, dope, chemical mechanical polish CMP.

[0044] 3. The channels of NMOS and PMOS are doped by multiple ion implantation. After doping, rapid annealing is performed. The vertical depth can be adjusted by adjusting the implantation energy and dose. After the doping is completed, the profile impurities should be evenly distributed, and the impurity distribution at the edge is clear and steep.

[0045] 4. The source region and the drain region of NMOS and PMOS are heavily doped by ion implantation, and rapid annealing is performed after doping.

[0046] 5. After etching windows for the channel, source region, drain reg...

Embodiment 2

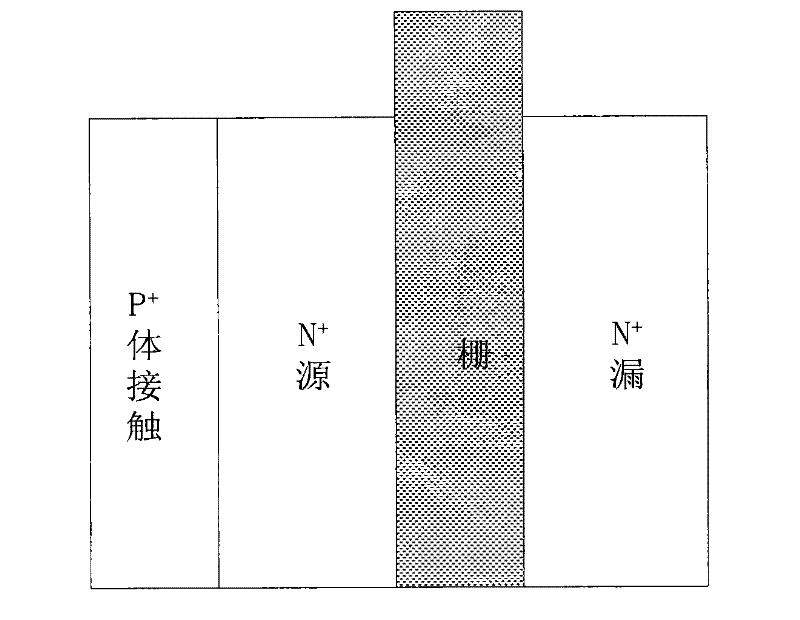

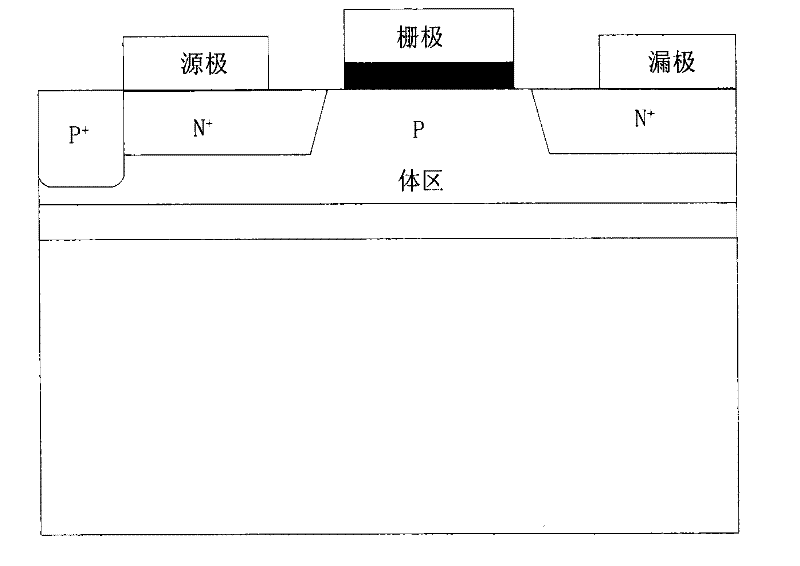

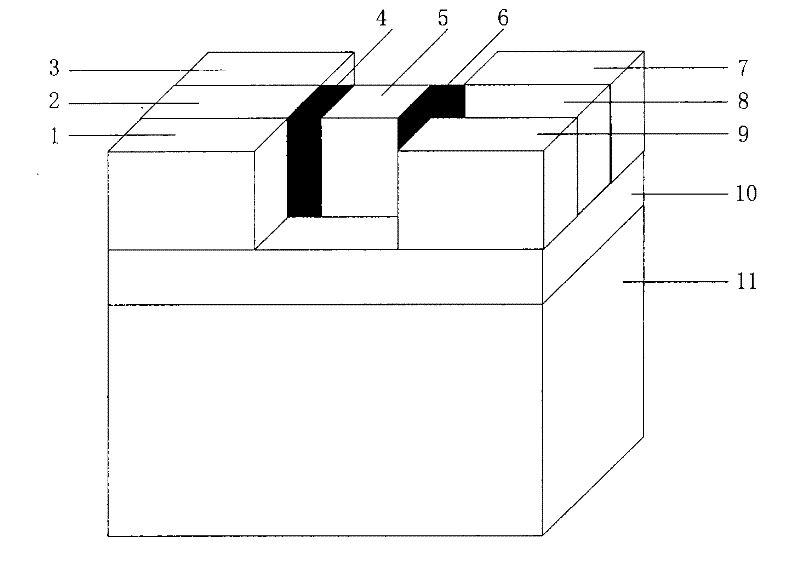

[0058] The SOI substrate includes a silicon substrate layer 11 grown from bottom to top, a buried oxide layer 10, and a single crystal silicon top layer. Both the NMOS gate oxide layer 4 and the PMOS gate oxide layer 6 extend down to the buried oxide layer 10; the vertical gate region 5, the NMOS region, the PMOS region and the silicon substrate layer 11 are separated by the buried oxide layer 10 . The NMOS region includes an NMOS source region 1, an NMOS drain region 3, and an NMOS channel 2. The NMOS source region 1 leads to an NMOS source 16, the NMOS drain region 3 leads to an NMOS drain 14, and the NMOS channel 2 leads to an NMOS body electrode 12. The PMOS region includes a PMOS source region 9, a PMOS drain region 7, and a PMOS channel 8. The PMOS source region 9 leads to a PMOS source 17, the PMOS drain region 7 leads to a PMOS drain 15, and the PMOS channel 8 leads to a PMOS body. electrode 13. A gate 18 leads out from the vertical gate region 5 . The vertical gat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More