Circuit device three-dimensional integrative method

A technology of circuit devices and three-dimensional integration, applied in chemical instruments and methods, circuits, electrical components, etc., can solve the problems of three-dimensional interconnection aspect ratio limitation, blind holes are sealed, etc., achieve high aspect ratio, avoid holes and Gap, the effect of high three-dimensional integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

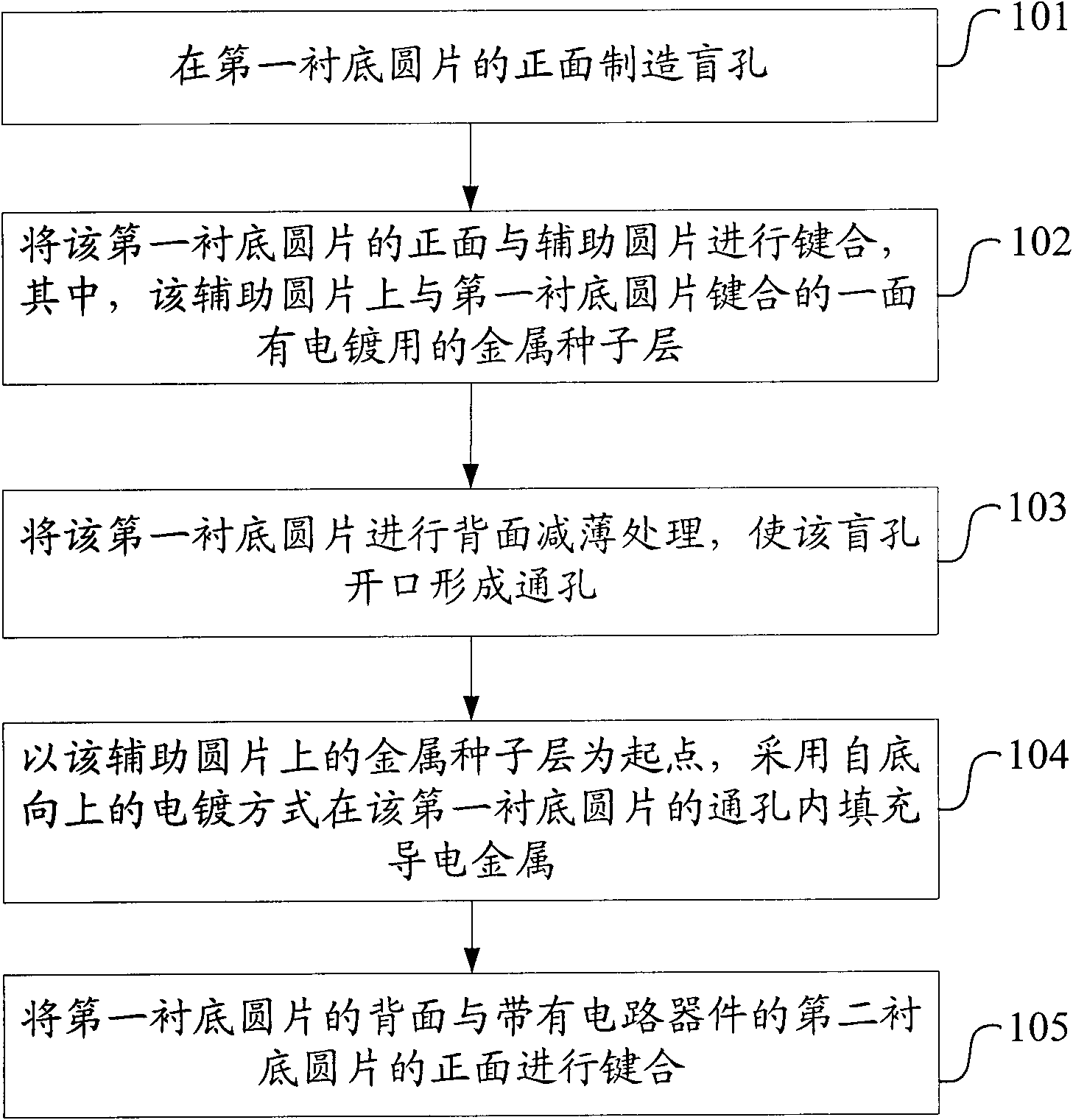

Embodiment 1

[0030] The embodiment of the present invention provides a method for three-dimensional interconnection of circuit devices, which can perform three-dimensional vertical interconnection of substrate wafers of circuit devices with high density and high aspect ratio, effectively realizing three-dimensional interconnection of circuit devices and 3D integration.

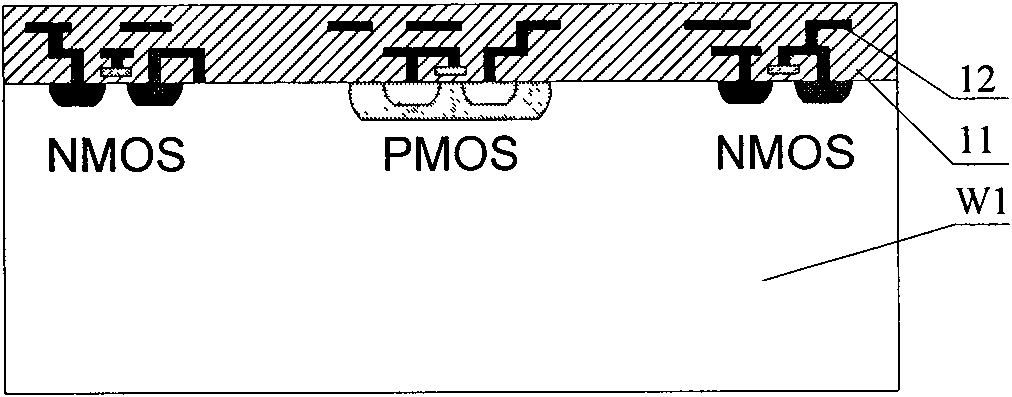

[0031] In this embodiment, the implementation of three-dimensional interconnection of substrate wafers of two-layer circuit devices is taken as an example for illustration. figure 1 Shown is the substrate wafer W1 used in this embodiment, which includes fabricated circuit devices, such as integrated circuits, MEMS devices, or microsensors; the substrate wafer W1 also includes : multilayer metal interconnection 12, and the interlayer dielectric layer or surface passivation layer 11 of the metal interconnection 12. Wherein, the material of the substrate wafer may be silicon, strained silicon, silicon germanium, gallium arse...

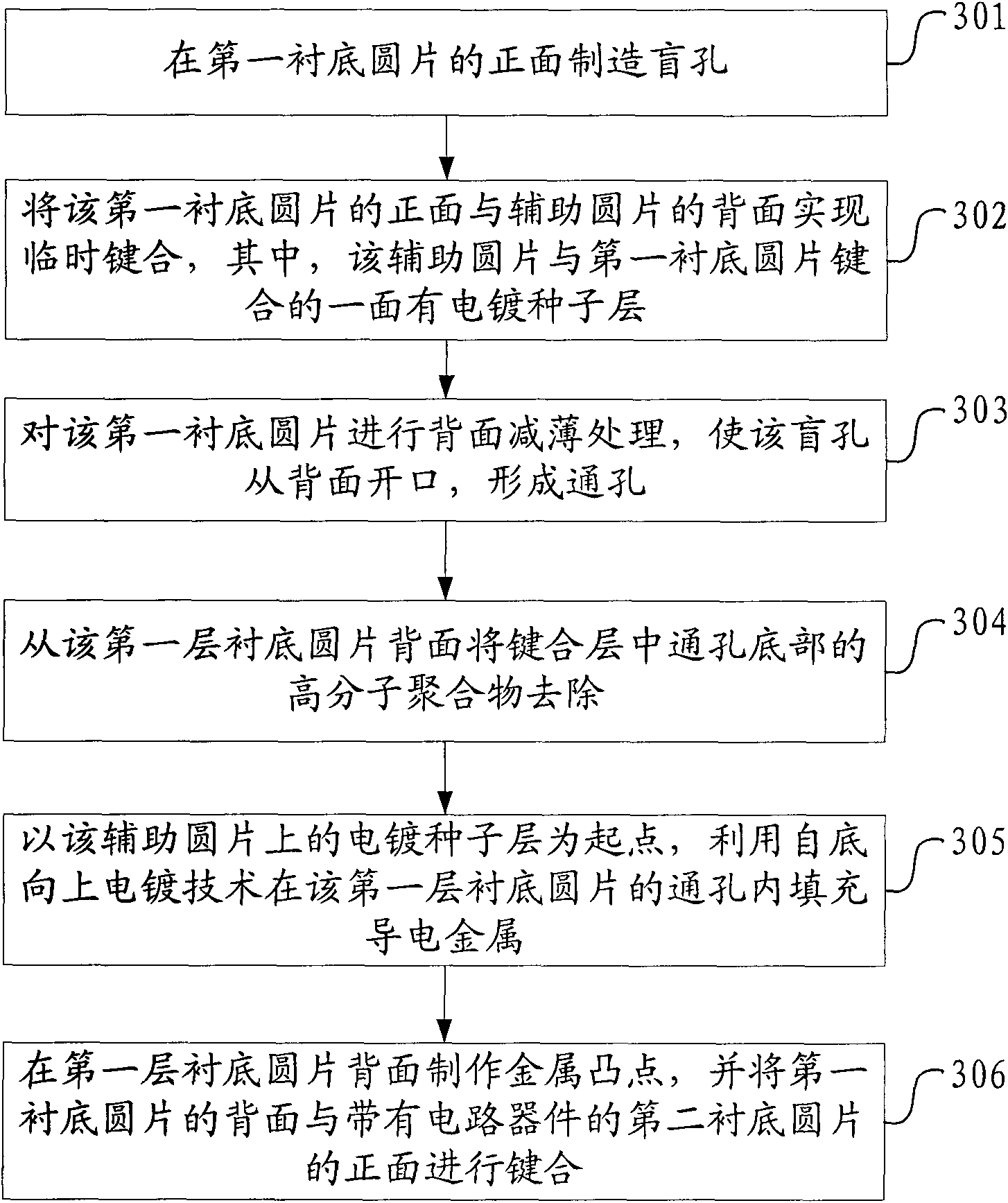

Embodiment 2

[0045] The embodiment of the present invention provides a method for three-dimensional integration of circuit devices, which can perform three-dimensional vertical interconnection of substrate wafers of circuit devices with high density and high aspect ratio, effectively realizing three-dimensional integration and three-dimensional integration of circuit devices. interconnection.

[0046] In this embodiment, the implementation of three-dimensional interconnection of substrate wafers of two-layer circuit devices is taken as an example for illustration. figure 1 Shown is the substrate wafer W1 used in this embodiment, which includes fabricated circuit devices, such as integrated circuits, MEMS devices, or microsensors; the substrate wafer W1 also includes : multilayer metal interconnection 12, and the interlayer dielectric layer or surface passivation layer 11 of the metal interconnection 12. Wherein, the material of the substrate wafer W1 may be silicon, strained silicon, sili...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More