Composite plane terminal passivating method for controllable silicon device

A composite planar and silicon device technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problem that the gate trigger current is difficult to guarantee the off-state repetitive peak voltage, the mesa process terminal passivation process is cumbersome, and the mesa process Problems such as poor parameter consistency, to achieve the effect of shortening the production cycle, small proportion, and shortening the production process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0047] The planar terminal passivation method of the thyristor device involved in the present invention is to use a composite film generated by chemical vapor deposition as the terminal passivation structure of the thyristor device, and the method includes the following process:

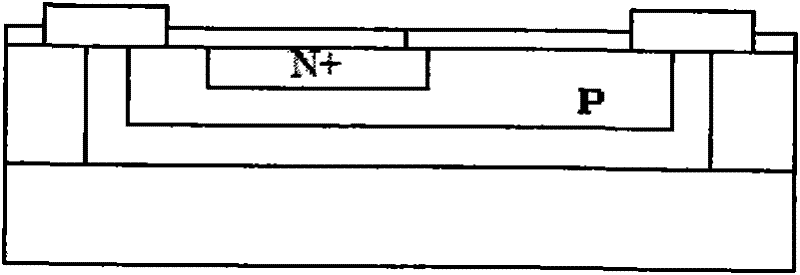

[0048] Step 1, at a certain temperature (1150~1250 ℃), time (the specific time is determined by I GT set) and atmosphere (N 2 : 10L / min, O 2 : 1L / min), the phosphorus atoms are pushed into the silicon chip to a certain depth to form the cathode area, and the oxidation diffusion of the cathode area of the chip is completed, such as Figure 6 shown.

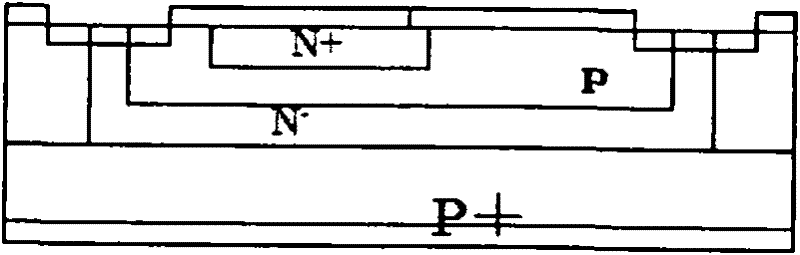

[0049] Step 2. The silicon wafer that has been oxidized and diffused in the cathode area of the chip is completely peeled off by using a silicon dioxide etching solution to form a silicon substrate layer of the chip, such as Figure 7 shown.

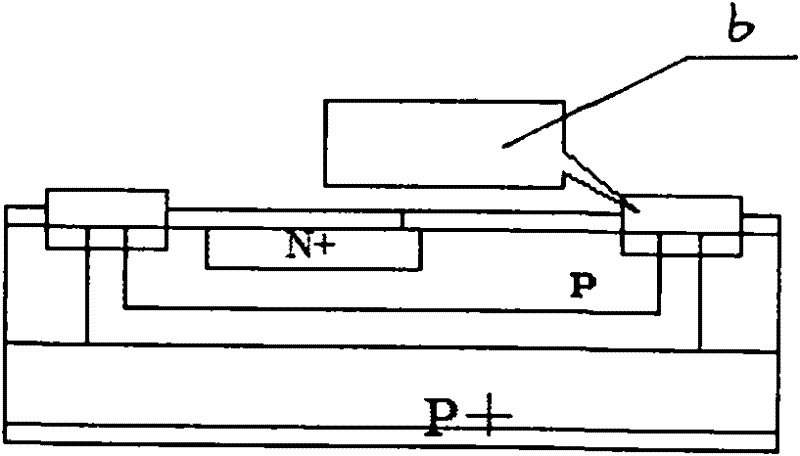

[0050] Step 3, adopt the method of chemical vapor deposition (600-700 ℃, 20-60pa lower N 2 O and SiH 4 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More