Method for packaging multi-laminated multi-chip on flexible circuit board and packaging chipset

A flexible circuit substrate, multi-chip packaging technology, applied in the direction of circuits, electrical components, electrical solid devices, etc., can solve the problems of mutual interference of signals, the inability of the size chip packaging to meet the requirements, and the incompatibility between the packaging position and the installation point.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

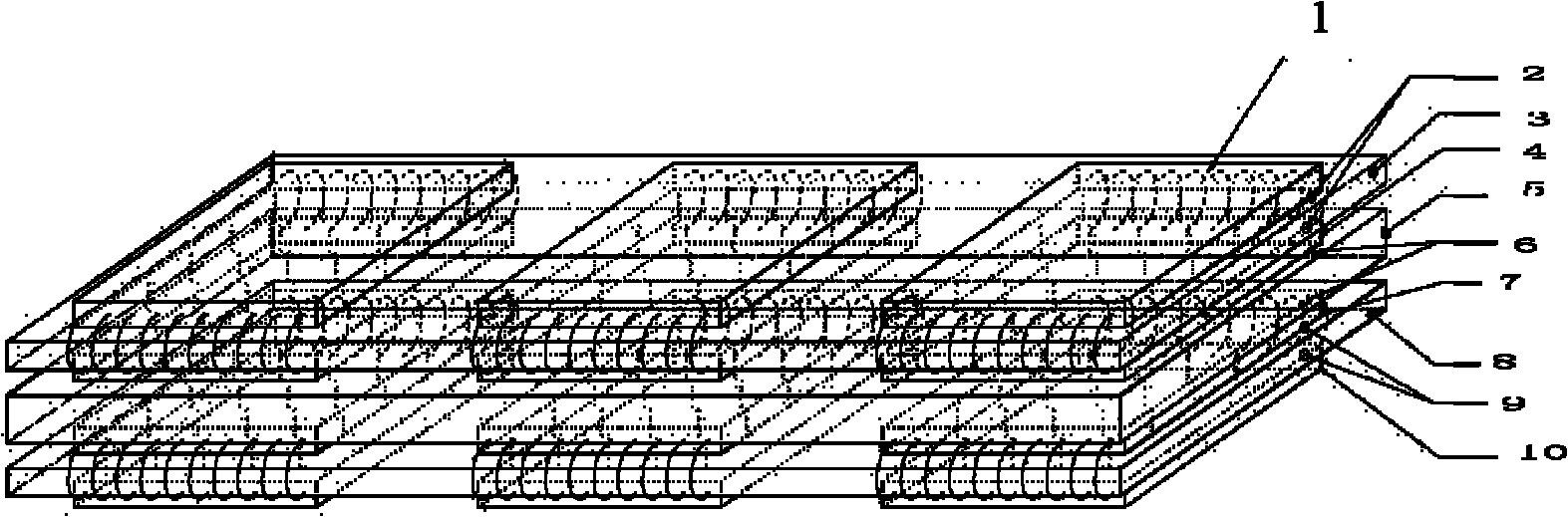

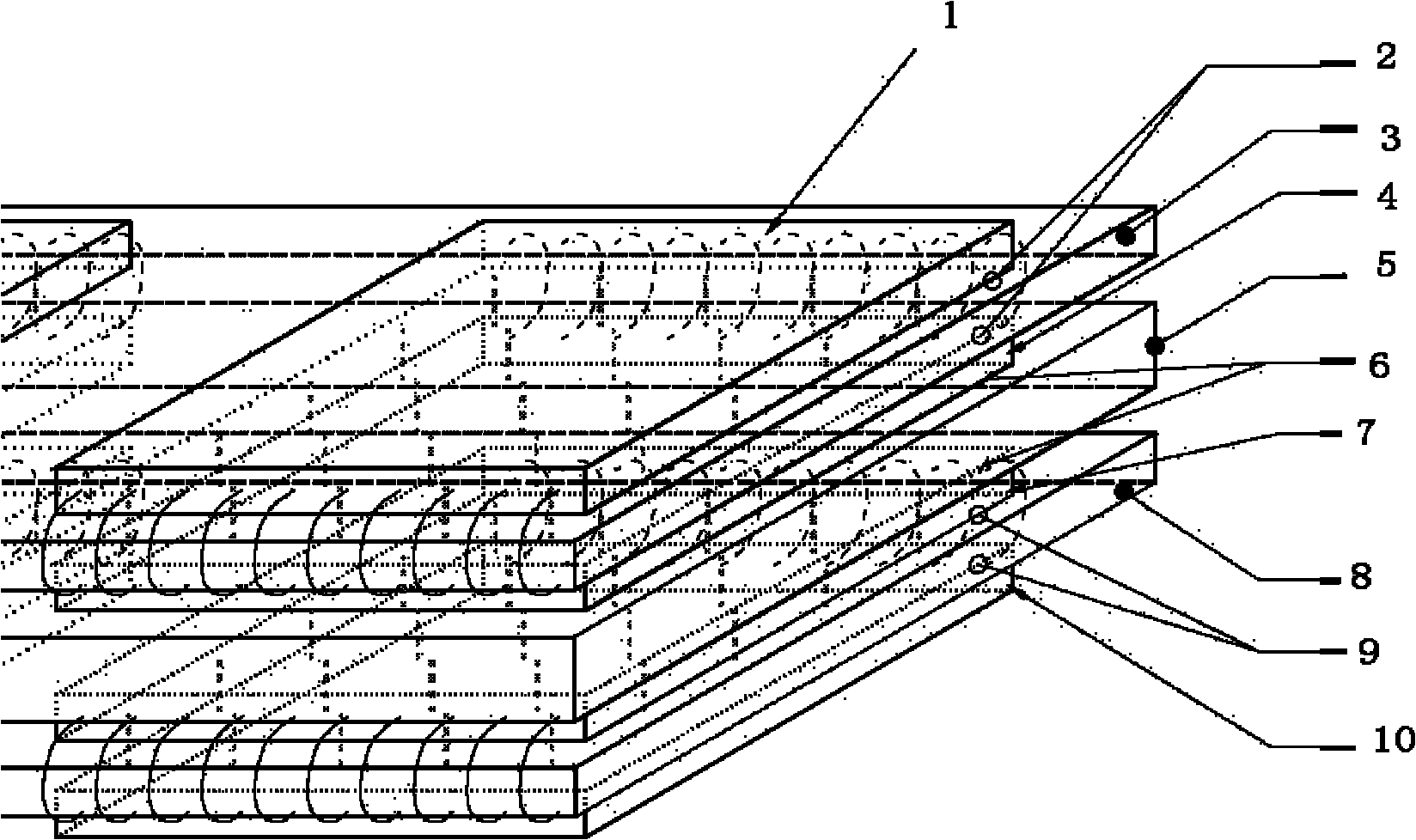

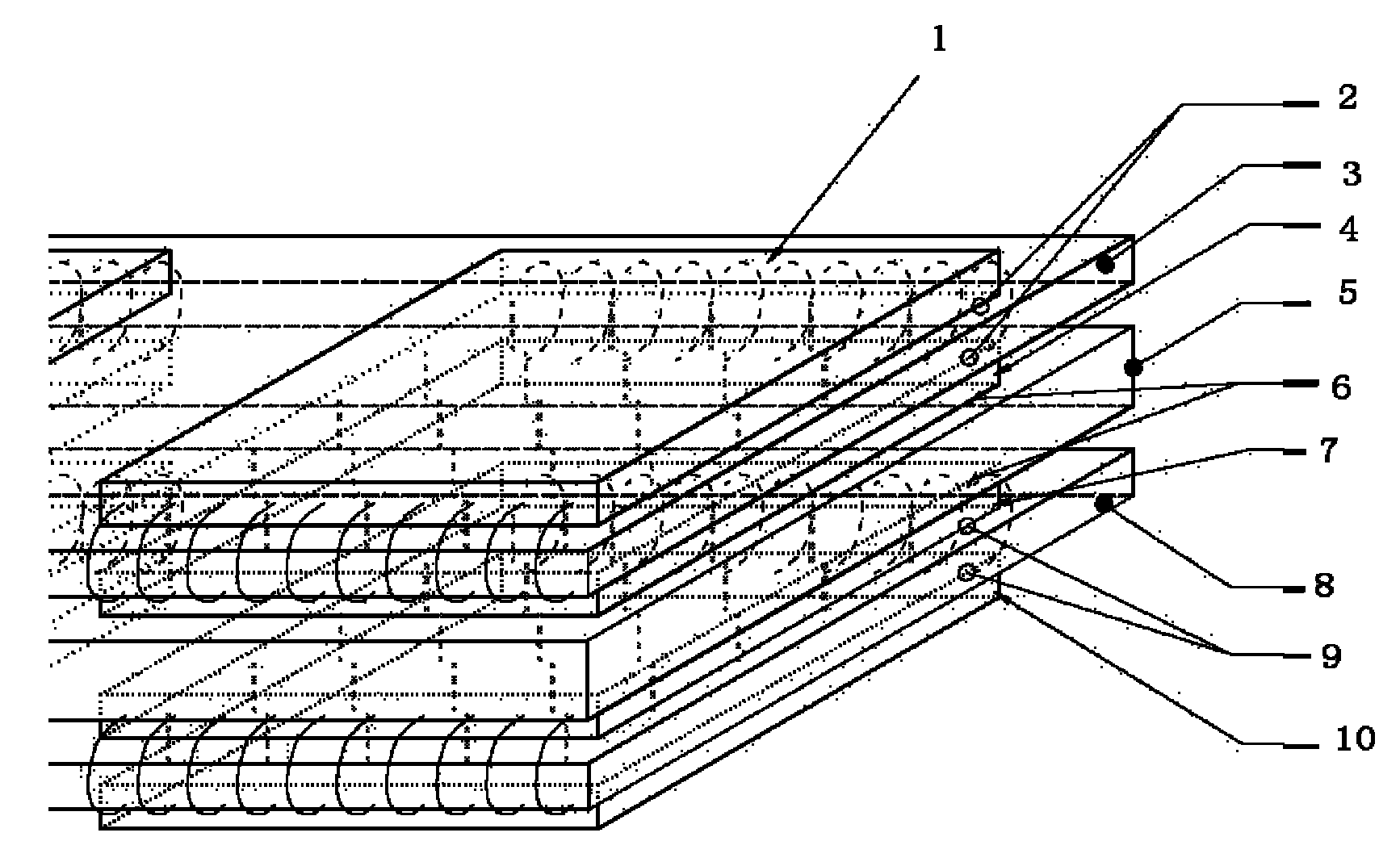

[0011] In the embodiment of the present invention, the method for integrating multi-layer multi-chip packaging on a multi-layer packaging circuit substrate and the package made by this method, the line distance and line width of the packaging circuit substrate are less than 20 microns, and a logic chip is stacked On top of the other, form the middle layer (core part) two identical chips stacked, and the upper layer (top) stack one large-capacity memory chip on top of the other to form the top two chips stacked on the core part chip, so that the upper layer and The middle layer is connected to the same symmetrical position with flexible circuit terminals. Four packaged chips are stacked to form a package for conductive connection to form a stacked layer. The four chips are packaged on a flexible circuit substrate with a total thickness of less than 1.20mm, realizing ball grid array packaging technology (FBGA) and Chip Scale Package (FCSP) package manufacturing.

[0012] In this...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More