Independent grid-controlled nano line field effect transistor

A technology of field effect transistors and nanowires, applied in semiconductor devices, electrical components, circuits, etc., to achieve the effect of reducing off-state current, reducing driving current, and strong driving ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0023] 3) Complete the preparation of the outer gate structure; implant phosphorus at a large angle (1x10 15 cm -2 / 10keV) and annealed (1000°C / 10s) to prepare source and drain regions;

[0024] 4) The standard CMOS process completes the metal electrode preparation.

Embodiment 1

[0026] Embodiment 1. Nanowire Field Effect Transistor Controlled by Independent Gate and Its Performance Testing

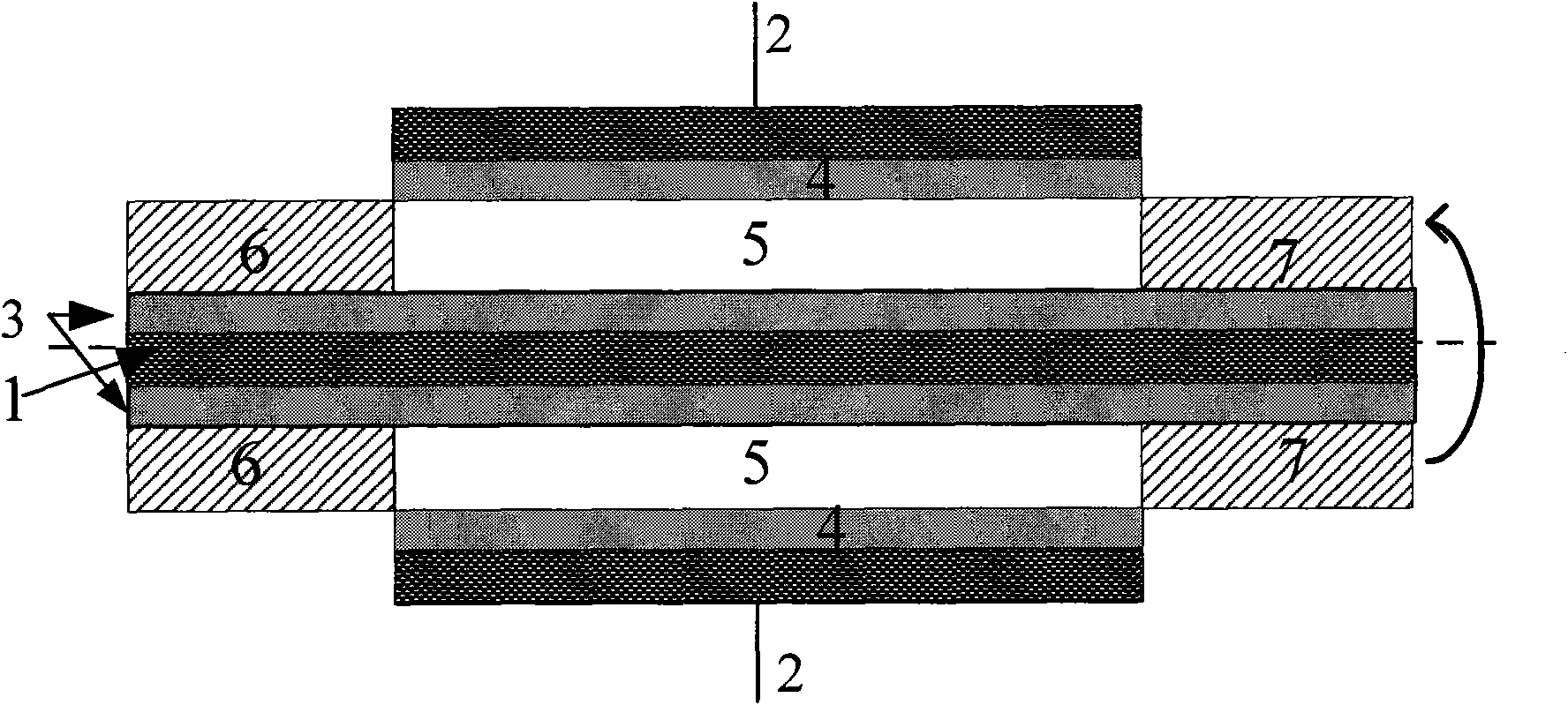

[0027] The structure of the independent gate controlled nanowire field effect transistor is as follows figure 1 As shown, wherein, the work function of the material of the inner gate electrode 1 and the outer gate electrode 2 is set to 4.61 electron volts; the inner gate dielectric 3 and the outer gate dielectric 4 are silicon oxide layers with a thickness of 1.5 nanometers, and the channel region 5 is boron-doped Concentration 1×10 11 cm -3 Silicon material with a thickness of 10 nanometers; the source region 6 and the drain region 7 are phosphorus doped with a concentration of 1×10 20 cm -3 silicon material; inner gate radius is 10 nanometers. The source and drain regions of the device are both 50 nm in length. The thickness of the source and drain regions is equal to the thickness of the channel region and surrounds the inner gate electrode.

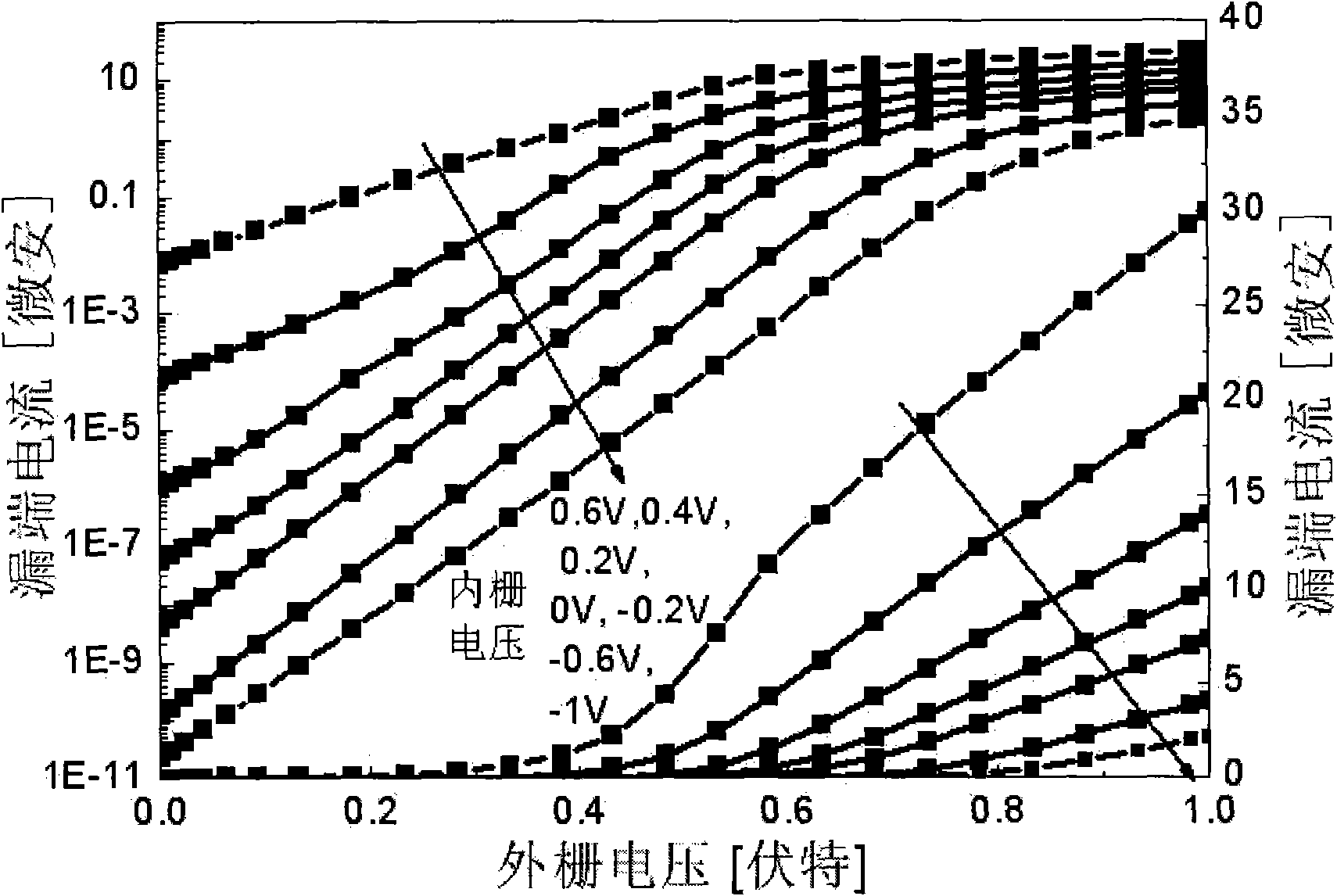

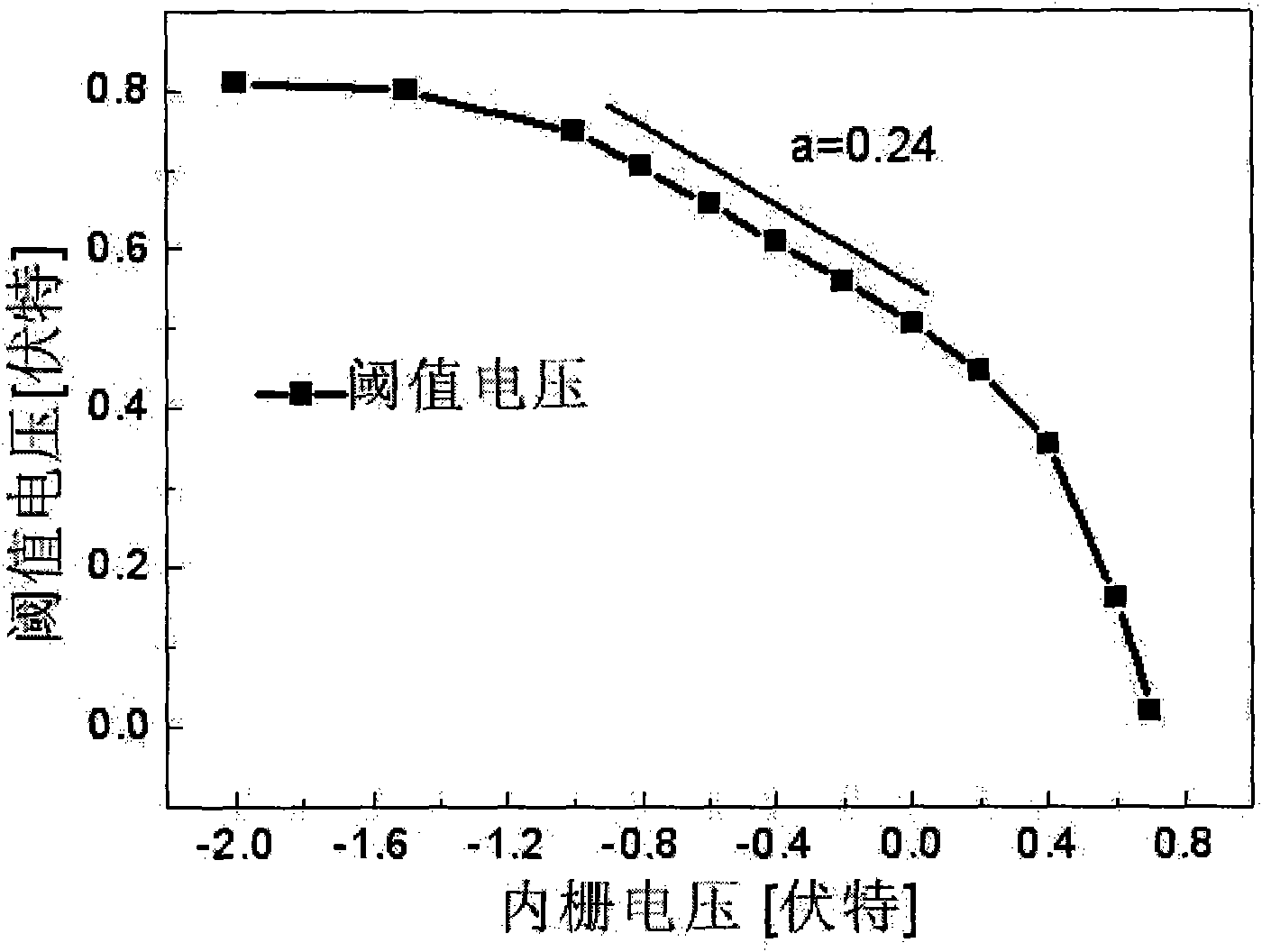

[0028] The ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Diameter | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More