Gallium nitride (GaN) enhancement type metal insulator semiconductor field effect transistor (MISFET) device and manufacturing method thereof

An enhanced, device technology, used in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of increasing device on-resistance, low current density, affecting device performance, etc., to increase device current density. , the effect of reducing gate leakage current and increasing threshold voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

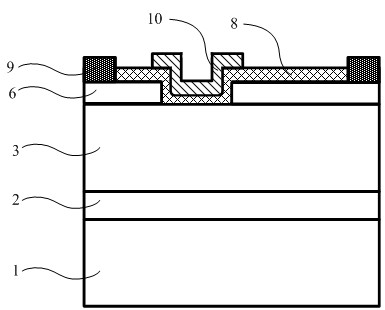

[0034] This example figure 1 A GaN enhanced MISFET device is given, which includes: a substrate 1, a stress buffer layer 2 and a GaN layer 3 grown on the substrate 1 by MOCVD or MBE, and a heterogeneous layer 6 selectively grown on the GaN layer 3 During selective growth, a heterogeneous layer structure is grown in the access region, and the gate is blocked by the mask layer 5, the gate region is deposited to form an insulating dielectric layer 8, and the source and drain access regions are vapor-deposited with ohmic contact metal 9, A gate metal 10 is vapor-deposited on the insulating dielectric layer in the gate region.

[0035] The thickness of the growing heterogeneous layer 6 needs to be controlled to not only form a sufficient two-dimensional electron gas concentration at the interface of the GaN layer, but also reduce the ohmic contact resistance of the source and drain and the on-resistance of the device. The thickness of the heterogeneous layer can be controlled with...

Embodiment 2

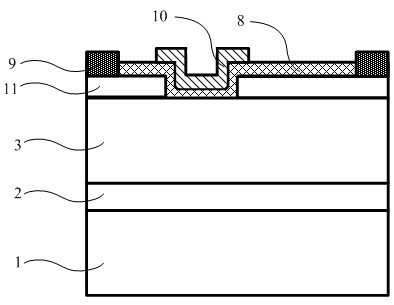

[0038] Such as figure 2 As shown, this embodiment provides a second structure of a GaN enhanced MISFET device, which is roughly the same as the device structure of Embodiment 1, the difference is that when the heterogeneous layer 11 is selectively grown, the N-type doped It further reduces the ohmic contact resistance of the source and drain regions and increases the current density of the device.

Embodiment 3

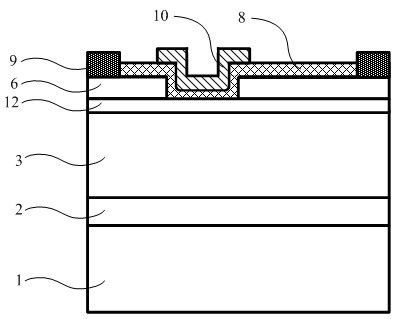

[0040] Such as image 3 As shown, this embodiment provides a third structure of a GaN enhanced MISFET device. In this embodiment, a 1nm-10nm AlN insertion layer 12 is grown on the surface of the GaN layer 3 in the conductive channel region, and the AlN The insertion layer 12 can effectively increase the concentration and mobility of the conductive channel 2DEG, and increase the on-current density of the device. The specific solution is that after the GaN layer 3 is grown on the substrate material, the AlN insertion layer 12 is grown, and the subsequent process is the same as that of the embodiment 1.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More