Organic thin film transistor using paper substrate and silk dielectric layer and manufacturing method thereof

A technology of organic thin film and production method, which is applied in the fields of electrical solid-state devices, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of pentacycline carrier mobility, poor matching, and expensive equipment, etc., and achieve effective Conducive to large-area production, improved transistor characteristics, simple and cheap process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

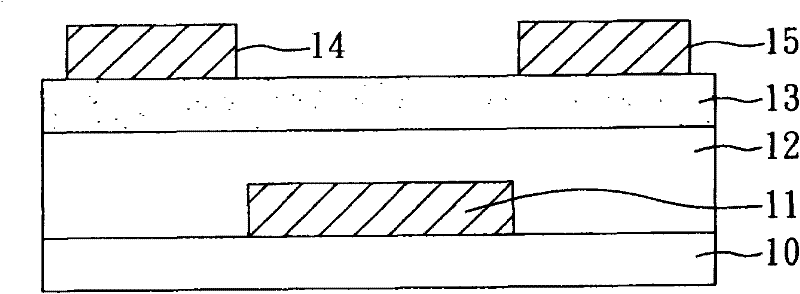

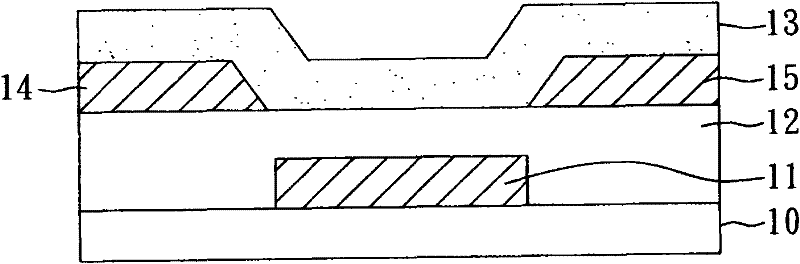

[0026] Example 1 - Top Contact Organic Thin Film Transistor Device

[0027] Preparation of silk aqueous solution

[0028] Firstly, prepare an aqueous solution containing 10wt% sodium carbonate, heat to boil, add dry natural silk, and boil for 30 minutes to remove sericin on the outer layer of silk. Then, put it into deionized water for washing to wash away the lye attached to the outer layer of silk. After drying, refined silk can be obtained, that is, fibroin.

[0029] Next, put the scoured silk into 20ml of 85wt% phosphoric acid solution, and stir until dissolved. Then, the phosphoric acid solution in which the silk was dissolved was placed in a dialysis membrane (Spectra / Por 3 dialysis membrane, molecular weight cutoff = 14000) and dialyzed for 3 days to remove the phosphoric acid solution. Finally, filter out impurities with filter paper to obtain an aqueous silk solution.

[0030] Fabrication of Top-Contact Organic Thin Film Transistor Devices

[0031] First, if Fi...

Embodiment 2 1

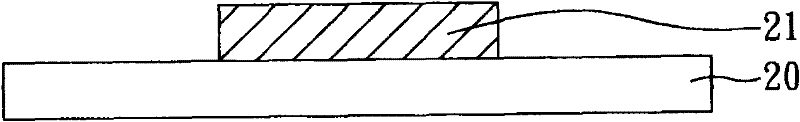

[0046] Embodiment 2 One contact type organic thin film transistor device

[0047] like Figure 5A As shown, a paper substrate 20 is provided, and a gate electrode 21 and a gate dielectric layer 22 are sequentially formed on the paper substrate 20 . In this embodiment, the materials and preparation methods of the paper substrate 20 , the grid 21 , and the gate dielectric layer 22 are the same as those in the first embodiment. In addition, in this embodiment, the thickness of the gate 21 is about 100 nm, and the thickness of the gate dielectric layer 22 is about 500 nm.

[0048] Next, if Figure 5B As shown, a patterned metal layer is vapor-deposited on the gate dielectric layer 22 to serve as the source 24 and the drain 25 by using the same process conditions as in the embodiment 1 for forming the gate. In this embodiment, the material of the source electrode 24 and the drain electrode 25 is gold, and its thickness is about 100 nm.

[0049] Finally, if Figure 5C As shown,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More